WM8778-EV1M

w Rev 1.1, February 2004

2

TABLE OF CONTENTS

INTRODUCTION ............................................................................................. 3

GETTING STARTED ....................................................................................... 3

EVALUATION KIT CHECKLIST ............................................................................. 3

CUSTOMER RE UIREMENTS..............................................................................3

EVALUATION BOARD OPERATION.............................................................. 4

POWER SUPPLIES ...............................................................................................4

BOARD FUNCTIONALITY ..................................................................................... 4

DIGITAL INPUT...................................................................................................... 5

ANALOGUE INPUT................................................................................................ 5

DIGITAL OUTPUT.................................................................................................. 5

ANALOGUE OUTPUT ............................................................................................ 5

INTERFACES......................................................................................................... 6

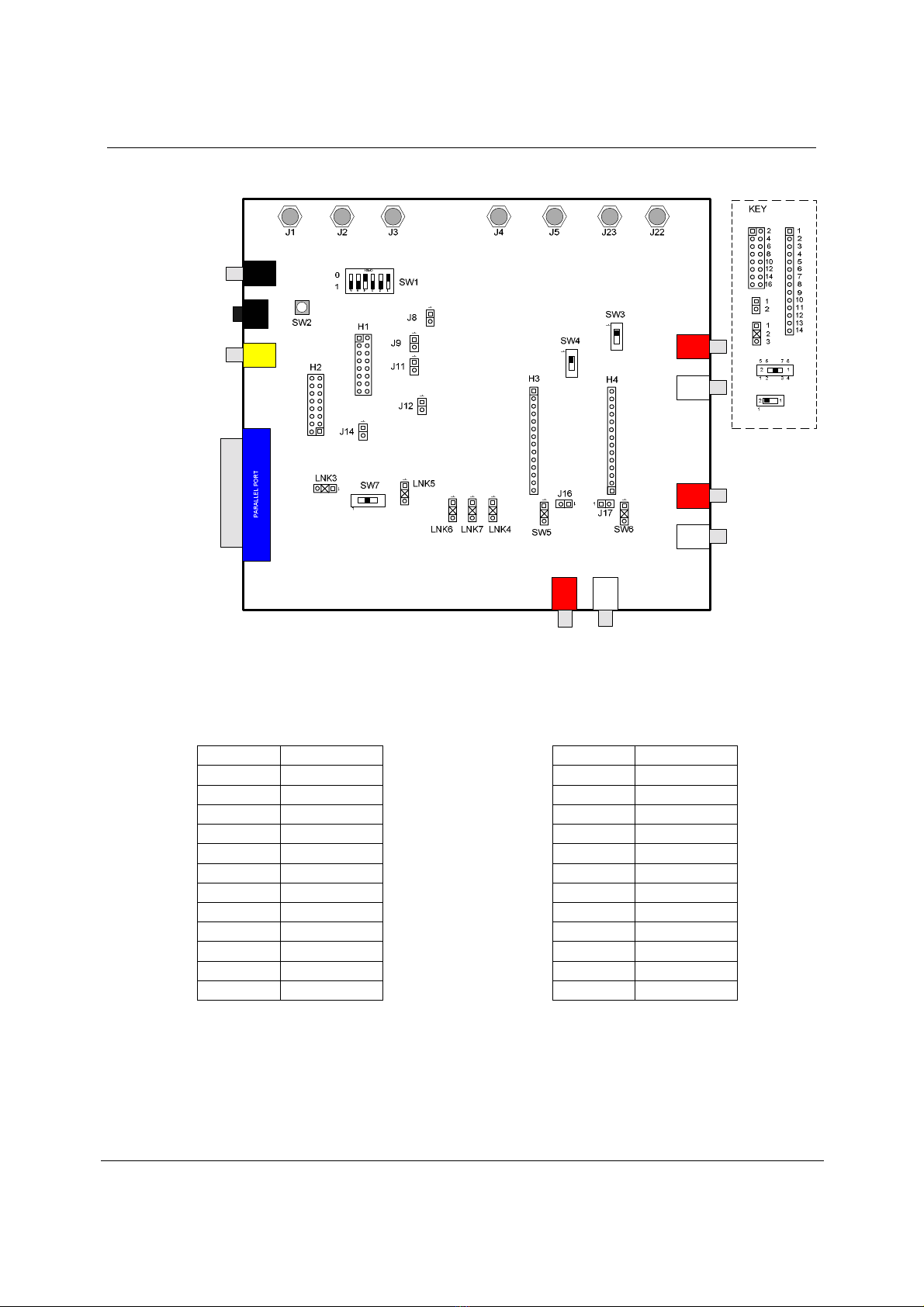

HEADERS .............................................................................................................. 6

JUMPERS .............................................................................................................. 7

SWITCHES ............................................................................................................ 8

LINKS..................................................................................................................... 8

HARDWARE CONTROL ................................................................................. 9

SOFTWARE CONTROL................................................................................ 11

SPI INTERFACE MODE....................................................................................... 11

TWO-WIRE MODE............................................................................................... 11

REGISTER MAP .................................................................................................. 12

SERIAL INTERFACE SOFTWARE DESCRIPTION...................................... 13

SOFTWARE DOWNLOAD................................................................................... 13

SOFTWARE INSTALLATION............................................................................... 13

SOFTWARE OPERATION ................................................................................... 14

DAC SETUP......................................................................................................... 19

ADC SETUP......................................................................................................... 21

LINE SETUP ........................................................................................................ 23

SCHEMATIC LAYOUT .................................................................................. 2

WM8778-EV1B PCB LAYOUT...................................................................... 33

WM8778-EV1B BILL OF MATERIAL............................................................ 37

APPENDIX .................................................................................................... 39

DAC AND ADC ALTERNATIVE AUDIO INTERFACE CONFIGURATION............ 39

EXTERNAL DSP CONNECTION TO THE WM8778-EV1B.................................. 41

ADDITIONAL WM8778-EV1B SETUP RECOMMENDATIONS ............................ 45

EVALUATION SUPPORT ............................................................................. 47

IMPORTANT NOTICE ................................................................................... 48