wWM8580

Multichannel CODEC with S/PDIF Transceiver

WOLFSON MICROELECTRONICS plc

To receive regular email updates, sign up at http://www.wolfsonmicro.com/enews/

Production Data, March 2009, Rev 4.7

Copyright ©2009 Wolfson Microelectronics plc

DESCRIPTION

The WM8580 is a multi-channel audio CODEC with S/PDIF

transceiver. The WM8580 is ideal for DVD and surround

sound processing applications for home hi-fi, automotive

and other audiovisual equipment.

Integrated into the device is a stereo 24-bit multi-bit sigma

delta ADC with support for digital audio output word lengths

from 16-bit to 32-bit, and sampling rates from 8kHz to

192kHz.

Also included are three stereo 24-bit multi-bit sigma delta

DACs, each with a dedicated oversampling digital

interpolation filter. Digital audio input word lengths from 16-

bits to 32-bits and sampling rates from 8kHz to 192kHz are

supported. Each DAC channel has independent digital

volume and mute control.

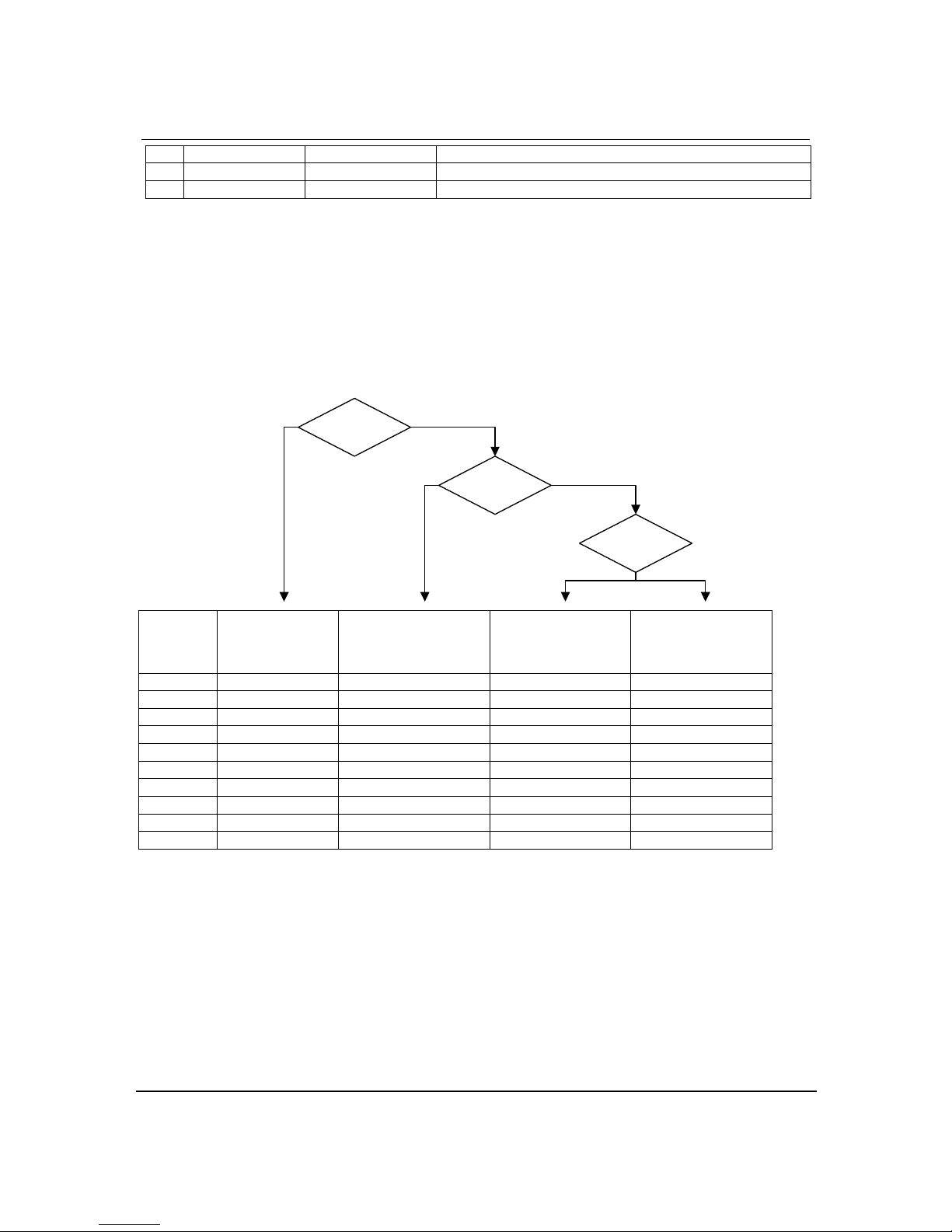

Two independent audio data interfaces support I2S, Left

Justified, Right Justified and DSP digital audio formats.

Each audio interface can operate in either Master Mode or

Slave Mode.

The S/PDIF transceiver is IEC-60958-3 compatible and

supports frame rates from 32k/s to 96k/s. It has four

multiplexed inputs and one output. Status and error

monitoring is built-in and results can reported over the serial

interface or via GPO pins. S/PDIF Channel Block

configuration is also supported.

The device has two PLLs that can be configured

independently to generate two system clocks for internal or

external use.

Device control and setup is via a 2-wire or 3-wire (SPI

compatible) serial interface. The serial interface provides

access to all features including channel selection, volume

controls, mutes, de-emphasis, S/PDIF control/status, and

power management facilities. Alternatively, the device has a

Hardware Control Mode where device features can be

enabled/disabled using selected pins.

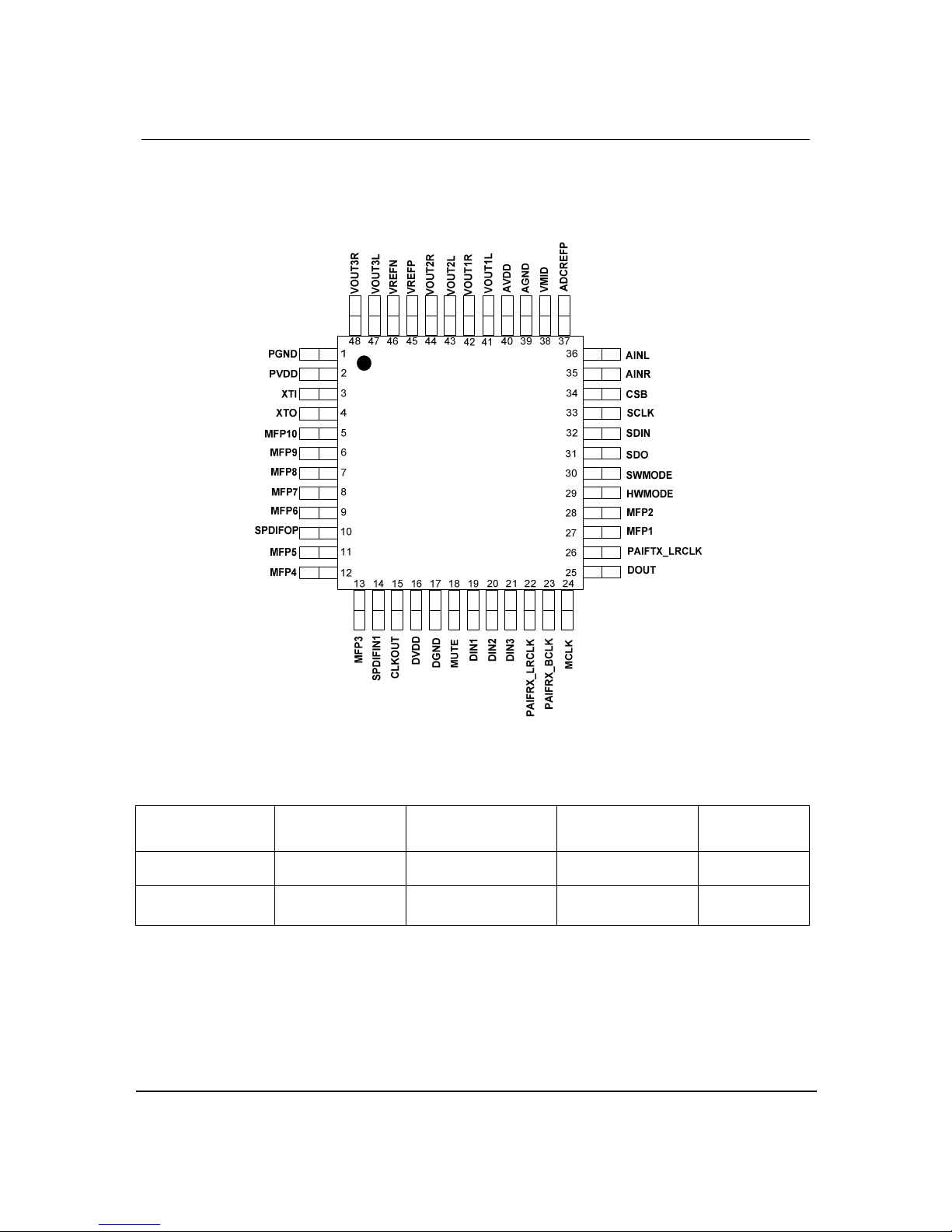

The device is available in a 48-lead TQFP package.

FEATURES

•Multi-channel CODEC with 3 Stereo DACs and 1 Stereo

ADC

•Integrated S/PDIF / IEC-60958-3 transceiver

•Audio Performance

−103dB SNR (‘A’ weighted @ 48kHz) DAC

−-90dB THD (48kHz) DAC

−100dB SNR (‘A’ weighted @ 48kHz) ADC

−-87dB THD (48kHz) ADC

•DAC Sampling Frequency: 8kHz – 192kHz

•ADC Sampling Frequency: 8kHz – 192kHz

•Independent ADC and DAC Sample Rates

•2 and 3-Wire Serial Control Interface with readback, or

Hardware Control Interface

•GPO pins allow visibility of user selected status flags

•Programmable Audio Data Interface Modes

−I

2S, Left, Right Justified or DSP

−16/20/24/32 bit Word Lengths

•Three Independent Stereo DAC Outputs with Digital

Volume Controls

•Two Independent Master or Slave Audio Data Interfaces

•Flexible Digital Interface Routing with Clock Selection

Control

•2.7V to 5.5V Analogue, 2.7V to 3.6V Digital Supply

Operation

•48-lead TQFP Package

APPLICATIONS

•Digital TV

•DVD Players and Receivers

•Surround Sound AV Processors and Hi-Fi systems

•Automotive Audio