AC701 Evaluation Board www.xilinx.com UG952 (v1.2) August 28, 2013

© Copyright 2012–2013 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands

included herein are trademarks of Xilinx in the United States and other countries. PCI, PCI Express, PCIe, and PCI-X are trademarks of

PCI-SIG. All other trademarks are the property of their respective owners.

DISCLAIMER

The information disclosed to you hereunder (the “Materials”) is provided solely for the selection and use of Xilinx products. To the maximum

extent permitted by applicable law: (1) Materials are made available “AS IS” and with all faults, Xilinx hereby DISCLAIMS ALL

WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF

MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether

in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising

under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or

consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action

brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same.

Xilinx assumes no obligation to correct any errors contained in the Materials, or to advise you of any corrections or update. You may not

reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and

conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to warranty and

support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any

application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications:

http://www.xilinx.com/warranty.htm#critapps.

Revision History

The following table shows the revision history for this document.

Date Version Revision

10/23/2012 1.0 Initial Xilinx release.

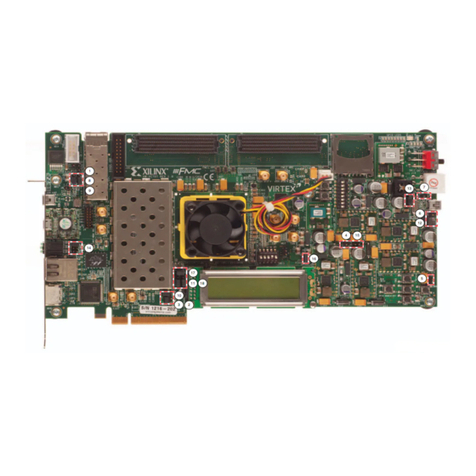

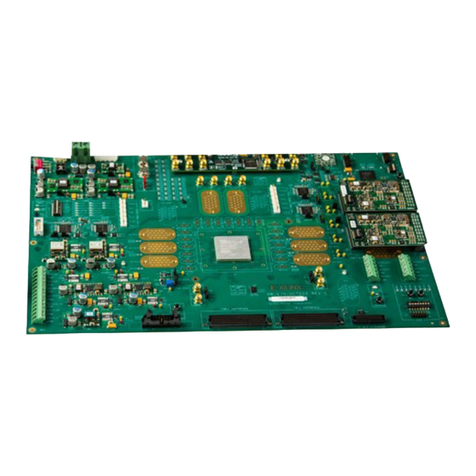

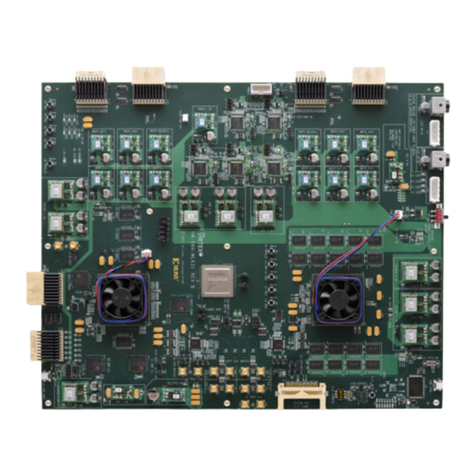

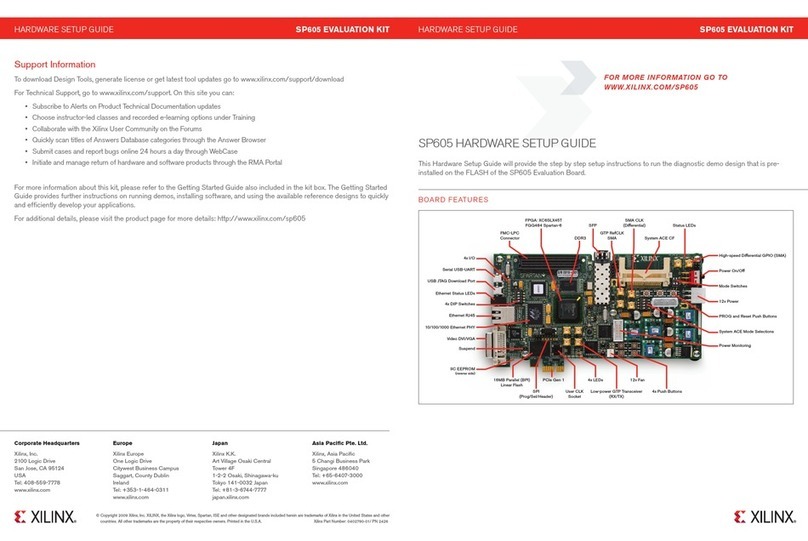

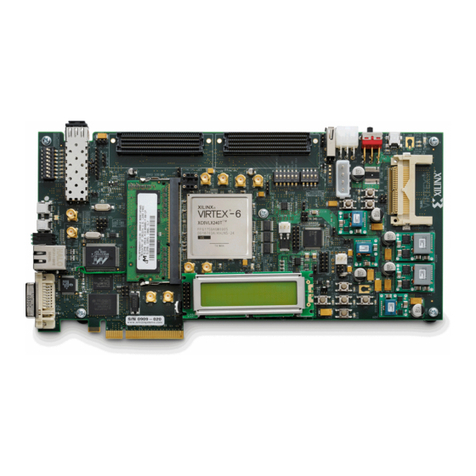

01/30/2013 1.1 Updated photograph in Figure 1-2, page 8 to revision 1.0 of the AC701 board. Revised

Figure 1-3. Revised last paragraph under DDR3 Memory Module, page 12, fourth

paragraph under USB JTAG Module, page 19, third paragraph under GTP Clock MUX,

page 26, first paragraph under 125 MHz Clock Generator, page 27, first, second and

third paragraphs under FMC HPC GBT Clocks, page 29, fourth paragraph under PCI

Express Edge Connector, page 34, and the first paragraph under SFP/SFP+ Connector,

page 36. Revised third and fourth rows in Table 1-13, page 37 and the fifth row in

Table 1-14, page 37. Revised second paragraph and added fourth paragraph under LCD

Character Display, page 45. Revised first paragraph under I2C Bus Switch, page 47.

Added Figure 1-31, page 51, Figure 1-33, page 51 and Figure 1-34, page 52. Revised

Figure 1-40, page 56. Added section AC701 Board Power System, page 61 and section

XADC Power System Measurement, page 66. Added third paragraph under Power

Management, page 69. Revised Figure 1-48, page 77. Revised Figure A-2, page 80.

Updated the Master Constraints File Listing in Appendix C. Added Appendix G,

Regulatory and Compliance Information.

08/28/2013 1.2 Added Figure 1-10. Revised Figure 1-2, Figure 1-48, and Figure 1-49. Updated Table 1-1,

Table 1-18, and Table 1-26. Updated Monitoring Voltage and Current. Updated

Appendix C, Master Constraints File Listing.