AMD XILINX T2 Telco User manual

Other AMD Video Card manuals

AMD

AMD FirePro W7000 User manual

AMD

AMD ATI Radeon HD 3400 Series User manual

AMD

AMD Radeon R9 285 Series User manual

AMD

AMD ATI Radeon HD 4890 User manual

AMD

AMD RADEON RX 7600 User manual

AMD

AMD ATI Radeon HD 2400 Series User manual

AMD

AMD ATI Radeon x1700 FSC User's guide User manual

AMD

AMD ATI Radeon HD 2600 Series User's guide User manual

AMD

AMD Radeon HD 7790 User manual

AMD

AMD ATI Radeon HD 3800 Series User manual

AMD

AMD Radeon HD 7750 User manual

AMD

AMD ATI Radeon HD 4600 Series User manual

AMD

AMD Radeon RX 6000 Series User manual

AMD

AMD FirePro W8100 User manual

AMD

AMD HD2600 - Radeon Pro 256MB Pcie User manual

AMD

AMD Vega 10 Product guide

AMD

AMD RADEON RX 7000 Series User manual

AMD

AMD ATI Radeon HD 5600 Series User manual

AMD

AMD ATI Radeon HD 5970 User manual

AMD

AMD ATI Radeon HD 4800 Series User manual

Popular Video Card manuals by other brands

Gainward

Gainward GeForce GTX 690 4GB brochure

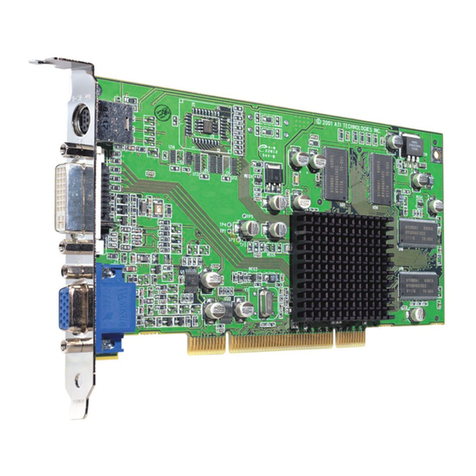

ATI Technologies

ATI Technologies RADEON 137-40225-20 user guide

MSI

MSI N220GT series user manual

ATI Technologies

ATI Technologies RADEON 7000 MAC EDITION user guide

SIIG

SIIG aurora Quick installation guide

ClearSpeed

ClearSpeed ClearSpeed Advance e720 user guide