EVAL-AD7761FMCZ User Guide UG-949

Rev. 0 | Page 5 of 17

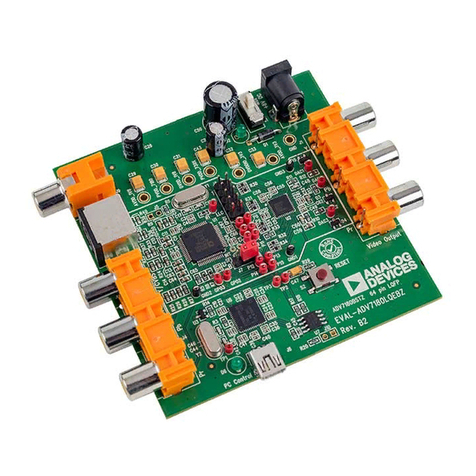

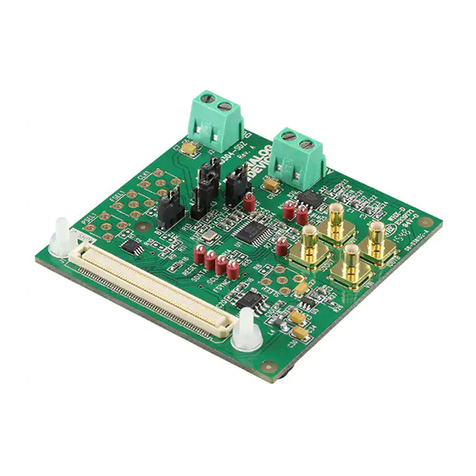

EVALUATION BOARD HARDWARE

DEVICE DESCRIPTION

The AD7761 is an 8-channel, simultaneously sampling, Σ-Δ

ADC. The AD7761 offers an ADC per channel and synchronized

sampling. The ADC power scaling is as required for the

application, catered for by selecting one of the following modes

of operation:

Fast: 256 kSPS maximum, 110.8 kHz input bandwidth,

52 mW per channel

Median: 128 kSPS maximum, 55.4 kHz input bandwidth,

28 mW per channel

Focus: 32 kSPS maximum, 13.8 kHz input bandwidth,

9.5 mW per channel

The AD7761 offers extensive digital filtering:

Wideband: low ripple, antialiasing, low-pass filter with

sharp roll off, and full attenuation at Nyquist frequency.

Sinc response: sinc5 filter, low latency path for dc

measurements or control loops.

Within these filter options, the user can select a decimation rate

of 32, 64, 128, 256, 512, or 1024.

Embedded analog functionality on each ADC channel simplifies

system design. A precharge buffer on each analog input reduces

analog input current.

Complete specifications for the AD7761 are provided in the

product data sheet and should be consulted in conjunction with

this user guide when using the evaluation board. Full details

about the EVAL-SDP-CH1Z are available on the Analog

Devices, Inc., website.

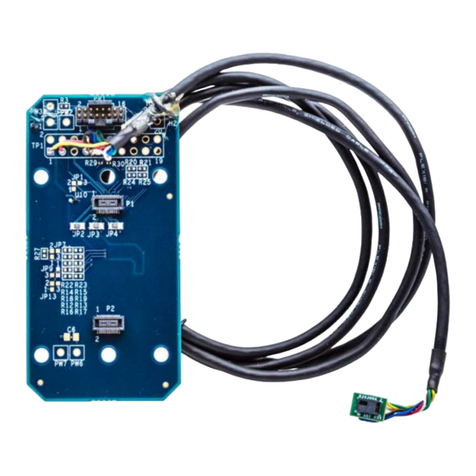

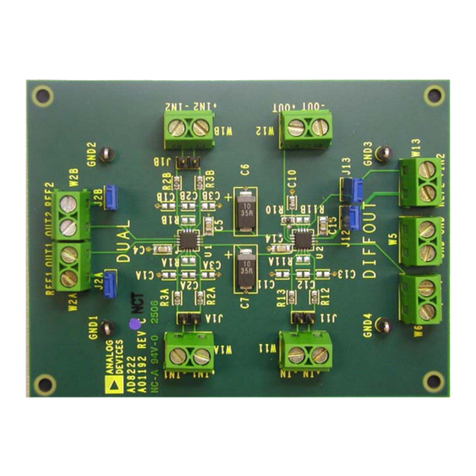

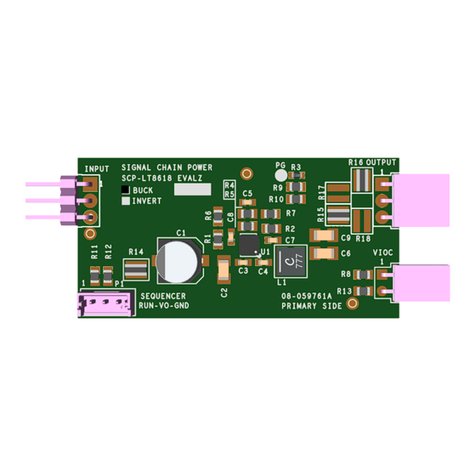

HARDWARE LINK OPTIONS

The default link options are listed in Table 1. The board can be

configured to operate from a bench top power supply via

Connector J3, or from a 9 V dc adapter via Connector J1. The

supply required for the AD7761 comes from the on-board low

dropout regulators (LDOs), which generate their input voltage

from J1 or J3, depending on the setting of LK1. Alternatively,

the board can be powered by setting LK2 to Position A when used

in conjunction with the EVAL-SDP-CH1Z (see Table 3 for details).

Table 1. Default Link and Solder Link Options

Link No. Default Option Description

LK1 A LK1 selects the input voltage source.

Position A: J3 is selected.

Position B: J1 is selected.

LK2 B LK2 selects the input from EVAL-SDP-CH1Z board.

Position A: 12 V input from EVAL-SDP-CH1Z.

Position B: external power supply from either J1 or J3.

SL1 A SL1 selects between pin mode and SPI mode operation of the AD7761.

Position A: SPI mode.

Position B: pin mode (pin mode is not compatible with the evaluation software and currently

untested on the evaluation board).

SL2 B FORMAT0 pin.

Position A: IOVDD.

Position B: DGND.

SL3 A FORMAT1 pin.

Position A: DGND.

Position B: IOVDD.

SL4 A Clock terminal source selection. To choose the Y1 crystal oscillator, do not populate SL4. R253,

R254, C46, and C45 must be populated. SL4A must be configured to the crystal oscillator.

Position A: selects CMOS Oscillator Y2.

Position B: unpopulated terminals (J6 and J7).

Position C: SDP MCLK.

SL4A A Clock select (CLK_SEL) pin.

CMOS clock option on Pin 32.

Crystal oscillator or LVDS option.

SL5 Soldered 0 Ω resistor Shorts SYNC_OUT to SYNC_IN to allow sync pulses on START to be synchronously applied to SYNC_IN.

SL6 A Pin 16: ST0/CS.

Position A: chip select (CS) pin in SPI mode.

Position B: Channel 0 to Channel 3 in standby mode (pin mode).

Position C: Channel 0 to Channel 3 enabled (pin mode).

Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.