AD9396

Rev. 0 | Page 9 of 48

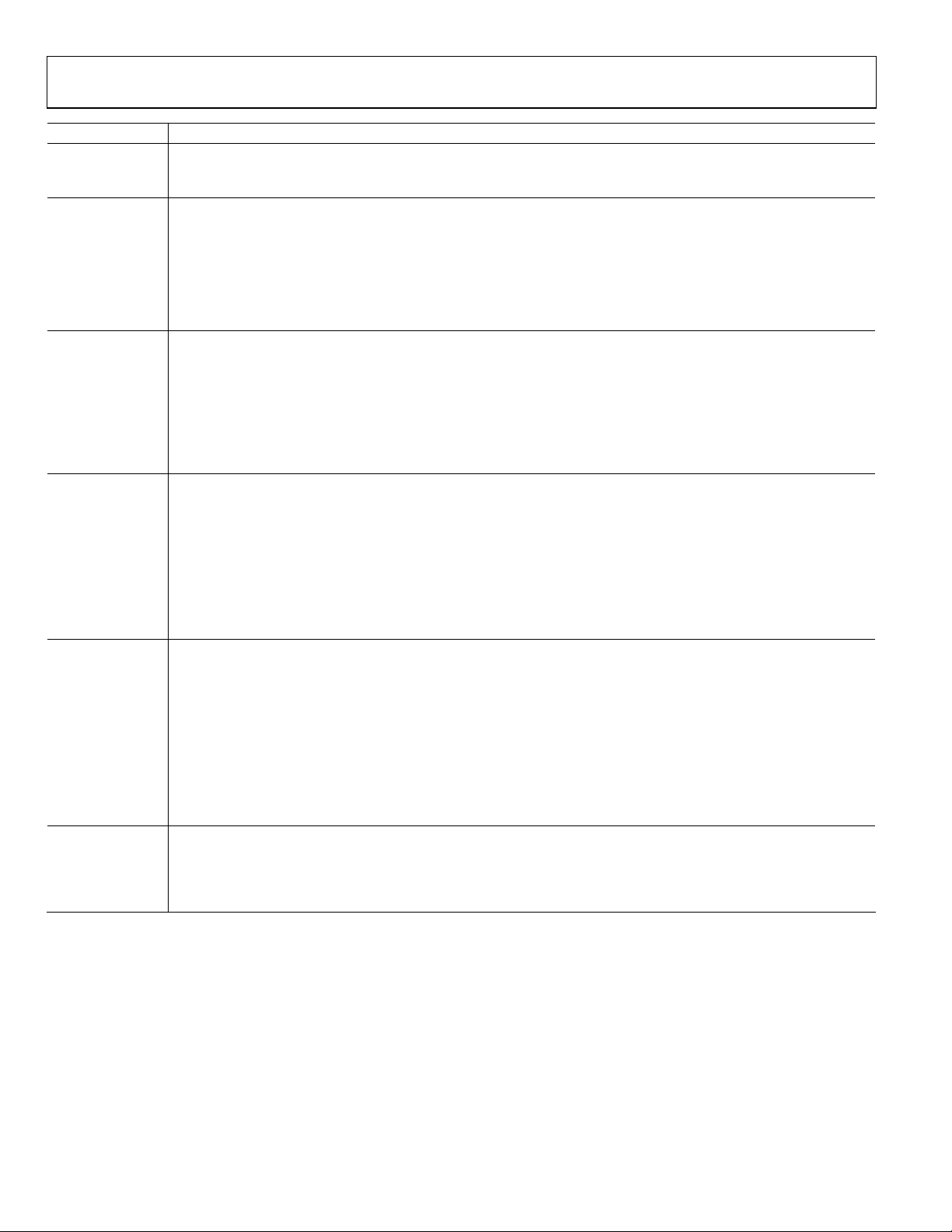

Mnemonic Description

RxC+ Digital Data Clock True.

RxC− Digital Data Clock Complement.

This clock pair receives a TMDS clock at 1× pixel data rate.

HSYNC 0 Horizontal Sync Input Channel 0.

HSYNC 1 Horizontal Sync Input Channel 1.

These inputs receive a logic signal that establishes the horizontal timing reference and provides the frequency

reference for pixel clock generation. The logic sense of this pin is controlled by Serial Register 0x12, Bits 5:4 (HSYNC

polarity). Only the leading edge of HSYNC is active; the trailing edge is ignored. When HSYNC polarity = 0, the falling

edge of HSYNC is used. When HSYNC polarity = 1, the rising edge is active. The input includes a Schmitt trigger for

noise immunity.

VSYNC 0 Vertical Sync Input Channel 0.

VSYNC 1 Vertical Sync Input Channel 1.

These are the inputs for vertical sync.

SOGIN 0 Sync-on-Green Input Channel 0.

SOGIN 1 Sync-on-Green Input Channel 1.

These inputs are provided to assist with processing signals with embedded sync, typically on the green channel. The

pin is connected to a high speed comparator with an internally generated threshold. The threshold level can be

programmed in 10 mV steps to any voltage between 10 mV and 330 mV above the negative peak of the input signal.

The default voltage threshold is 150 mV. When connected to an ac-coupled graphics signal with embedded sync, it

produces a noninverting digital output on SOGOUT. (This is usually a composite sync signal, containing both vertical

and horizontal sync (HSYNC) information that must be separated before passing the horizontal sync signal to HSYNC.)

When not used, this input should be left unconnected. For more details on this function and how it should be

configured, refer to the HSYNC and VSYNC Inputs section.

EXTCLK/COAST Coast Input to Clock Generator (Optional).

This input may be used to cause the pixel clock generator to stop synchronizing with HSYNC and continue producing a

clock at its current frequency and phase. This is useful when processing signals from sources that fail to produce

horizontal sync pulses during the vertical interval. The coast signal is generally not required for PC-generated signals.

The logic sense of this pin is controlled by coast polarity (Register 0x18, Bits 6:5). When not used, this pin may be

grounded and input coast polarity programmed to 1 (Register 0x18, Pin 5), or tied high (to VDthrough a 10 kΩ resistor)

and input coast polarity programmed to 0. Input coast polarity defaults to 1 at power-up. This pin is shared with the

EXTCLK function, which does not affect coast functionality. For more details on coast, see the description in the Clock

Generation section.

EXTCLK/COAST External Clock.

This allows the insertion of an external clock source rather than the internally generated PLL-locked clock. This pin is

shared with the coast function, does not affect EXTCLK functionality.

RTERM RTERM is the termination resistor used to drive the AD9396 internally to a precise 50 Ω termination for TMDS lines. This

should be a 500 Ω 1% tolerance resistor.

PWRDN Power-Down Control/Three-State Control.

The function of this pin is programmable via Register 0x26 [2:1].

FILT External Filter Connection.

For proper operation, the pixel clock generator PLL requires an external filter. Connect the filter shown in Figure 6 to

this pin. For optimal performance, minimize noise and parasitics on this node. For more information see the section on

PCB Layout Recommendations.

OUTPUTS

HSOUT Horizontal Sync Output.

A reconstructed and phase-aligned version of the HSYNC input. Both the polarity and duration of this output can be

programmed via the serial bus registers. By maintaining alignment with DATACK and Data, data timing with respect to

horizontal sync can always be determined.

VSOUT Vertical Sync Output.

The separated VSYNC from a composite signal or a direct passthrough of the VSYNC signal. The polarity of this output

can be controlled via serial bus bit (Register 0x24 [6]).

SOGOUT Sync-on-Green Slicer Output.

This pin outputs one of four possible signals (controlled by Register 0x24 [2:1]): raw SOG, raw HSYNC, regenerated

HSYNC from the filter, or the filtered HSYNC. See Figure 8, the Sync Processing Block Diagram, to view how this pin is

connected. (Note: besides slicing off SOG, the output from this pin is not processed on the AD9396. VSYNC separation

is performed via the sync separator.

O/E FIELD Odd/Even Field Bit for Interlaced Video. This output identifies whether the current field (in an interlaced signal) is odd

or even. The polarity of this signal is programmable via Register 0x24 [4].