1. Overview

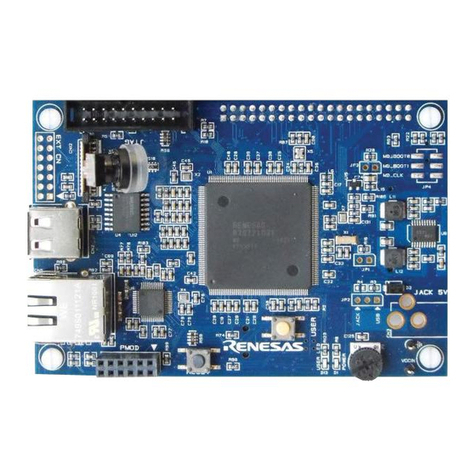

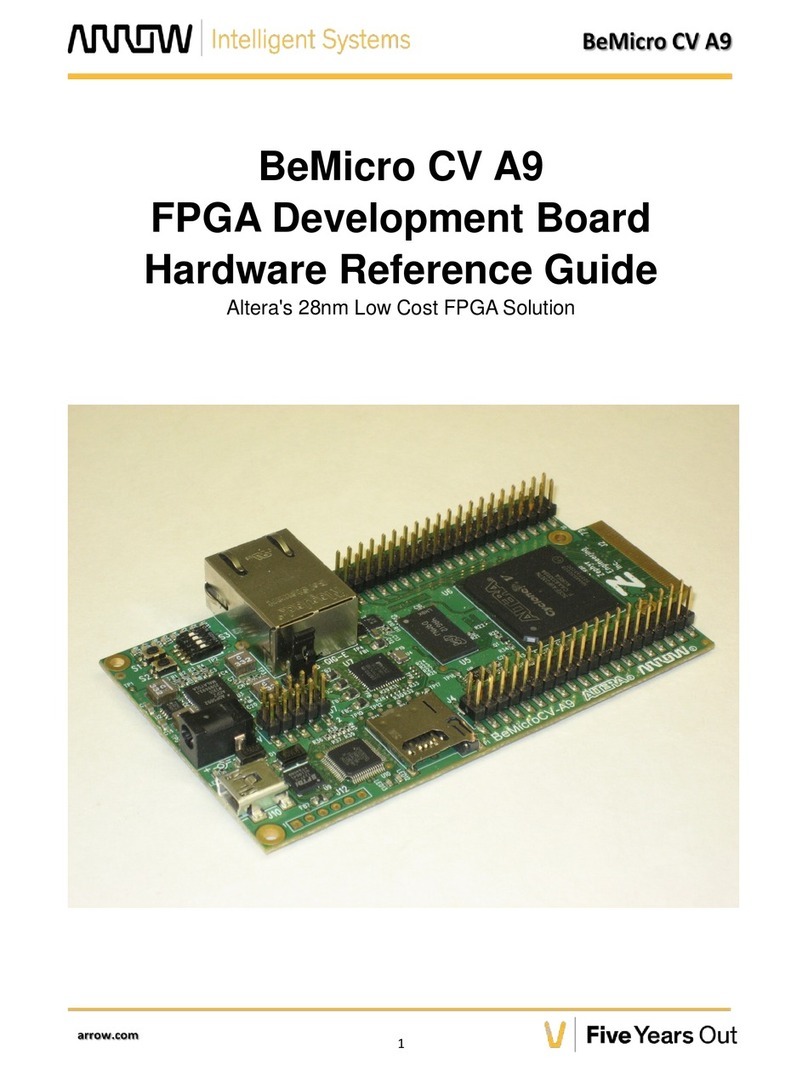

This document describes the hardware features of the BeMicro CV A9 Cyclone V E FPGA

Development Board, including component references and detailed pin-out information.

General Description

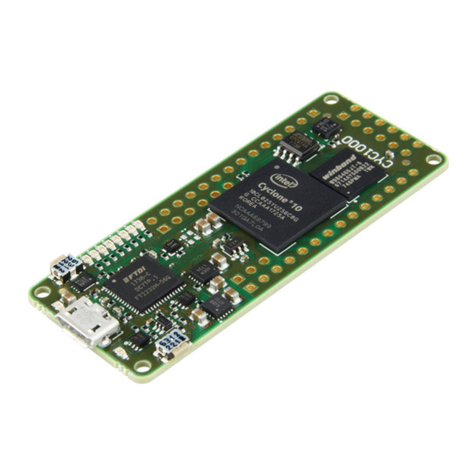

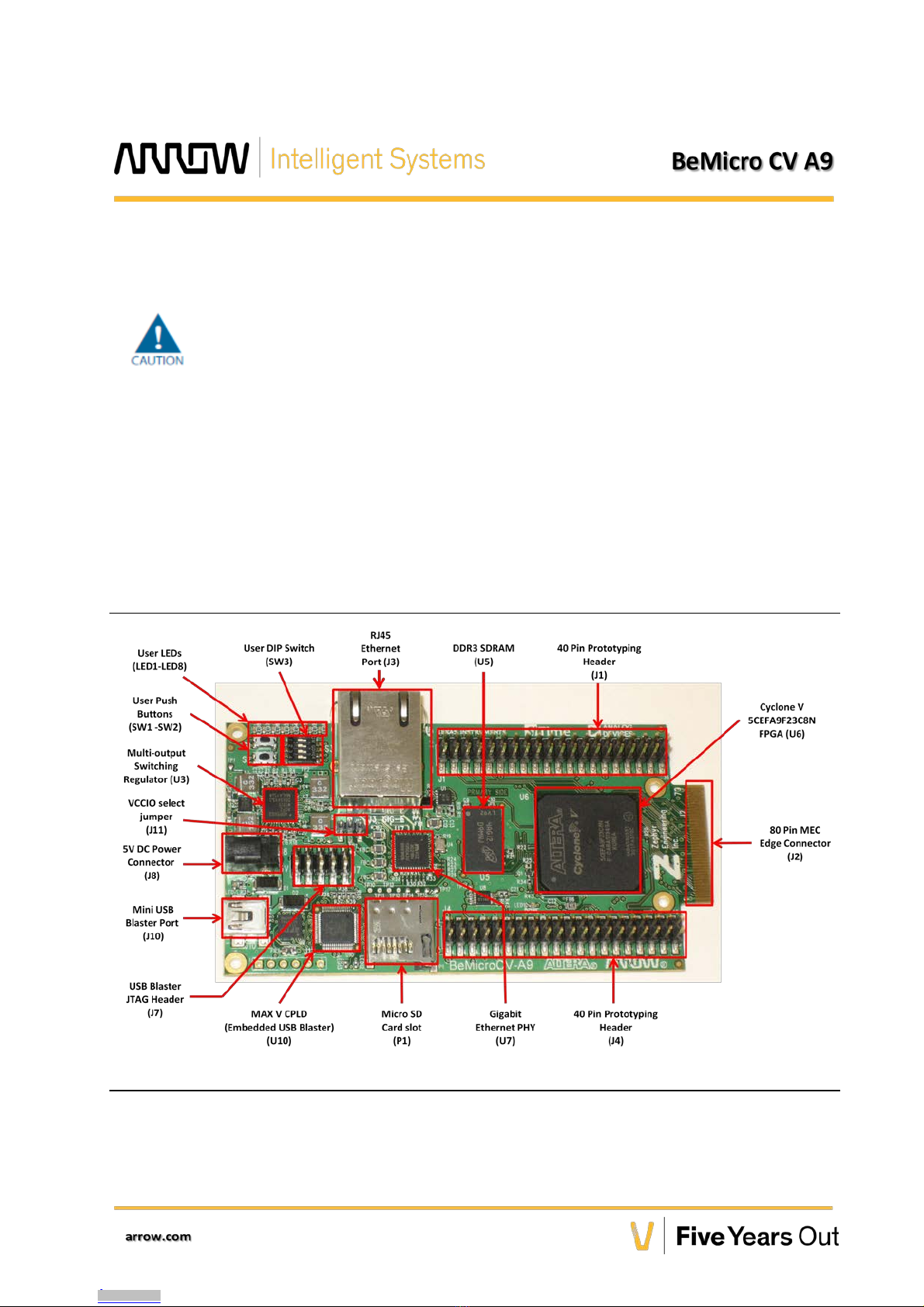

The Arrow Electronics BeMicro CV A9 is an enhanced BeMicro CV development board that

utilizes Altera’s 28-nm low-cost Cyclone V FPGA. It retains all the main features of the original

BeMicro CV predecessor while providing a higher logic density and additional features. The

5CEFA9F23C8N on the BeMicro CV A9 includes a hardened memory controller (HMC) connected

to a single 16-bit wide, 1Gb DDR3 SDRAM device. FPGA user I/O are routed to the two 40-pin

I/O headers and 80-pin MEC-style edge connector. The BeMicro CV A9 also includes an on

board USB Blaster programmer, Micro-SD card slot, and a 10/100/1000 Ethernet PHY.

The BeMicro CV A9 is well suited for DSP and logic-intensive applications such as Software

Defined Radio (SDR), data acquisition, and video processing. BeMicro CV A9 is compatible

with the Arrow BeScope digital oscilloscope, SDRstickTM SDR front-end boards, and the Terasic

MTL LCD module. For a complete list of products compatible with BeMicro CV A9 board, see

the BeMicro CV A9 Partner Pack at http://www.arrow.com/bemicro.

Users can easily migrate existing designs from BeMicro SDK or BeMicro CV to BeMicro CV A9.

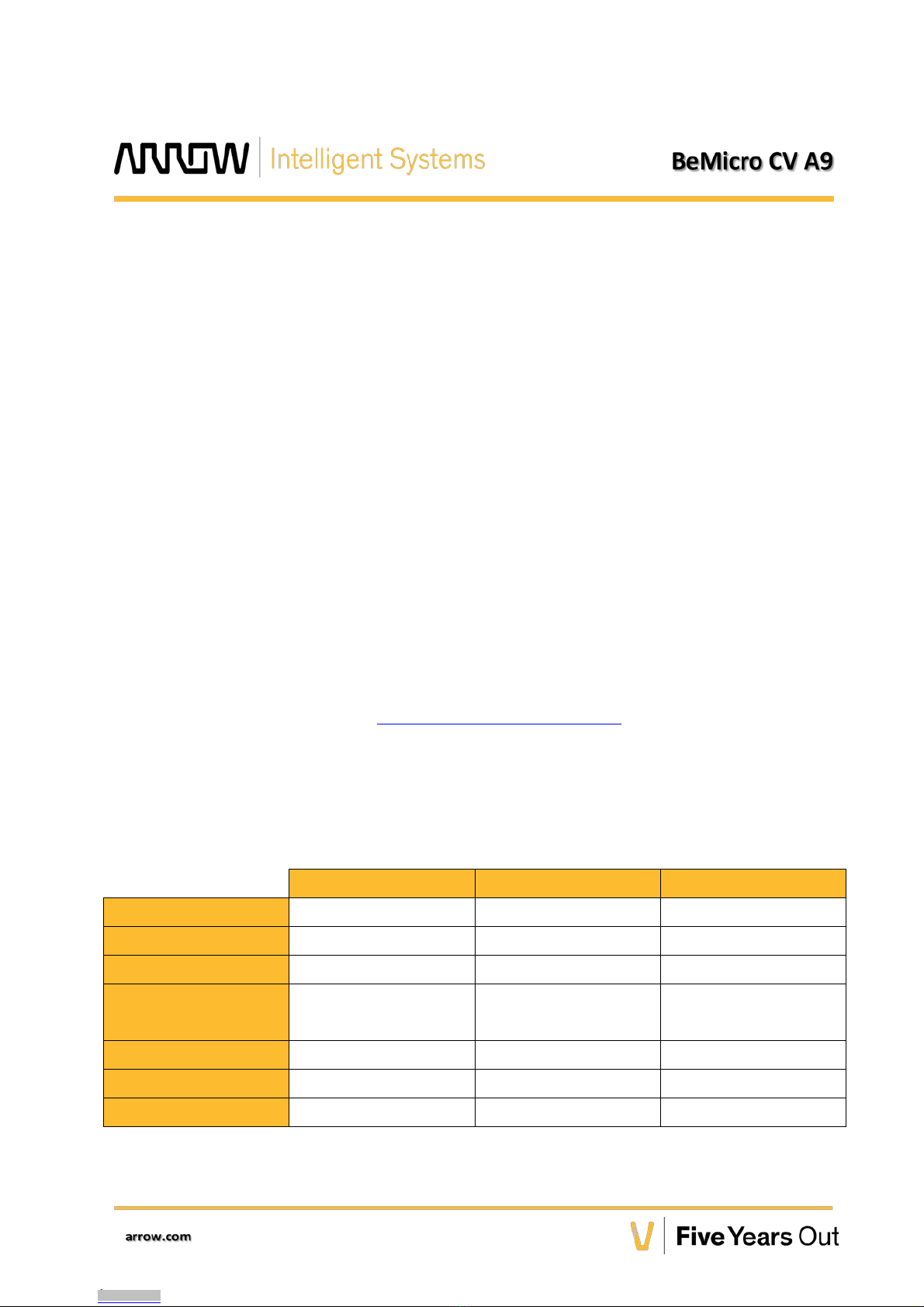

Table 1-1 provides a brief feature comparison of the Cyclone-based BeMicro development

boards.

Table 1-1: BeMicro Feature Comparison

BeMicro SDK BeMicro CV BeMicro CV A9

FPGA EP4CE22F17C7 5CEFA2F23C8N 5CEFA9F23C8N

External Memory Mobile DDR DDR3 DDR3

Memory Controller Soft (Microtronix) Hard Hard

Expansion I/O 80 pin edge connector 2 x 40 pin I/O +

80 pin edge connector

2 x 40 pin I/O +

80 pin edge connector

Ethernet Yes No Yes

USB Blaster Integrated Integrated Integrated

Micro-SD card slot Yes Yes Yes

3