Asahi KASEI AKD5538-B User manual

Other Asahi KASEI Motherboard manuals

Asahi KASEI

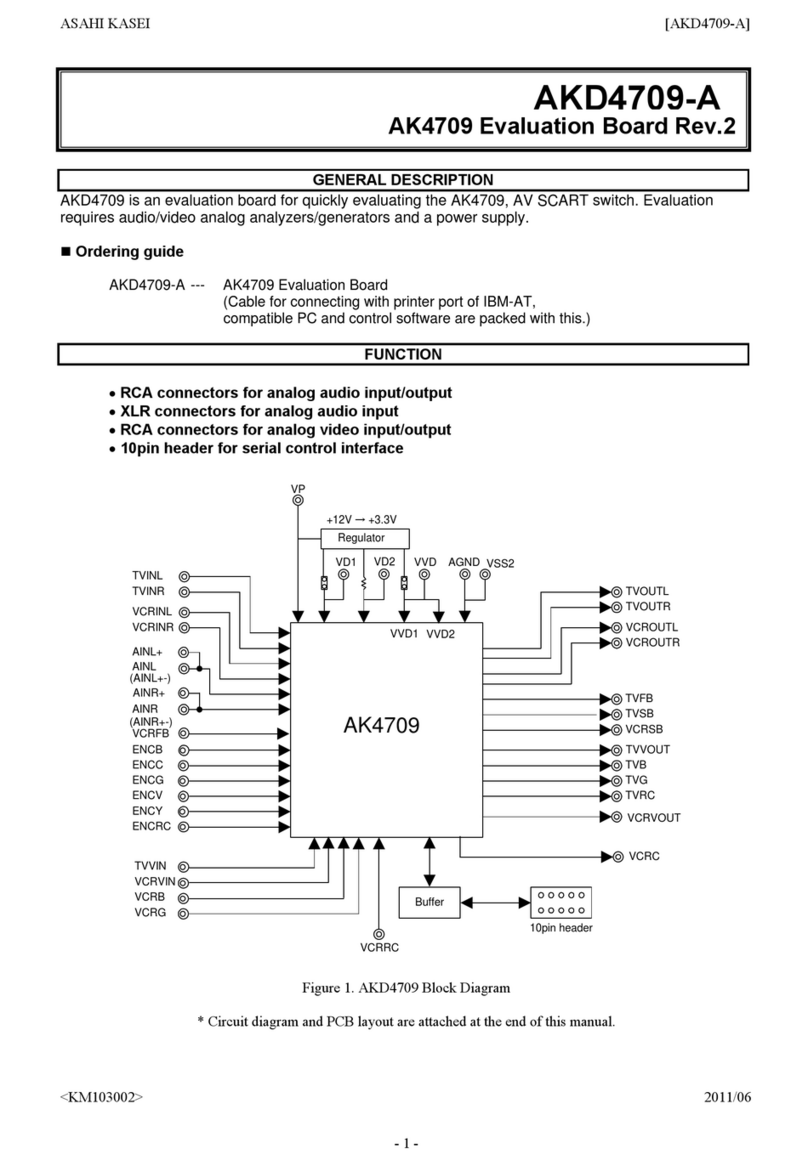

Asahi KASEI AKD4709-A User manual

Asahi KASEI

Asahi KASEI AK5704 User manual

Asahi KASEI

Asahi KASEI AKD2300 User manual

Asahi KASEI

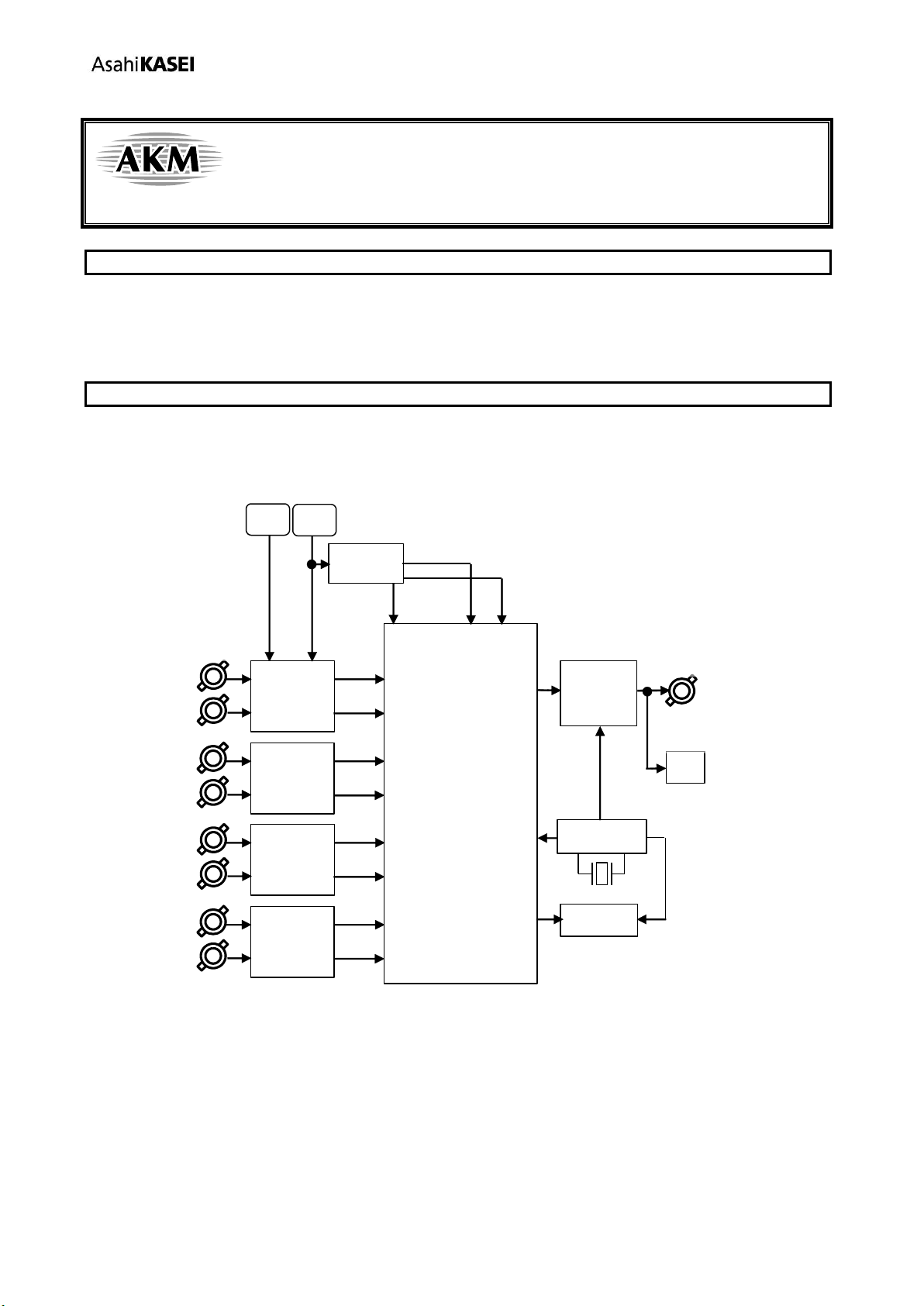

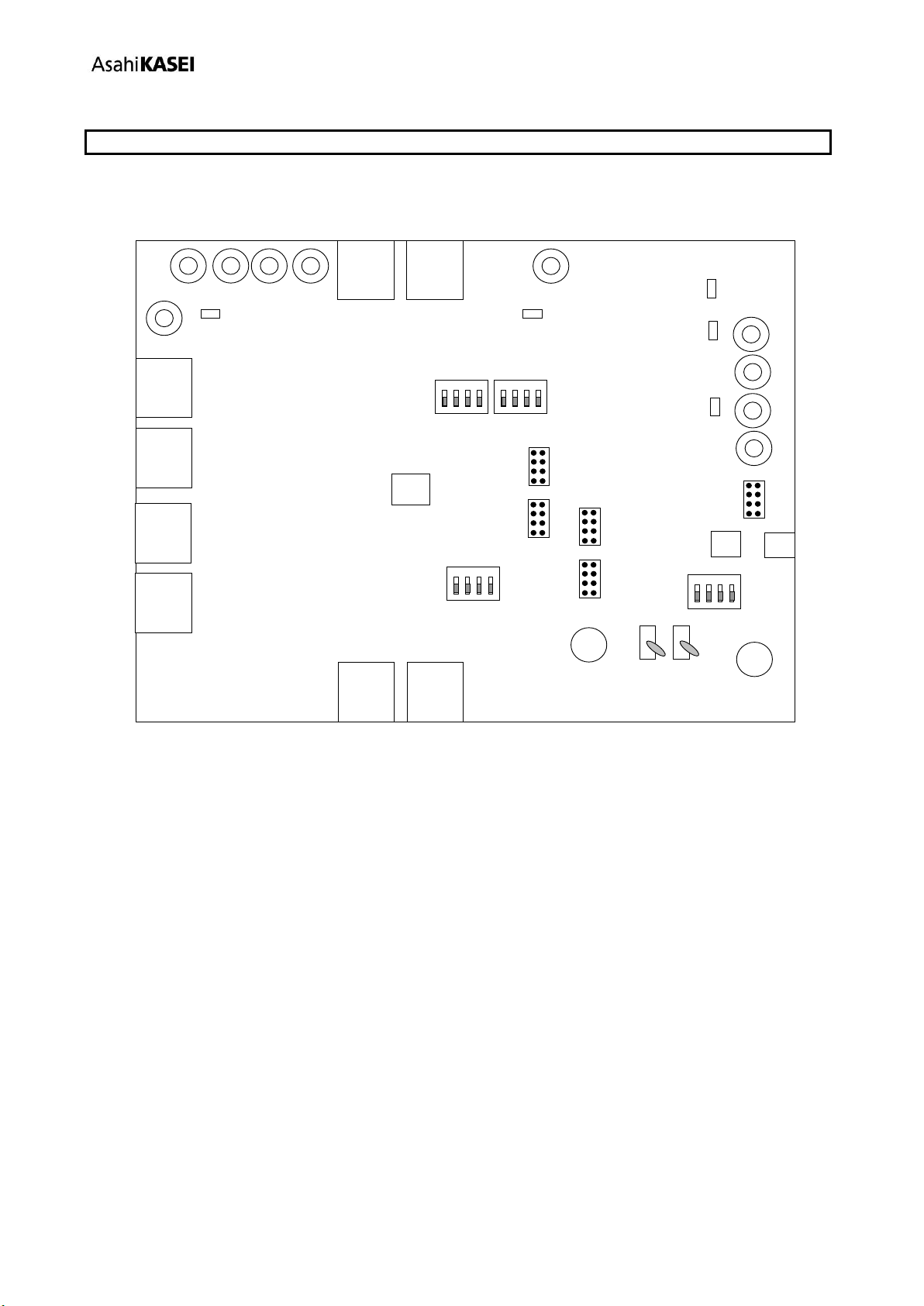

Asahi KASEI AKM AKD5538-B User manual

Asahi KASEI

Asahi KASEI AKD4220-A User manual

Asahi KASEI

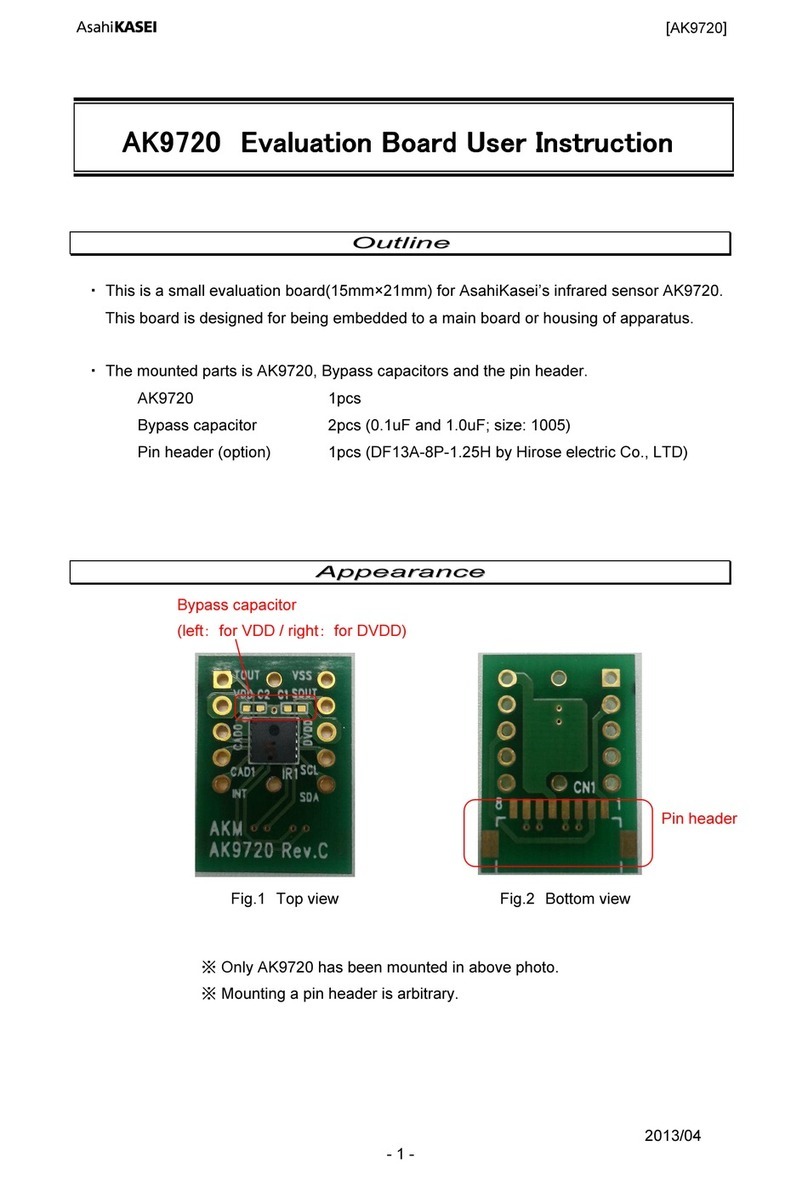

Asahi KASEI AK9720 Installation instructions

Asahi KASEI

Asahi KASEI AKD4140-B User manual

Asahi KASEI

Asahi KASEI AKD4382A-SB User manual