AT91 ARM Thumb

3

The ISO 7816-3 specification implements two different conventions for data transfer: direct or reverse convention. For more

convenience, this application note refers to the direct convention, which is to say:

• not inverted bits (logical “1” = HIGH state)

• Least Significant Bit (LSB) first

• even parity (number of “1’s” in data + parity fields is even)

The beginning of the byte is indicated by a start bit at LOW level. Then, the 8 data bits are transmitted, followed by the par-

ity bit. Afterwards, 2 stop bits, at HIGH level, are transmitted. If the receiver does not detect a parity error, it waits for the

next start bit and the sender transmits the next byte after the 2 stop bits. If the receiver does detect an error, it indicates this

to the sender by setting the line at LOW level somewhere between the half of the first stop bit and the half of the second

stop bit. Therefore, the sender checks the I/O line at the end of the first stop bit and, if it is LOW, transmits a third stop bit at

HIGH level, and then re-sends the same byte from the beginning.

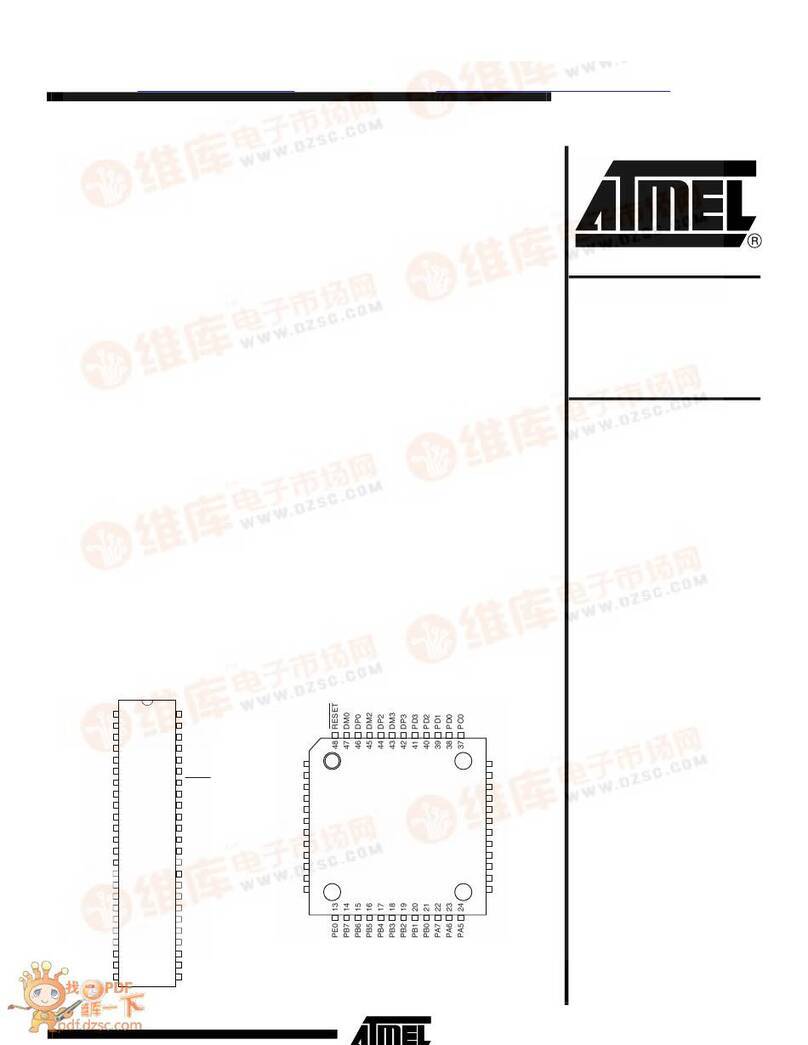

Figure 1. Communication on the I/O Line without Parity Error

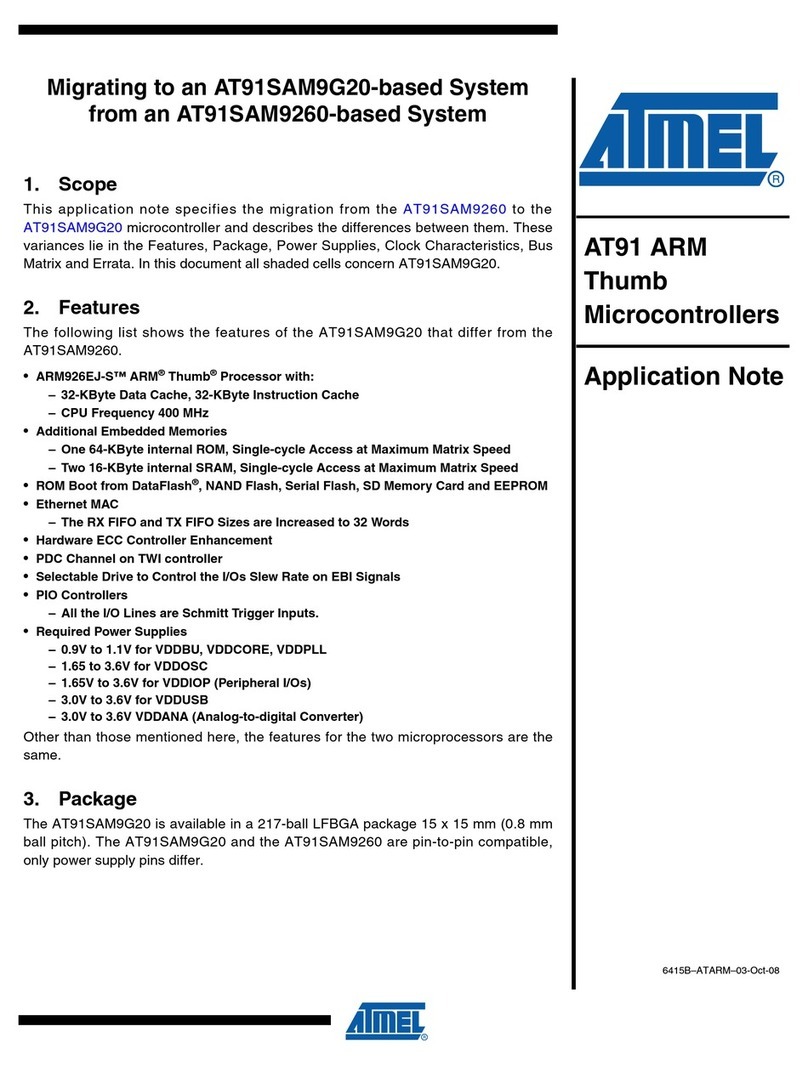

Figure 2. Communication on the I/O Line with Parity Error

For more information concerning the I/O Line, please refer to the ISO 7816-3 Specification.

AT91M40400 Implementation

This application note describes how to implement an ISO 7816-3 I/O line with an AT91M40400. It describes only the byte

transfer feature. It does not refer to the type of protocol used (T = 0 or T = 1), or the type of frame. These points are relevant

to a higher protocol layer and to the application. Nor does it describe the clock and reset (which can be generated with

another timer channel) or the VCC generation.

One of the three channels from the AT91M40400 Timer Counter block can be chosen to implement the I/O line. The

received bytes are stored in a reception buffer. The bytes to transmit come from a transmission buffer. By default, the ISO

line is in reception mode, except when a transmission is requested by a higher application level.

The timer is clocked from its external clock input (TCLKi) linked to the ISO clock and the corresponding TIOB signal is used

as the I/O line. It is used in wave form mode in order to drive TIOB as input or output. Note that when driven for transmis-

sion, the TIOB line is physically held for HIGH level as well as for LOW. Bit duration and sampling are performed by using

the TC_RC (Register C) and TC_RA (Register A):

• TC_RC is set with the bit time value (the clock divisor Fi / Di).

In reception and transmission mode, the counter is reset at each RC Compare event.

In transmission mode, each RC Compare event generates an interrupt in order to set each bit at the beginning of a bit

period.

• TC_RA is set with the half bit time value (the clock divisor divided by 2).

In reception mode, each RA Compare event generates an interrupt in order to get the I/O line state at the middle of each

bit.

start byte iPguard time

(2 stop bits) start byte i+1

start byte iPerror

signal 3rd

stop bit start byt