www.awinic.com 9 Copyright © 2020 SHANGHAI AWINIC TECHNOLOGY CO., LTD

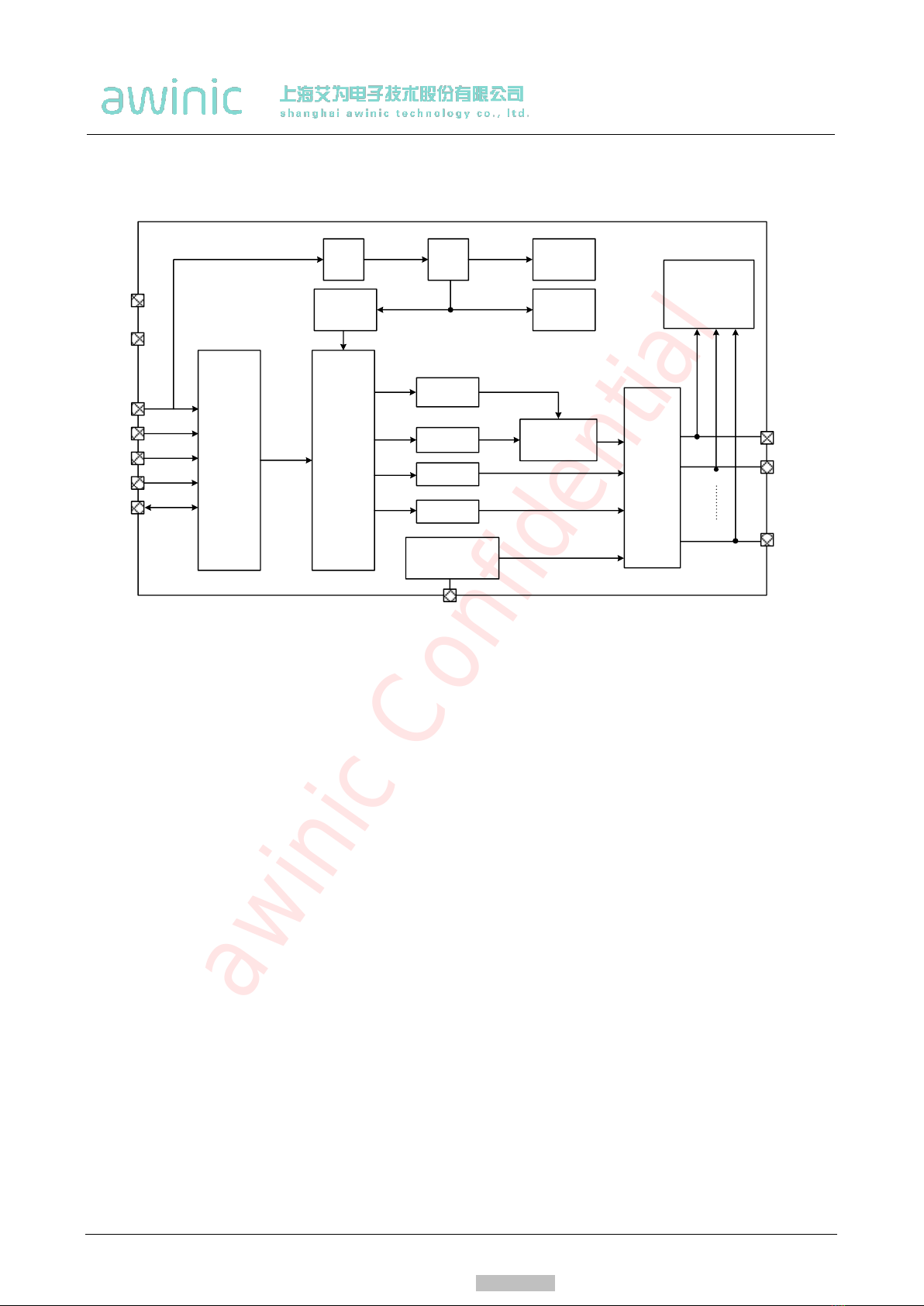

Detailed Functional Description

OVERVIEW

AW21018 is an18 channel multi-function LED driver with I2C interface. Each channel has individual 8-bit DC

current setting for color-mixing and maximum 12-bit PWM resolution for brightness control. The global current

of each channel is recommended to be 40mA configured via register and external resistor REXT.

Phase-control, spread spectrum technology and slew rate control are utilized to reduce EMI and audible noise

caused by MLCC. Output current of each LED can be controlled by one pattern or be configured independently.

The integrated pattern controller provides breathing or group dimming control. The breathing mode includes

auto breathing and manual control mode. All breathing parameters are configurable including rising/falling

slope, on/off time, repeat times and brightness.

OPERATION MODE AND RESET

RESET

Power On Reset

Upon initial power-up, the AW21018 is reset by internal power-on-reset, and all registers are reset to default

value, and the chip is shut down.

Once the supply voltage VDD drops below the threshold voltage VPOR(2.0V), the power-on-reset will reset the

chip again. By reading the bit PUST of the register UVCR (address 60h), whether the chip has been reset can

be detected.

When the VDD ramps up above the threshold voltage VPOR (2.0V) and EN is high, POR is pulled high, meanwhile

the chip enters into initialization mode. The chip needs about 2ms to load the efuse information in initalization

mode. After initialization, it works in lower-power mode. About 200μs delay is required after CHIPEN is pulled

up, otherwise, internal OSCCLK may work incorrectly. Only in low-power and active mode, registers could be

configurated. The recommended operation timing is shown as bellow.

VDD

POR

CHIPEN

OSC

Initialization

initial

Standby Active

200μs

EN

..

2ms

Shutdown

INITIAL

MODE

Note: Thechip needsabout 2ms for

initalization after power on

(bit CHIPEN of GCR register)

Note: Recommend CHIPEN=1 after Initial

Note: OSC operates stable,which needs

200μs after CHIPEN=1

Internal registers are configurable

Configuring

Time

Figure 7 Power On Timing

Software Reset

By writing 00h to register RESET (address 70h) in active mode, the software reset is triggered. Then all

registers will be reset to the default value and the chip enters into initialization mode.

After the software reset command is input by I2C, it needs to wait at least 2ms before any other I2C commands