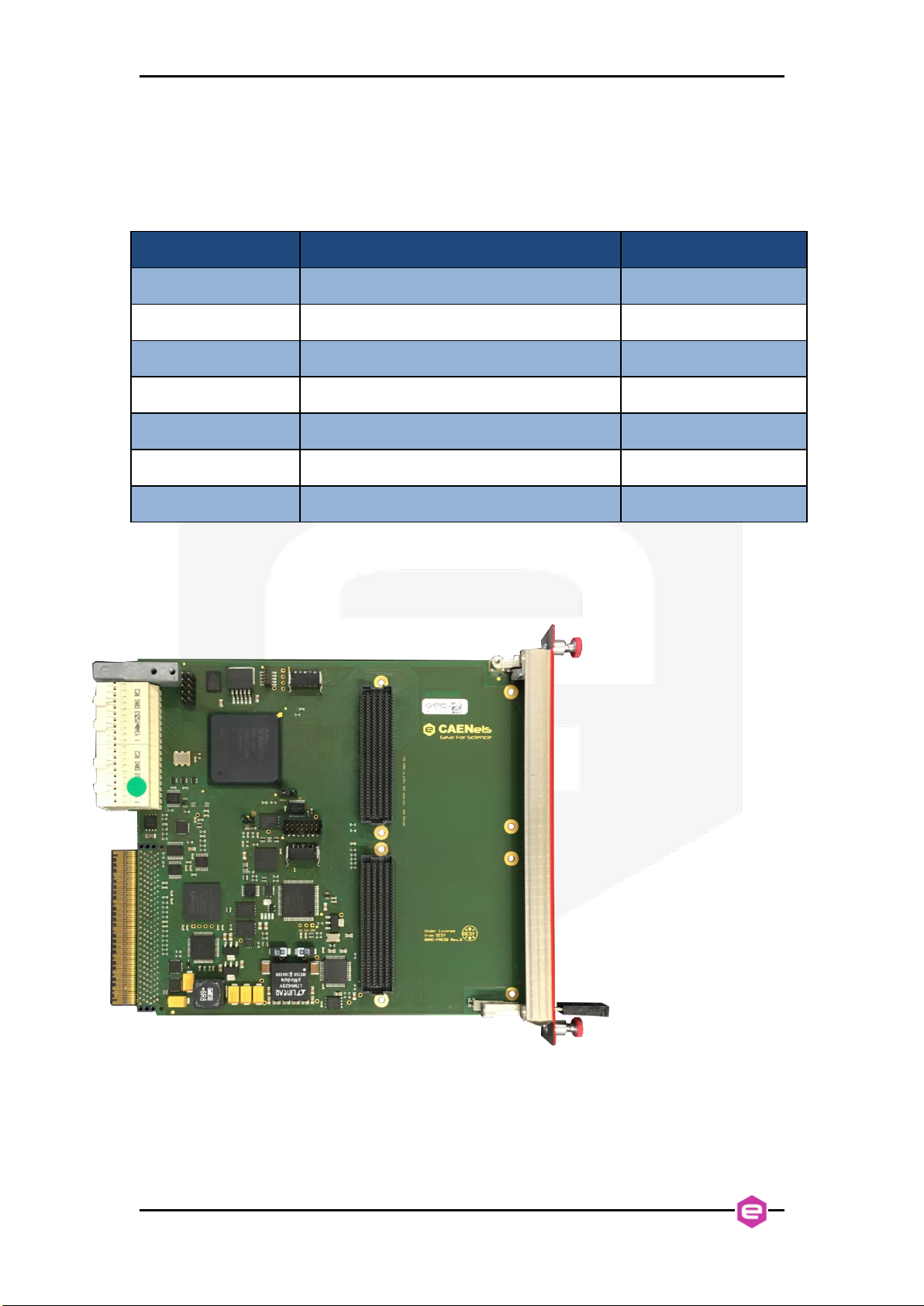

DAMC-FMC20 User’s Manual

3

Table Of Contents

1. INTRODUCTION................................................................................................8

1.1 DAMC-FMC20 DESCRIPTION........................................................................8

1.2 DAMC-FMC20 OVERVIEW .........................................................................10

2. DAMC-FMC20 ARCHITECTURE.................................................................11

2.1 CLOCK TREE .................................................................................................12

2.2 JTAG CHAIN ................................................................................................14

2.3 FLASH PROGRAMMING................................................................................15

2.4 MODULE MANAGEMENT...............................................................................15

2.4.1 On-board Diagnostics..............................................................................16

2.4.2 On-board Voltage Monitoring and Implemented Functions ...................16

2.4.3 I2C Buses .................................................................................................17

2.4.1 AMC Connectivity....................................................................................17

2.5 RTM CONNECTOR ........................................................................................18

2.5.1 Zone 3 Class Compatibility......................................................................20

2.6 FMC CONNECTORS.......................................................................................21

2.6.1 FMC Connectors Remarks.......................................................................21

2.7 LED INDICATORS..........................................................................................21

2.8 MGT ROUTING AND CROSSPOINT SWITCH ...................................................22

2.9 POWER SUPPLY ARCHITECTURE ...................................................................23

2.10 CONNECTOR PIN ASSIGNMENTS....................................................................24

2.10.1 FMC Power Connector........................................................................24

2.10.2 JTAG Connector ..................................................................................24

2.10.3 Atmel Programmer Connector.............................................................25

2.10.4 RTM connector.....................................................................................25

2.10.5 AMC Connector Pin Assignment.........................................................27

2.10.6 FMC Low Pin Count (LPC) connector................................................28

2.10.7 FMC High Pin Count (HPC) Connector.............................................29

2.11 PINOUT FOR FPGAS......................................................................................31

2.11.1 UCF for Main FPGA...........................................................................31

2.11.2 UCF for Transceiver FPGA.................................................................45

3. REFERENCE FIRMWARE.............................................................................49

4. TECHNICAL SPECIFICATIONS ..................................................................51