Cirrus Logic CS4953xx Instructions for use

Copyright 2008 Cirrus Logic, Inc. JULY ’08

DS732UM7

http://www.cirrus.com

CS4953x

32-bit Audio DSP Family

Preliminary Product Information This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CS4953xx

Hardware Users Manual

DS732UM7 Copyright 2008 Cirrus Logic, Inc. ii

CS4953xx Hardware Users Manual

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative.

To find the one nearest to you go to www.cirrus.com

I

MPORTANT NOTICE

“Preliminary” product information describes products that are in production, but for which full characterization data is not yet available.

Cirrus Logic, Inc. and its subsidiaries (“Cirrus”) believe that the information contained in this document is accurate and reliable. However, the information

is subject to change without notice and is provided “AS IS” without warranty of any kind (express or implied). Customers are advised to obtain the latest

version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the

terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability.

No responsibility is assumed by Cirrus for the use of this information, including use of this information as the basis for manufacture or sale of any items, or

for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license,

express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copy-

rights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization

with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution,

advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE

PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WAR-

RANTED FOR USE IN PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT

PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OFCIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY

AT THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IM-

PLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS

USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITI-

CAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIB-

UTORSAND OTHERAGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM ORARISE

IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, the Cirrus Logic logo designs, DSP Composer, Cirrus Extra Surround, Cirrus Original Multichannel Surround, and Cirrus Original Sur-

round are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks or service marks of their respective

owners.

Dolby, Dolby Digital, Dolby Headphone, Dolby Virtual Speaker, AC-3, and Pro Logic are registered trademarks of Dolby Laboratories, Inc. AAC, Dolby

Headphone2, Dolby Virtual Speaker2, and Dolby Digital Surround EX are trademarks of Dolby Laboratories, Inc. Supply of an implementation of Dolby

technology does not convey a license nor imply a right under any patent, or any other industrial or intellectual property right of Dolby Laboratories, to use

the implementation in any finished end-user or ready-to-use final product. It is hereby notified that a license for such use is requiredfromDolbyLaboratories.

DTS and DTS Digital Surround are registered trademarks of the Digital Theater Systems, Inc. DTS-ES, DTS-ES 96/24, DTS Neo:6, DTS 96/24 are trade-

marks of the Digital Theater Systems, Inc. It is hereby notified that a third-party license from DTS is necessary to distribute software of DTS in any finished

end-user or ready-to-use final product.

THX

®

is a registered trademark of THX Ltd. THx Ultra2 and THx Select2 are trademarks of THx Ltd.

Re-equalization is a trademark of Lucasfilm, Ltd.

SRS, Circle Surround, and Trusurround XT are registered trademarks of SRS Labs, Inc. Circle Surround II is a trademark of SRS Labs, Inc. The Circle

Surround technology rights incorporated in the Cirrus Logic chip are owned by SRS Labs, Inc. and by Valence Technology, Ltd., and licensed to Cirrus

Logic, Inc.

Users of any Cirrus Logic chip containing enabled Circle Surround

®

technology (i.e., Circle Surround

®

licensees) must first sign a license to purchase pro-

duction quantities for consumer electronics applications which may be granted upon submission of a preproduction sample to, and the satisfactory passing

of performance verification tests performed by SRS Labs, Inc., or Valence Technology, Ltd. E-mail requests for performance specifications and testing rate

schedule may be made to cslicense@srslabs.com. SRS Labs, Inc. and Valence Technology, Ltd., reserve the right to decline a use license for any sub-

mission that does not pass performance specifications or is not in the consumer electronics classification.

All equipment manufactured using any Cirrus Logic chip containing enabled Circle Surround

®

technology must carry the Circle Surround

®

logo on the front

panel in a manner approved in writing by SRS Labs, Inc., or Valence Technology, Ltd. If the Circle Surround logo is printed in user manuals, service man-

uals, or advertisements, it must appear in a form approved in writing by SRS Labs, Inc. or Valence Technology, Ltd. The rear panel of products containing

Circle Surround technology and user manuals, service manuals, and advertising for those products must all carry the legends as described in Licensor’s

most current version of the Circle Surround Trademark Usage Manual.

Intel is a registered trademark of Intel Corporation.

Motorola and SPI are trademarks or registered trademarks of Motorola, Inc.

I

2

C is a registered trademark of Philips Semiconductor Corp.

Philips is a registered trademark of Koninklijke Philips Electronics N.V. Corp.

Sony and Direct Stream Digital are registered trademark of Sony Kabushiki Kaisha T.A. Sony Corporation.

DS732UM7 Copyright 2008 Cirrus Logic, Inc. iii

CS4953xx Hardware Users Manual

Contents

Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . v

Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .vi

Chapter 1. Introduction.........................................................................................1-1

1.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

1.1.1 Chip Features.................................................................................................................1-1

1.2 Functional Overview of the CS4953xx Chip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-4

1.2.1 DSP Core .......................................................................................................................1-4

1.2.2 Security Extension module.............................................................................................1-4

1.2.3 Debug Controller (DBC) .................................................................................................1-4

1.2.4 Digital Audio Output (DAO1, DAO2) Controller..............................................................1-4

1.2.5 Digital Audio Input (DAI1) Controller ..............................................................................1-4

1.2.6 Compressed Data Input / Digital Audio Input (DAI2) Controller .....................................1-4

1.2.7 Direct Stream Digital®(DSD) Controller.........................................................................1-5

1.2.8 General Purpose I/O.......................................................................................................1-5

1.2.9 Parallel Control Port (Motorola/Intel Standards).............................................................1-5

1.2.10 Serial Control Ports (SPI™or I2C®Standards) ............................................................1-5

1.2.11 SDRAM Controller........................................................................................................1-6

1.2.12 Flash Controller............................................................................................................1-6

1.2.13 DMA Controller.............................................................................................................1-6

1.2.14 Timers...........................................................................................................................1-6

1.2.15 Clock Manager and PLL...............................................................................................1-6

1.2.16 Programmable Interrupt Controller...............................................................................1-7

Chapter 2. Operational Modes..............................................................................2-1

2.1 Operational Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.2 Slave Boot Procedures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.2.1 Host Controlled Master Boot ..........................................................................................2-4

2.2.1.1 Performing a Host Controlled Master Boot (HCMB)......................................2-5

2.2.2 Slave Boot ......................................................................................................................2-7

2.2.2.1 Performing a Slave Boot................................................................................2-8

2.2.3 Boot Messages.............................................................................................................2-10

2.2.3.1 Slave Boot ..................................................................................................2-10

2.2.3.2 Host-Controlled Master Boot from Parallel ROM.........................................2-10

2.2.3.3 Host-Controlled Master Boot from I2C ROM................................................2-11

2.2.3.4 Host-Controlled Master Boot from SPI ROM...............................................2-11

2.2.3.5 Soft Reset ...................................................................................................2-12

2.2.3.6 Messages Read from CS4953xx.................................................................2-12

2.3 Master Boot Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

2.4 Softboot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

2.4.1 Softboot Messaging......................................................................................................2-14

2.4.2 Softboot Procedure.......................................................................................................2-15

2.4.2.1 Softboot Procedure......................................................................................2-15

2.4.2.2 Softboot Example ........................................................................................2-16

2.4.2.3 Softboot Example Steps ..............................................................................2-17

Chapter 3. Serial Control Port..............................................................................3-1

3.1 Serial Control Port Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

3.2 I2C Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-2

3.2.1 I2C System Bus Description...........................................................................................3-2

iv Copyright 2008 Cirrus Logic, Inc. DS732UM7

CS4953xx Hardware Users Manual

3.2.2 I2C Bus Dynamics ..........................................................................................................3-4

3.2.3 I2C Messaging................................................................................................................3-7

3.2.3.1 SCP1_BSY Behavior.....................................................................................3-7

3.2.3.2 Performing a Serial I2C Write ........................................................................3-8

3.2.3.3 I2C Write Protocol..........................................................................................3-9

3.2.3.4 Performing a Serial I2C Read ........................................................................3-9

3.2.3.5 I2C Read Procedure ....................................................................................3-11

3.2.3.6 SCP1_IRQ Behavior....................................................................................3-13

3.3 SPI Port. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-13

3.3.1 SPI System Bus Description.........................................................................................3-15

3.3.2 SPI Bus Dynamics........................................................................................................3-15

3.3.2.1 SCP1_BSY Behavior...................................................................................3-16

3.3.3 SPI Messaging .............................................................................................................3-16

3.3.3.1 Performing a Serial SPI Write......................................................................3-17

3.3.3.2 SPI Write Protocol .......................................................................................3-17

3.3.3.3 Performing a Serial SPI Read......................................................................3-18

3.3.3.4 SPI Read Protocol .......................................................................................3-19

3.3.3.5 SCP1_IRQ Behavior....................................................................................3-21

Chapter 4. Parallel Control Port ...........................................................................4-1

Chapter 5. Digital Audio Input Interface..............................................................5-1

5.1 Digital Audio Input Port Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

5.1.1 DAI Pin Description ........................................................................................................5-1

5.1.2 Supported DAI Functional Blocks...................................................................................5-2

5.1.3 BDI Port..........................................................................................................................5-2

5.1.4 Digital Audio Formats .....................................................................................................5-4

5.1.4.1 I2S Format .....................................................................................................5-4

5.1.4.2 Left-Justified Format......................................................................................5-4

5.2 DAI Hardware Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-4

5.2.1 DAI Hardware Naming Convention ................................................................................5-5

Chapter 6. Direct Stream Data (DSD) Input Interface.........................................6-1

6.1 Description of Digital Audio Input Port when Configured for DSD Input . . . . . . . . . . . . . . .6-1

6.1.1 DSD Pin Description.......................................................................................................6-1

6.1.2 Supported DSD Functional Blocks .................................................................................6-1

Chapter 7. Digital Audio Output Interface...........................................................7-1

7.1 Digital Audio Output Port Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-1

7.1.1 DAO Pin Description.......................................................................................................7-1

7.1.2 Supported DAO Functional Blocks.................................................................................7-2

7.1.3 DAO Interface Formats...................................................................................................7-3

7.1.3.1 I2S Format .....................................................................................................7-3

7.1.3.2 Left-Justified Format......................................................................................7-3

7.1.3.3 One-line Data Mode Format (Multichannel)...................................................7-4

7.1.4 DAO Hardware Configuration.........................................................................................7-4

7.1.5 S/PDIF Transmitter.........................................................................................................7-9

Chapter 8. External Memory Interfaces...............................................................8-1

8.1 SDRAM Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-1

8.2 Flash Memory Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-1

DS732UM7 Copyright 2008 Cirrus Logic, Inc. v

CS4953xx Hardware Users Manual

8.2.1 Flash Controller Interface...............................................................................................8-2

8.3 SDRAM/Flash Controller Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-2

8.3.1 SDRAM/Flash Interface Signals.....................................................................................8-2

8.3.2 Configuring SDRAM/Flash Parameters..........................................................................8-4

Chapter 9. System Integration..............................................................................9-1

9.1 Typical Connection Diagrams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-1

9.2 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-10

9.2.1 Power and Ground .......................................................................................................9-10

9.2.1.1 Power...........................................................................................................9-10

9.2.1.2 Ground.........................................................................................................9-11

9.2.1.3 Decoupling...................................................................................................9-11

9.2.2 PLL Filter......................................................................................................................9-11

9.2.2.1 Analog Power Conditioning .........................................................................9-11

9.2.3 PLL...............................................................................................................................9-12

9.3 Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-12

9.4 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-13

9.4.1 Operational Mode.........................................................................................................9-13

9.5 144-Pin LQFP Pin Assigments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-15

9.6 128-Pin LQFP Pin Assigments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-16

9.7 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-17

9.8 Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-21

Figures

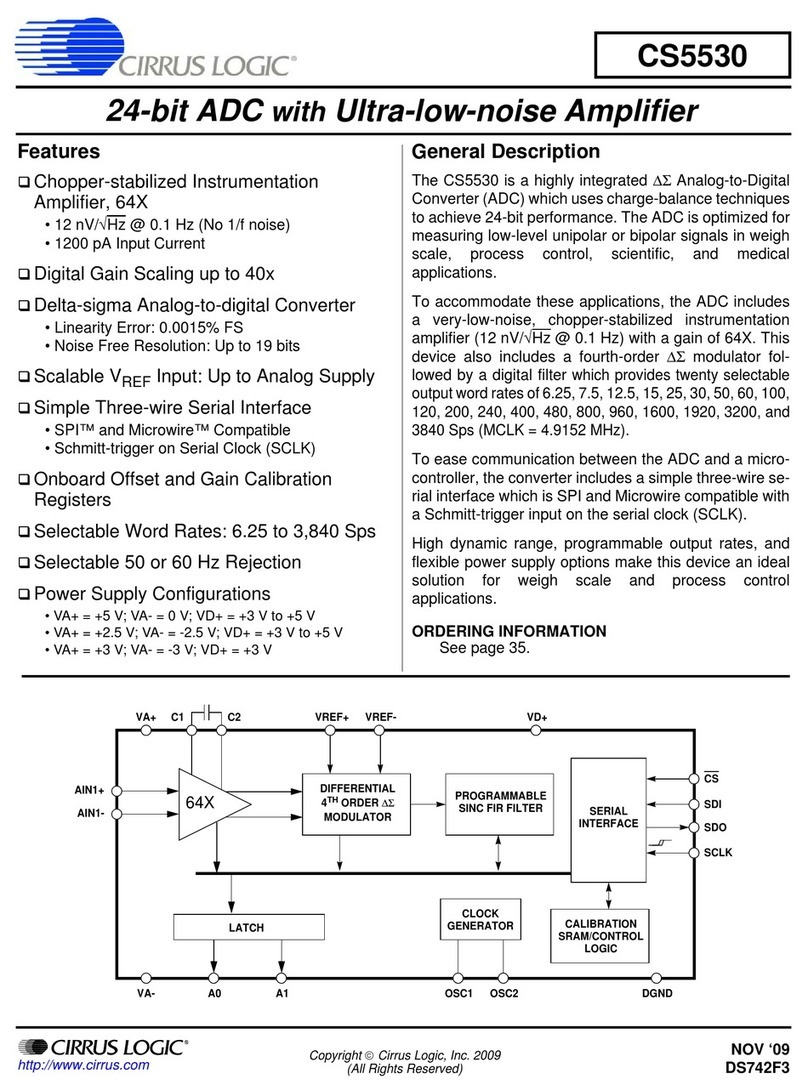

Figure 1-1. CS4953xx Chip Functional Block Diagram.................................................................................1-2

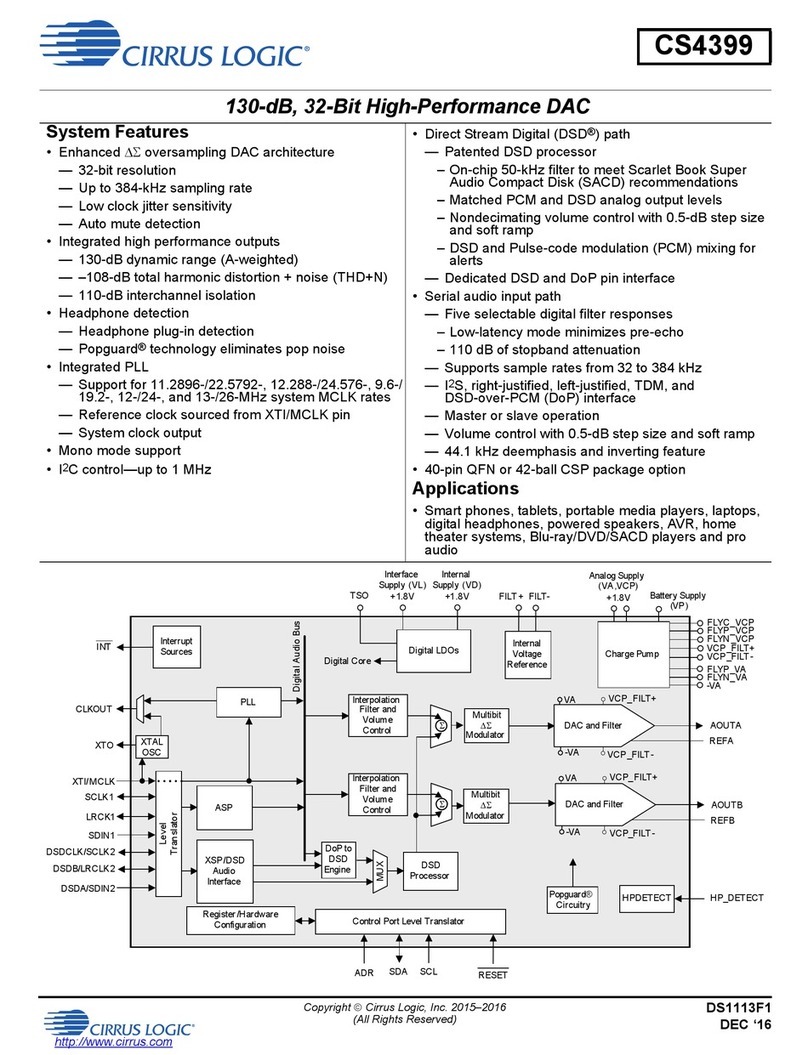

Figure 2-1. Operation Mode Block Diagrams................................................................................................2-2

Figure 2-2. Host Controlled Master Boot.......................................................................................................2-5

Figure 2-3. Slave Boot Sequence .................................................................................................................2-8

Figure 2-4. Master Boot Sequence Flowchart.............................................................................................2-13

Figure 2-5. Soft Boot Sequence Flowchart .................................................................................................2-15

Figure 2-6. Soft Boot Example Flowchart....................................................................................................2-16

Figure 3-1. Serial Control Port Internal Block Diagram .................................................................................3-2

Figure 3-2. Block Diagram of I2C System Bus ..............................................................................................3-3

Figure 3-3. I2C Start and Stop Conditions.....................................................................................................3-4

Figure 3-4. I2C Address with ACK and NACK...............................................................................................3-5

Figure 3-5. Data Byte with ACK and NACK ..................................................................................................3-6

Figure 3-6. Repeated Start Condition with ACK and NACK..........................................................................3-6

Figure 3-7. Stop Condition with ACK and NACK...........................................................................................3-7

Figure 3-8. I2C Write Flow Diagram ..............................................................................................................3-8

Figure 3-9. I2C Read Flow Diagram............................................................................................................3-10

Figure 3-10. Sample Waveform for I2C Write Functional TIming................................................................3-12

vi Copyright 2008 Cirrus Logic, Inc. DS732UM7

CS4953xx Hardware Users Manual

Figure 3-11. Sample Waveform for I2C Read Functional TIming................................................................3-12

Figure 3-12. SPI Serial Control Port Internal Block Diagram ......................................................................3-13

Figure 3-13. Block Diagram of SPI System Bus..........................................................................................3-15

Figure 3-14. Address and Data Bytes .........................................................................................................3-16

Figure 3-15. SPI Write Flow Diagram..........................................................................................................3-17

Figure 3-16. SPI Write Flow Diagram..........................................................................................................3-17

Figure 3-17. SPI Read Flow Diagram .........................................................................................................3-18

Figure 3-18. Sample Waveform for SPI Write Functional Timing................................................................3-20

Figure 3-19. Sample Waveform for SPI Read Functional Timing ...............................................................3-20

Figure 3-20. Sample Waveform for SPI Read Functional Timing ...............................................................3-20

Figure 5-1. DAI Port Block Diagram..............................................................................................................5-2

Figure 5-2. I2S format (Rising Edge Valid SCLK)..........................................................................................5-4

Figure 5-3. Left-justified Format (Rising Edge Valid SCLK)..........................................................................5-4

Figure 6-1. DSD Port Block Diagram ............................................................................................................6-2

Figure 7-1. DAO Block Diagram....................................................................................................................7-2

Figure 7-2. I2S Compatible Serial Audio Formats (Rising Edge Valid...........................................................7-3

Figure 7-3. Left-justified Digital Audio Formats (Rising Edge Valid DAO_SCLK) .........................................7-3

Figure 7-4. One-line Data Mode Digital Audio Formats ................................................................................7-4

Figure 8-1. SDRAM Interface Block Diagram................................................................................................8-1

Figure 9-1. LQFP-144, I2C Control, Serial FLASH, SDRAM, 7 DACs ..........................................................9-2

Figure 9-2. LQFP-144, SPI Control, Serial FLASH, SDRAM, 7 DACs..........................................................9-3

Figure 9-3. LQFP-144, SPI Control, Serial FLASH, SDRAM, 8 DACs..........................................................9-4

Figure 9-4. LQFP-144, I2C Control, Parallel Flash, SDRAM, 8 DACs..........................................................9-5

Figure 9-5. LQFP-128, SPI Control, Parallel Flash, SDRAM, 8 DACs..........................................................9-6

Figure 9-6. LQFP-128, I2C Control, Serial FLASH, DSD Audio Input, SDRAM, 7 DACs..............................9-7

Figure 9-7. LQFP-144, SPI Control, Serial FLASH, DSD Audio Input, SDRAM, 7 DACs.............................9-8

Figure 9-8. LQFP-144, SPI Control, Serial FLASH, DSD Audio Input, SDRAM, 7 DACs.............................9-9

Figure 9-9. PLL Filter Topology...................................................................................................................9-12

Figure 9-10. Crystal Oscillator Circuit Diagram...........................................................................................9-13

Figure 9-11. 144-Pin LQFP Pin Layout .......................................................................................................9-15

Figure 9-12. 128-Pin LQFP Pin Layout .......................................................................................................9-16

Tables

Table 2-1. Operation Modes..........................................................................................................................2-3

Table 2-2. SLAVE_BOOT message for CS4953xx.....................................................................................2-10

Table 2-3. HCMB_PARALLEL message for CS4953xx..............................................................................2-10

DS732UM7 Copyright 2008 Cirrus Logic, Inc. vii

CS4953xx Hardware Users Manual

Table 2-4. HCMB_I2C message for CS4953xx...........................................................................................2-11

Table 2-5. HCMB_SPI message for CS4953xx ..........................................................................................2-11

Table 2-6. GPIO Pins Available as EE_CS in HCMB..................................................................................2-12

Table 2-7. SOFT_RESET message for CS4953xx .....................................................................................2-12

Table 2-8. Boot Read Messages from CS4953xx.......................................................................................2-12

Table 2-9. Boot Command Messages for CS4953xx..................................................................................2-13

Table 2-10. SOFTBOOT Message..............................................................................................................2-14

Table 2-11. SOFTBOOT_ACK Message ....................................................................................................2-14

Table 3-1. Serial Control Port 1 I2C Signals..................................................................................................3-3

Table 3-2. Serial Control Port SPI Signals ..................................................................................................3-14

Table 5-1. Digital Audio Input Port ................................................................................................................5-1

Table 5-2. Bursty Data Input (BDI) Pins........................................................................................................5-3

Table 5-3. Input Data Format Configuration (Input Parameter A) .................................................................5-5

Table 5-4. Input SCLK Polarity Configuration (Input Parameter B)...............................................................5-7

Table 5-5. Input LRCLK Polarity Configuration (Input Parameter C) ............................................................5-7

Table 5-6. Input DAI Mode Configuration (Input Parameter D).....................................................................5-8

Table 6-1. DSDl Audio Input Port..................................................................................................................6-1

Table 7-1. Digital Audio Output (DAO1 & DAO2) Pins..................................................................................7-1

Table 7-2. Output Clock Mode Configuration (Parameter A) ........................................................................7-5

Table 7-3. DAO1 & DAO2 Clocking Relationship Configuration (Parameter B)............................................7-5

Table 7-4. Output DAO_SCLK/LRCLK Configuration (Parameter C) ...........................................................7-5

Table 7-5. Output Data Format Configuration (Parameter D).......................................................................7-7

Table 7-6. Output DAO_LRCLK Polarity Configuration (Parameter E).........................................................7-8

Table 7-7. Output DAO_SCLK Polarity Configuration (Parameter F) ...........................................................7-8

Table 7-8. S/PDIF Transmitter Pins ..............................................................................................................7-9

Table 7-9. S/PDIF Transmitter Config...........................................................................................................7-9

Table 7-10. DSP Bypass Config....................................................................................................................7-9

Table 8-1. SDRAM Interface Signals ............................................................................................................8-2

Table 8-2. SDRAM/Flash Controller Parameters ..........................................................................................8-4

Table 9-1. Core Supply Pins .......................................................................................................................9-10

Table 9-2. I/O Supply Pins ..........................................................................................................................9-10

Table 9-3. Core and I/O Ground Pins..........................................................................................................9-11

Table 9-4. PLL Supply Pins.........................................................................................................................9-11

Table 9-5. PLL Filter Pins............................................................................................................................9-12

Table 9-6. Reference PLL Component Values............................................................................................9-12

Table 9-7. DSP Core Clock Pins.................................................................................................................9-13

Table 9-8. Reset Pin....................................................................................................................................9-14

viii Copyright 2008 Cirrus Logic, Inc. DS732UM7

CS4953xx Hardware Users Manual

Table 9-9. Hardware Strap Pins..................................................................................................................9-14

Table 9-10. Pin Assignments ......................................................................................................................9-17

1-1 Copyright 2008 Cirrus Logic, Inc. DS732UM7

Overview

CS4953xx Hardware Users Manual

Chapter 1

Introduction

1.1 Overview

The CS4953xx is a programmable audio DSP that combines a programmable, 32-bit fixed-point general purpose

DSP with dedicated audio peripherals. Its audio-centric interfaces facilitate the coding of high-precision audio

applications and provide a seamless connection to external audio peripheral ICs.

The CS4953xx is a 32-bit RAM-based processor that provides up to 150 MIPS of processing power and includes all

standard codes in ROM. It has been designed with a generous amount of on-chip program and data RAM, and has all

necessary peripherals required to support the latest standards in consumer entertainment products. In addition,

external SDRAM and Flash memory interfaces can be used to expand the data memory. This device is suitable for a

variety of high-performance audio applications. These include:

• Audio/Video Receivers

• DVD Receivers

•StereoTVs

• Mini Systems

•ShelfSystems

• Digital Speakers

• Car Audio Head Units and Amplifiers

• Set-top Boxes

1.1.1 Chip Features

The CS4953xx includes the following features:

• Various Decoding/processing Standards • Customer Software Security Keys

• 12-channel Serial Audio Inputs • 16-channel PCM Output

• Dual 32-bit Audio DSP with Dual MAC • Dual S/PDIF Transmitters

• Large On-chip X,Y, and Program RAM • Two Serial Control Ports Using SPI™ or I2C®

Standards

• Supports SDRAM & Flash Memories • Digital Audio Input (DAI) Port for Audio Data

Delivery in I2S or LJ Format

• Parallel Control Using Motorola®or

Intel®Communication Standards

• GPIO Support for All Common Sub-circuits

Overview

CS4953xx Hardware Users Manual

DS732UM7 Copyright 2008 Cirrus Logic, Inc 1-2

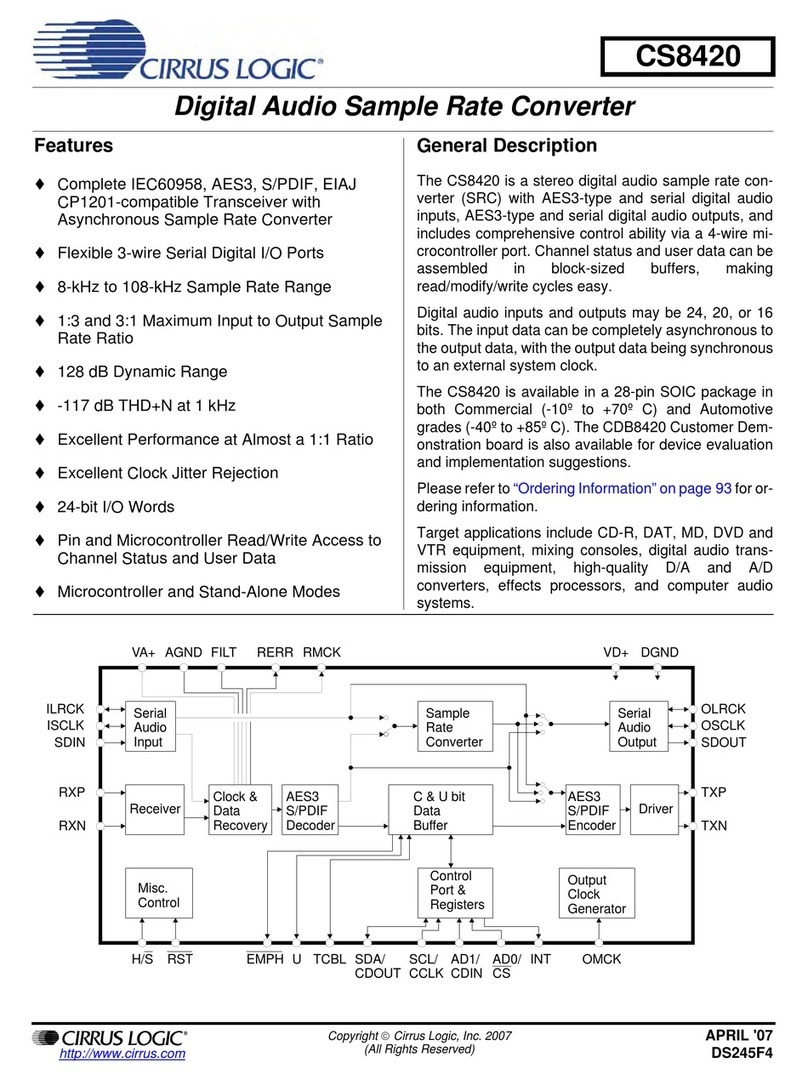

Figure 1-1 illustrates the functional block diagram for the CS4953xx chip.

Figure 1-1. CS4953xx Chip Functional Block Diagram

DAI

Controller

DMA Controller with 11 Stereo Channels

Programmable

Interrupt Controller

Peripheral

Bus

Controller

Memory Controller

Log/Exp

Security

Ext (64 bit)

DMA Bus

Peripheral Bus

Decryptor

32-bit Dual Datapath

DSP

with 72-bit

Accumulators

X

Y

PX

P

Y

64 bit Stereo Audio Output

Stereo Audio Output

Stereo Audio Output

ArbiterArbiter

Stereo Audio Output or

SPDIF Transmitter

DAO

Controller

ROM

SRAM

ROM

SRAM

ROM

SRAM

Timers

GPIOs

Clock Manager and PLL

Parallel Control Port

Serial Control Port

SDRAM Controller SRAM / FLASH Controller

Debug

Controller

DSPA

DSPB

DAO1

Stereo Audio Input/DSD

Stereo Audio Input/DSD

Stereo Audio Input/DSD

Stereo Audio Input/DSD

Stereo Audio Output

Stereo Audio Output

Stereo Audio Output

Stereo Audio Output or

SPDIF Transmitter

DAO

Controller

DAO2

DAI1

CS4953xx

Stereo Audio Input /

Bursty Data Input/DSD

Stereo Audio Input/DSD

DAI2

DAI

Controller

1-3 Copyright 2008 Cirrus Logic, Inc. DS732UM7

Overview

CS4953xx Hardware Users Manual

The CS4953xx supports the following post-processing application codes and/or modules:

• Dolby®Digital

•DTS-ES

™, DTS96/24™, DTS-ES96/24™ (Available only on the CS495313 product)

•THX

®Select, THX®Select 2™, THX®Ultra 2™

• Dolby Pro Logic®IIx

•SRS

®Circle Surround®

• Cirrus Extra Surround™

• Cirrus Original Multichannel Surround™

• Cirrus Original Surround™

•DTSNeo:6

™

• Tru-Surround XT®

• Dolby Headphone®, Dolby Headphone 2™

• Dolby Virtual Speaker®, Dolby Virtual Speaker 2™

• Crossbar Downmixer/Upmixer

• Bass Manager

• Parametric EQ

• Tone Control

• Intelligent Room Calibration 1 (IRC1)

• Intelligent Room Calibration 2 (IRC2)

• Delay

•PCM

•MPEG

• Signal Generator (SGEN)

•AAC

™

The above audio decoding/processing algorithms, post-processing application codes, and/or Cirrus Framework™

modules and the associated application notes are available through the Cirrus Software Licensing Program. Standard

post-processing code modules are only available to customers who qualify for the Cirrus Framework™CS4953xx

Family DSP Programming Kit. Please refer to the Related Documents section of the Framework™manual for

additional application note information.

The CS4953xx contains sufficient on-chip memory to support decoding of all major audio decoding algorithms

available today. The CS4953xx supports a glueless SDRAM/Flash interface for increased all-channel delays. The

memory interface also supports connection to an external 8- or 16-bit-wide EPROM or Flash memory for code

storage, thus allowing products to be field upgraded as new audio algorithms are developed.

This chip, teamed with the Cirrus certified decoder library, Cirrus digital interface products, and mixed-signal data

converters, enables the design of next-generation digital entertainment products.

Functional Overview of the CS4953xx Chip

CS4953xx Hardware Users Manual

DS732UM7 Copyright 2008 Cirrus Logic, Inc 1-4

1.2 Functional Overview of the CS4953xx Chip

The CS4953xx chip supports a maximum clock speed of 150 MHz in a 144-pin LQFP or 128-pin LQFP package. A

high-level functional description of the CS4953xx chip is provided in this section.

1.2.1 DSP Core

The CS4953xx DSP core is a pair of general purpose, 32-bit, fixed-point, fully programmable digital signal

processors that achieve high performance through an efficient instruction set and highly parallel architecture. The

device uses two’s complement fractional number representation, and employs busses for two data memory spaces

and one program memory space.

CS4953xx core enhancements include portability of the design, speed improvement, and improvements for

synthesis, verification, and testability. Each member of the CS4953xx family has different SRAM and ROM sizes.

Please refer to the CS4953xx data sheet for details.

1.2.2 Security Extension module

This module is a 64-bit extension module that allows the CS4953xx device to be placed in a secure mode where

decryption is activated via a 128-bit key. This key is written to the security extension in two 64-bit move

instructions. Secure mode is disabled by default, and must be explicitly enabled.

1.2.3 Debug Controller (DBC)

An I2C slave debug controller (DBC) is integrated within the CS4953xx DSP core. Two pins are reserved for

connecting a PC host to the debug ports on either DSP. The debug port consists of two modules, an I2C slave and a

debug master. The DBC master sends dedicated signals into the DSP core to initiate debug actions and it receives

acknowledge signals from the core to indicate the requested action has been taken. Basically, this interface allows

the DBC to insert instructions into the pipeline. The core will acknowledge the action when it determines the

pipeline is in the appropriate state for the inserted action to be taken.

1.2.4 Digital Audio Output (DAO1, DAO2) Controller

The CS4953xx has two Digital Audio Output (DAO) controllers, each of which contains 4 stereo output ports. One

port on each DAO can be used as a S/PDIF transmitter. The DAO ports can transmit up to 16 channels of audio

sample data in I2S-compatible format. The audio samples are stored in 16 channel buffers which are 32 bits wide.

Four of the channels can also serve as output buffers for the two S/PDIF transmitters. The O/S can dedicate DMA

channels to fill the DAO data buffers from memory. DAO control is handled through the peripheral bus.

1.2.5 Digital Audio Input (DAI1) Controller

The CS4953xx Digital Audio Input (DAI) controller has four stereo input ports and DAI control is handled through

the peripheral bus. Each DAI pin can be configured to load audio samples in a variety of formats. In addition to

accepting multiple formats, the DAI controller has the ability to accept multiple stereo channels on a single

DAI1_DATAx pin. All four DAI pins are slaves and normally share the same serial input clock pins (DAI1_SCLK

and DAI1_LRCLK). Pins DAI1_DATA[3:0] may also be reconfigured to use the DAO serial input clock pins

(DAOx_SCLK and DAOx_LRCLK). A single global configuration register provides a set of enable bits to ensure

that ports may be started synchronously.

1.2.6 Compressed Data Input / Digital Audio Input (DAI2) Controller

The DAI2 controller has one input port and its own SCLK and LRCLK and can be used for accepting PCM data in

the same way as DAI1, but is used primarily for the delivery of compressed data. When configured for compressed

data input, custom internal hardware is enabled that off-loads some pre-processing of the incoming stream to help

maximize the MIPS available in the DSP core for user-customized applications.

1-5 Copyright 2008 Cirrus Logic, Inc. DS732UM7

Functional Overview of the CS4953xx Chip

CS4953xx Hardware Users Manual

1.2.7 Direct Stream Digital®(DSD) Controller

The CS4953xx also has a DSD controller which allows the DSP to be integrated into a system that supports SACD

audio. The DSD controller pins are shared with the DAI1 and DAI2 ports. The DSD port consists of a bit clock

(DSD_CLK) and six DSD data inputs (DSD[5:0]).

1.2.8 General Purpose I/O

A 32-bit general-purpose I/O (GPIO) port is provided on the CS4953xx chip to enhance system flexibility. Many of

the functional pins can be used for either GPIO or peripherals.

Each GPIO pin can be individually configured as an output, an input, or an input with interrupt. A GPIO interrupt

can be triggered on a rising edge (0-to-1 transition), falling edge (1-to-0 transition), or logic level (either 0 or 1).

Each pin configured as an input with interrupt can be assigned its own interrupt trigger condition. All GPIOs share a

common interrupt vector.

1.2.9 Parallel Control Port (Motorola/Intel Standards)

The CS4953xx parallel control port allows an external device such as a microcontroller to communicate with the

CS4953xx chip using either a Motorola®-type or Intel®-type parallel communication standard. Only one of the two

communication modes can be selected at a time. For external device-control purposes, the CS4953xx is in slave

mode for all communication protocols, although it can request the external device to perform a read. The parallel

control port supports direct memory access (DMA) and can be used simultaneously with the CS4953xx serial

control port.

The parallel control port communication mode selection occurs as the CS4953xx exits a reset condition. The rising

edge of the RESET pin samples the HS[4:0] pins to determine the communication mode and boot style.

Configuration of the three address input pins A[2:0] allows one of the parallel configuration registers to be selected

and accessed.

1.2.10 Serial Control Ports (SPI™or I2C®Standards)

The CS4953xx has two serial control ports (SCP) that support SPI™and I2C®Master/Slave communication modes.

The serial control port allows external devices such as microcontrollers to communicate with the CS4953xx chip

through either I2C®or SPI™serial communication standards and can be configured as either a master or a slave.

The CS4953xx SPI and I2C serial communication modes are identical from a functional standpoint. The main

difference between the two is the protocol being implemented between the CS4953xx and the external device. In

addition, the I2C slave has a true I2C mode that utilizes data flow mechanisms inherent to the I2C protocol. If this

mode is enabled, the I2C slave will hold SCP1_CLK low to delay a transfer as needed.

By default, SCP1 is configured as a slave for external device-controlled data transfers. As a slave, it cannot drive the

clock signal nor initiate data transfers.

By default, SCP2 is configured as a master to access a serial FLASH/EEPROM for either booting the DSP or

retrieving configuration information. As a master, it can drive the clock signal at up to 1/2 of the DSP’s core clock

speed.

The CS4953xx has two additional serial communication pins not specified in either the I2C or SPI specification. The

port uses the SCP1_IRQ pin to indicate that a read message is ready for the host. The port uses the SCP1_BSY pin to

warn the host to pause communication.

A serial control port can be operated simultaneously with the CS4953xx parallel control port.

Functional Overview of the CS4953xx Chip

CS4953xx Hardware Users Manual

DS732UM7 Copyright 2008 Cirrus Logic, Inc 1-6

1.2.11 SDRAM Controller

The CS4953xx supports a glueless external SDRAM interface to extend the data memory of the DSP during

runtime. The SDRAM controller provides 2-port access to X and Y memory space, a quad-word read buffer, and a

double-buffered quad-word write buffer. One SDRAM controller port is dedicated to P memory space and the

second port is shared by X and Y memories. The X/Y port has dual write buffers and a single read buffer, and the P

memory port has a single read buffer. One of these buffers is four 32-bit words (128 bits). Every “miss” to the read

buffer will cause the SDRAM controller to burst eight 16-bit reads on the SDRAM interface. The SDRAM

controller supports SDRAMs from 2 MB to 64 MB with various row, bank, and column configurations. The

SDRAM controller runs synchronous to HCLK, the global chip clock.

1.2.12 Flash Controller

The CS4953xx supports a glueless external Flash interface that allows autoboot from a parallel Flash or EEPROM

device extending data memory and/or program memory during DSP runtime. Flash can be accessed using 8-bit, 16-

bit, and 32-bit data modes (1-byte, 2-byte, and 4-byte words) and using an 8-bit or 16-bit data bus, where the word

width is the number of bytes per transfer, and the data bus size is the width of the physical interface to Flash.

Separate chip select pins allow Flash devices to be connected without additional chip select logic. Thus, the interface

supports up to 512k x 16 bits of Flash. The external Flash interface serially accesses the X, Y, and P memory spaces

on the CS4953xx chip.

1.2.13 DMA Controller

The DMA controller contains 12 stereo channels. The O/S uses 11 stereo channels, 6 for the DAO (2 are for the S/

PDIF transmitters), 4 for the DAI, and one for the parallel control port. The addition of the DMA channel for the

parallel control port allows compressed audio data to be input over this port. The DMA block is able to move data to/

from X or Y memory, or alternate between both X and Y memory. The DMA controller moves data to/from X and/or

Y memory opportunistically (if the core is not currently accessing that particular memory space during the current

cycle). The DMA controller has a “Dead Man’s” timer so that if the core is running an inner loop and accessing

memory every cycle, the DMA controller can interrupt the core to run a DMA cycle.

1.2.14 Timers

A 32-bit timer block runs off the CS4953xx DSP clock. The timer count decrements with each clock tick of the DSP

clock when the timer is enabled. When the timer count reaches zero, it is re-initialized, and may be programmed to

generate an interrupt to the DSP.

1.2.15 Clock Manager and PLL

The CS4953xx Clock Manager and PLL module contains an Analog PLL, RTL Clock Synthesizer, and Clock

Manager. The Analog PLL is a customized analog hard macro that contains the Phase Detector (PD), Charge Pump,

Loop Filter, VCO, and other non-digital PLL logic. The Clock Synthesizer is a digital design wrapper around the

analog PLL that allows clock frequency ranges to be programmed. The Clock Manager is a digital design wrapper

for the Clock Synthesizer that provides the logic (control registers) necessary to meet chip clocking requirements.

The Clock Manager and PLL module generates two master clocks:

• HCLK - global chip clock (clocks the DSP core, internal memories, SDRAM, Flash, and all peripherals)

• OVFS - oversampled audio clock. This clock feeds the DAO block which has dividers to generate the

DAO_MCLK, DAO_SCLK, and DAO_LRCLK.

The Clock Manager has the ability to bypass the PLL so that the HCLK will run directly off the PLL Reference

Clock (REFCLK). While operating in this mode, the OVFS clock can still be divided off the VCO so the PLL can be

tested.

1-7 Copyright 2008 Cirrus Logic, Inc. DS732UM7

Functional Overview of the CS4953xx Chip

CS4953xx Hardware Users Manual

1.2.16 Programmable Interrupt Controller

The Programmable Interrupt Controller (PIC) forces all incoming interrupts to be synchronized to the global clock,

HCLK. The PIC provides up to 16 interrupts to the DSP Core. The interrupts are prioritized with interrupt 0 as the

highest priority and interrupt 15 as the lowest priority. Each interrupt has a corresponding interrupt address that is

also supplied to the DSP core. The interrupt address is the same as the IRQ number (interrupt 0 uses interrupt

address 0 and interrupt 15 uses interrupt address 15). Both an enable mask and a run mask are provided for each

interrupt. The enable mask allows the enabled interrupts to generate a PIC_REQ signal to the DSP core, and the run

mask allows the enabled interrupts to generate a PIC_CLR, thereby bringing the core out of its halt state when it

accepts the interrupt.

§§1

1. The “§§” symbol is used throughout this manual to indicate the end of the text flow in a chapter.

Functional Overview of the CS4953xx Chip

CS4953xx Hardware Users Manual

DS732UM7 Copyright 2008 Cirrus Logic, Inc 1-8

2-1 Copyright 2008 Cirrus Logic, Inc. DS732UM7

CS4953xx Hardware Users Manual

Chapter 2

Operational Modes

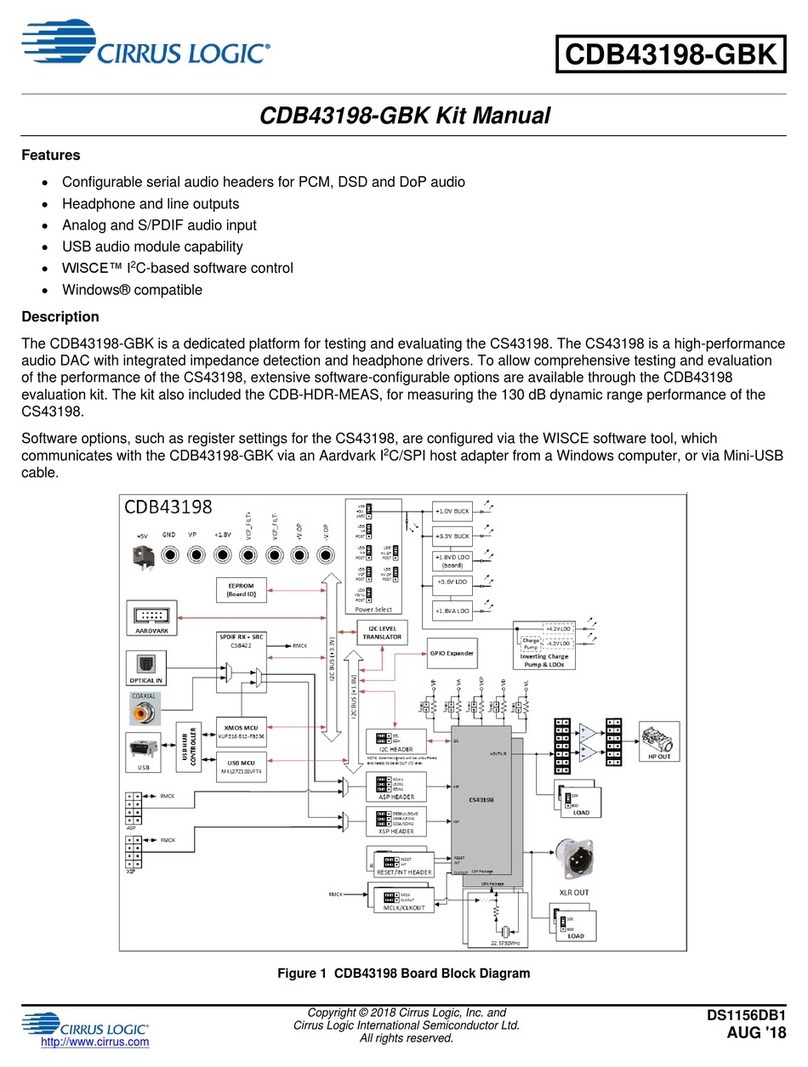

The CS4953xx has several operational modes that can be used to conform to many system configurations. The

operational modes for the CS4953xx specify both the communication mode and boot mode. This chapter discusses

the selection of operational modes, booting procedures and performing a soft reset.

The CS4953xx can be either a slave device or a master device for the boot procedure. In Master Boot Mode, the

CS4953xx is the master boot device and can automatically boot the application code from either serial or parallel

external ROM (the slave boot device). In Slave Boot Mode, the CS4953xx is the slave boot device and requires the

system host controller (the master boot device) to determine how to boot the application code. The system host

controller can either load the application code or the host can direct the CS4953xx to boot application code from

serial or parallel external ROM. See Figure 2-1 on page 2-2.

Thus, there are three boot modes for the CS4953xx:

• Master Boot (From serial or parallel external ROM)

• Slave Boot (Using SPI, I2C, Intel, Motorola, or Multiplexed Intel protocols.)

• Host Controlled Master Boot (serial or parallel external ROM)

When the CS4953xx is configured for an operational mode where it is the slave boot device, one of the below

communication modes must be specified by the host controller (that is, the master boot device). These

communication modes are described in detail in Chapter 3, "Serial Control Port" and Chapter 4, "Parallel Control

Port". Please see these chapters for block diagrams and flowcharts depicting each of the CS4963x boot modes.

CS4953xx Hardware Users Manual

DS732UM7 Copyright 2008 Cirrus Logic, Inc 2-2

Figure 2-1. Operation Mode Block Diagrams

Slave Boot

System Host

Controller

(Master) CS4953xx

(Slave)

Control Bus

CS4953xx

(Master)

External ROM

(Slave)

External

Memory Bus

Master Boot

(Not currently supported by O/S)

CS4953xx

(Slave)

External ROM /

Ext. Serial Flash

Parallel

Memory Bus /

SCP2

System Host

Controller

(Master)

Control Bus

Host Controlled Master Boot

(Recommended for most systems)

2-3 Copyright 2008 Cirrus Logic, Inc. DS732UM7

Operational Mode Selection

CS4953xx Hardware Users Manual

2.1 Operational Mode Selection

The operational mode for the CS4953xx is selected by the values of the HS[4:0] pins on the rising edge of RESET.

This value determines the communication mode used until the part is reset again. This value also determines the

method for loading application code. The table below shows the different operational modes and the HS[4:0] values

for each mode.

1. In I2C master mode, the Image Start address (0x0) is sent as a 16-bit value, with the default I2C address of 0x50, I2C clock

frequency = Fdclk /72.

2. SPI master mode 1 is to support the legacy 16-bit SPI EEPROM. The following defaults are used: SPI Command Byte

0x03, Image Start address 0x0 is sent as a 16-bit value, no dummy bytes, SPI clock frequency = Fdclk /4.

3. In SPI Master mode 2, the following defaults are used: SPI Command Byte 0x68, Image Start address 0x0 is sent as a 24-

bit value, 4 dummy bytes sent following the address (and before reading image data), SPI clock frequency = Fdclk /2.This

mode supports the Atmel SPI Flash memory.

4. In SPI Master mode 3, the following defaults are used: SPI command byte 0x03, Image Start address 0x0 is sent as a 24-bit

value, no dummy bytes, SPI clock frequency = Fdclk / 2. This mode supports the ST SPI EEPROM devices.

5. For all SPI Master boot modes, by default GPIO20 is used as EE_CS, but the HCMB message can be configured to select

an alternate pin for EE_CS.

6. For Flash Master modes, the following defaults are used: clock ratio=1:1, Endian Mode = little-endian, Chip Select polarity

= active-low, 0-cycle delay from CS/Address Change to Output Enable, 4-cycle delay from CS to Read Access.

7. Master Boot Modes are currently not supported by the O/S.

8. Fdclk is specified in the CS4953xx data sheet.

2.2 Slave Boot Procedures

When the CS4953xx is the slave boot device, the system host controller (as the master boot device) must follow an

outlined procedure for correctly loading application code. The two methods of slave boot for the CS4953xx, slave

boot and host-controlled master boot are described in this section. Each of these methods requires the system host

controller to send messages to, and read back messages from, the CS4953xx. These messages have been outlined in

Section 2.2.3 "Boot Messages" on page 2-10.

The CS4953xx has different .uld files (overlays) for certain processing tasks. Slave booting the CS4953xx requires

loading multiple overlays - differing from previous Cirrus Logic Audio DSP families (this is, CS493xx, CS494xxx).

Please refer to AN288, “CS4953xx Firmware User’s Manual” regarding more information on the breakdown of

processing tasks for each overlay.

Table 2-1. Operation Modes

HS[4:0] Mode Boot Master

Device Boot Slave Device

X0000Master SCP1 I2CCS4953xx I2C External ROM1,8

X 1 0 0 0 Master SCP1 SPI1 CS4953xx SPI (Mode 1) External ROM2, 5, 7, 8

X 0 0 0 1 Master SCP1 SPI2 CS4953xx SPI (Mode 2) External ROM3, 5, 7, 8

X 1 0 0 1 Master SCP1 SPI3 CS4953xx SPI (Mode 3) External ROM4, 5, 7, 8

X 0 0 1 0 Master 8-bit Flash CS4953xx 8-bit External ROM6

X 1 0 1 0 Master 16-bit Flash CS4953xx 16-bit External ROM6

XX1 0 0 Slave/HCMB SCP1 I2CSystem Host CS4953xx

X X 1 0 1 Slave/HCMB SCP1 SPI System Host CS4953xx

X X 1 1 0 Slave/HCMB PCP Intel System Host CS4953xx

X X 1 1 1 Slave/HCMB PCP Motorola System Host CS4953xx

X X 0 1 1 Slave/HCMB PCP Mux System Host CS4953xx

Slave Boot Procedures

CS4953xx Hardware Users Manual

DS732UM7 Copyright 2008 Cirrus Logic, Inc 2-4

Pseudocode and flowcharts will be used to describe each of these boot procedures in detail. The flow charts use the

following messages:

•Write_*–

Write to CS4953xx

• Read_* – Read from CS4953xx

Please note that * above can be replaced by SPI™, I2C®, Intel®, Multiplexed Intel®, or Motorola®depending on the

mode of host communication. For each case, the general download algorithm is the same. The system designer

should also refer to the control port sections of this document in Chapter 3, "Serial Control Port"and Chapter 4,

"Parallel Control Port" for the details of when writing to and reading from the CS4953xx is valid.

One feature that is of special note – the entire boot procedure for the CS4953xx can be made of a combination of

slave boot and host-controlled master boot procedures. An example can be seen in Figure 2-3 on page 8.

After completing the full download to the CS4953xx, a KICK START message is sent to cause the application code

begin execution. Please note that it takes time to lock the PLL and initialize the SDRAM interface when initially

booting the DSP. Typically this time is less than 200 ms. If a message is sent to the DSP during this time, the

SCP1_BSY pin will go low to indicate that the DSP is busy. Any messages sent when the SCP1_BSY pin is LOW

will be lost. If the SCP1_BSY pin stays LOW longer than 200 ms the host must reboot the DSP.

2.2.1 Host Controlled Master Boot

The Host Controlled Master Boot (HCMB) procedure is a sequence where the system host controller instructs the

CS4953xx to boot application code from either the external memory interface (ROM or Flash), or the serial control

interface (serial SPI Flash/EEPROM or I2C EEPROM). The system host controller can communicate with the

CS4953xx via SPI™, I2C®, or one of the three parallel formats (Intel®, Multiplexed Intel®, or Motorola®). The

external memory start address of the code image, as well as the data rate, are specified by the host by the

HCMB_<MODE> message. These messages are defined in Section 2.2.3 "Boot Messages" on page 2-10.

Table of contents

Other Cirrus Logic Media Converter manuals