H_D#35

D32

*SCS751V-40

AC

H_SMI#

R303 10K_04

H_D#51

H_THERMDA

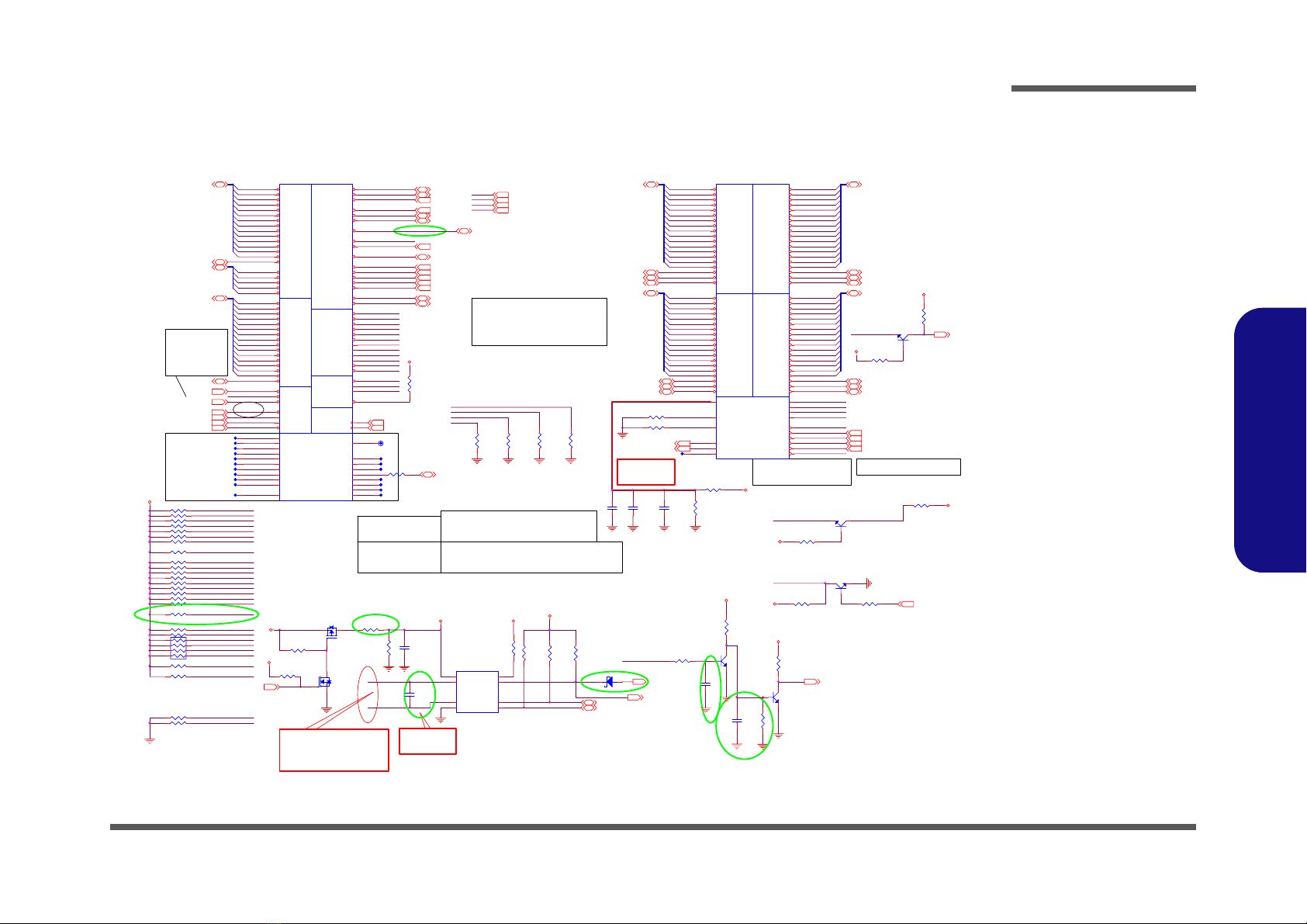

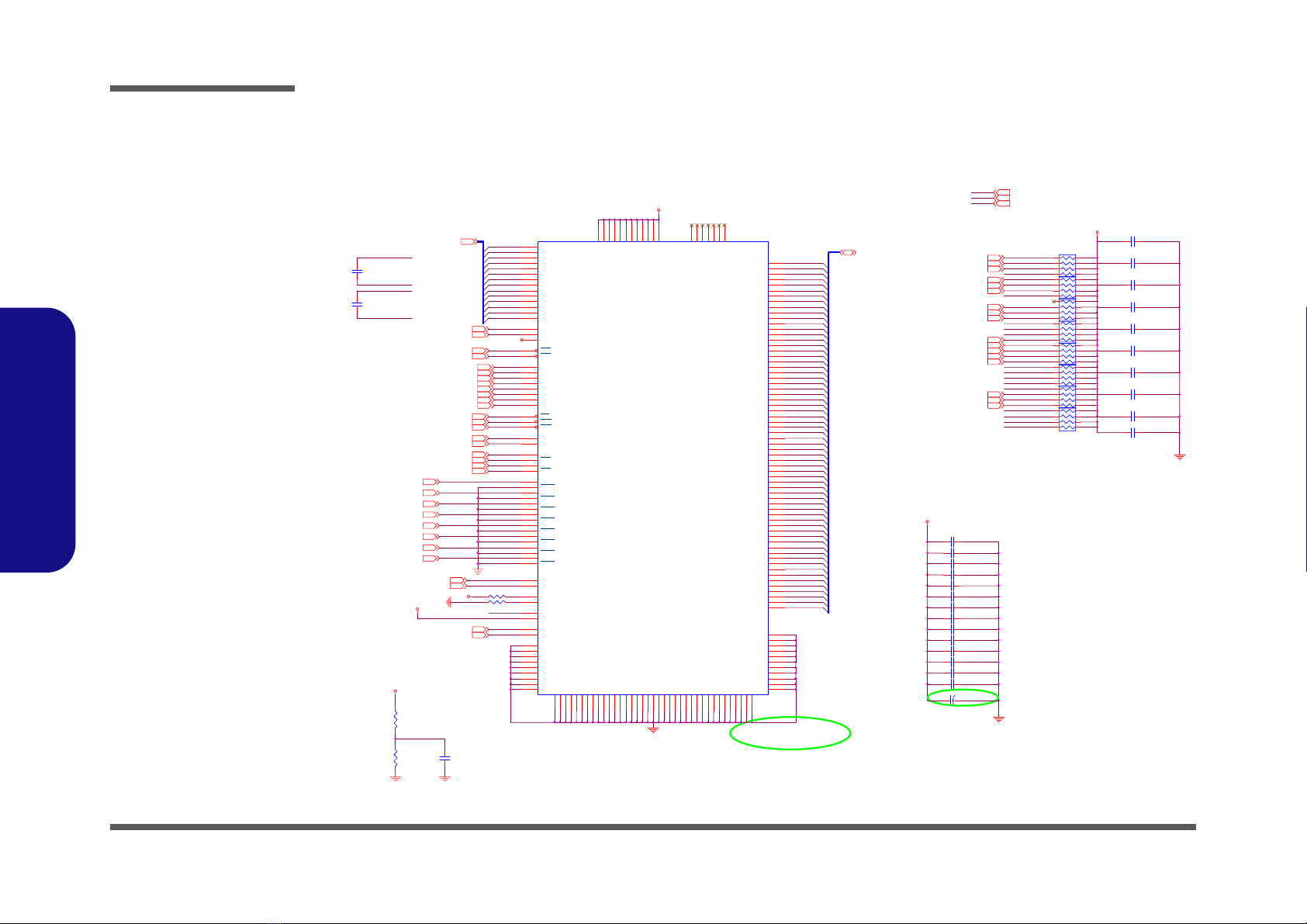

If PROCHOT# is not used, it must be pull-up 56

Ohm to Vccp; if PROCHOT# is routed between CPU,

IMVP6 VR & GMCH, Rtt has to be 75ohm+-5%

Layout Note:

+VCC P

R23 200 _04

H_RS#1 4

FERR#

H_A#18

H_A#14

H_A#21

R26 10K_04

H_DPWR# 4

R575 * 0_04

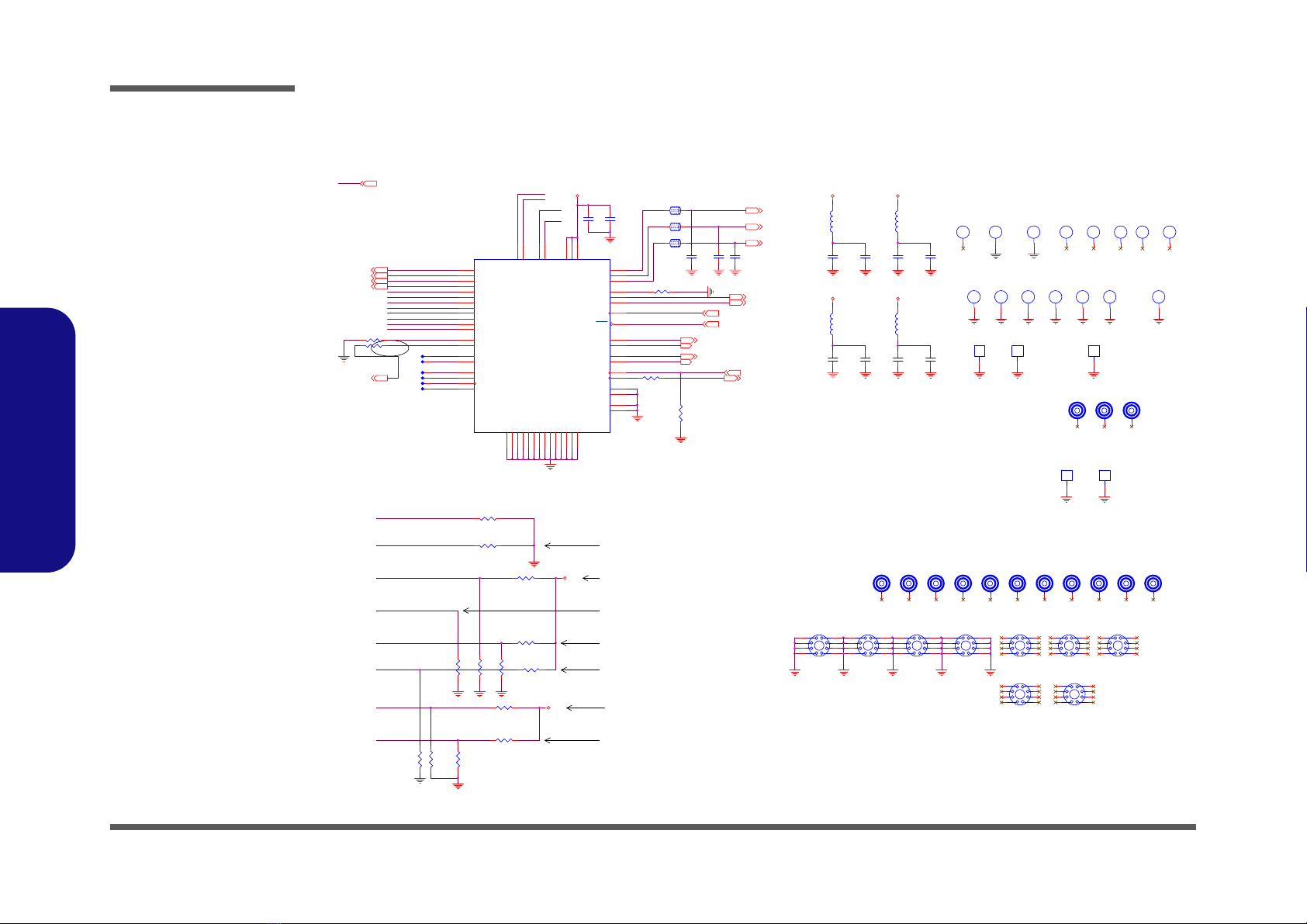

Layout Note:

COMP0, COMP2: 0.5" Max, Zo=27.4 Ohms

COMP1, COMP3: 0.5" Max, Zo=55 Ohms

Best estimate is 18 mils wide trace

for outer layers and 14 mils wide

trace if on internal layers.

H_D#60

H_D#57

H_DPRSLPVR

+2. 5VS 10, 12, 13 ,14, 15, 21 ,2 6, 28, 29

H_D#12

CLK_CPU_BCLK 10

H_INTR15

H_A#22

H_CPURST#

H_INTR

R326

100K_04

+V CC P

H_D#40

COMP2

H_BPM0#

Layout Note:

ITP_DBRST#

H_D#21

C469

10u/ 10 V_08

R581

*6.8K_04

+VDD3

H_A#3

H_HIT# 4

H_D#53

R47 51_ 1%_06

H_BREQ0# 4

H_PWRGD

H_A#15

H_REQ#0

H_A#20

R323

4.7K_04

CPU_GTLREF

H_D#6

H_D#17

H_PSI#

R546 150_04

A#[32-39],

APM#[0-1]:

Leave escape

routing on

for future

functionality

H_D#20

R321 0_06

R315 10K_04

H_IERR#

H_D#9

H_D#36

H_A#24

RN 2 2 20_06_ 8P4R

8 1

7 2

6

5

3

4

H_PREQ#

H_INTR

H_D#8

Within 2.0" of the CPU

R18 75_ 1%_06

T31

R299 150_04

+3VS

H_D#7

R17 680 _1%_06

C481

0. 01u/ 25 V_04

H_CPUSLP# 15

COMP3

H_DSTBP#3 4

H_D#41

H_D#52

H_D#15

H_D#10

H_D#19

H_REQ#1

H_A#30

R67 150 _04

H_ADSTB#04

H_A#27

R301 150_04

H_DSTBN#14

Layout Note:

0.5" max,

Zo= 55 Ohms

+V C CP

H_D#34

H_D#54

No stub on H_STPCLK# test

point

C469 CLOSE TO U19.

H_DSTBN#04

H_TDO

H_D#28

H_PRDY#

R16 54. 9_1%_06

R547 150_04

+V C CP

H_IGNNE#15

H_A20M#

H_A#19

H_INIT#

+VCC_THRM

H_REQ#[4:0]4

H_TRDY# 4

R65 75_ 1%_06

R302 150_04

H_DSTBP#14

H_DSTBP#2 4

+VCCP 3,4,10,15,28,29

COMP2

H_THERMDC

R341 51 _1%_06

R304

10K_ 06

R13 10K_04

H_DSTBP#04

H_RS#2 4

+VDD3 15,20,21,26,27,30

H_PRDY#

R286

27.4_1%_06

H_D#31

R25 10K _04

H_D#23

H_D#22

H_D#4

H_DBI#3 4

H_NMI15

H_D#[63:0]4

H_D#61

+VCC P

H_SMI #15

PM_DPRSLPVR 15,28

H_TRST#

H_PREQ#

H_DPRSLPVR

H_BPM3#

H_D#42

H_A#12

H_REQ#4

[13]

+3VS 6, 7, 8, 10, 11,1 2, 13, 14, 15 ,16 ,1 7,19 ,2 1,2 2, 24, 25, 26, 28, 29

H_CPUSLP#

H_D#55

R310 51_1%_04

Near to

F75383M

H_D#16

PM_THRMTRIP#

H_A#28

H_A20M#15

H_DPSLP# 15

H_D#33

COMP1

H_A#7

R340 * 1K_04

H_ADSTB0# 4

FERR#

PSI#

C717

*0.1u/16V_04

H_LOCK# 4

H_D#32

H_D#26

RESERVED

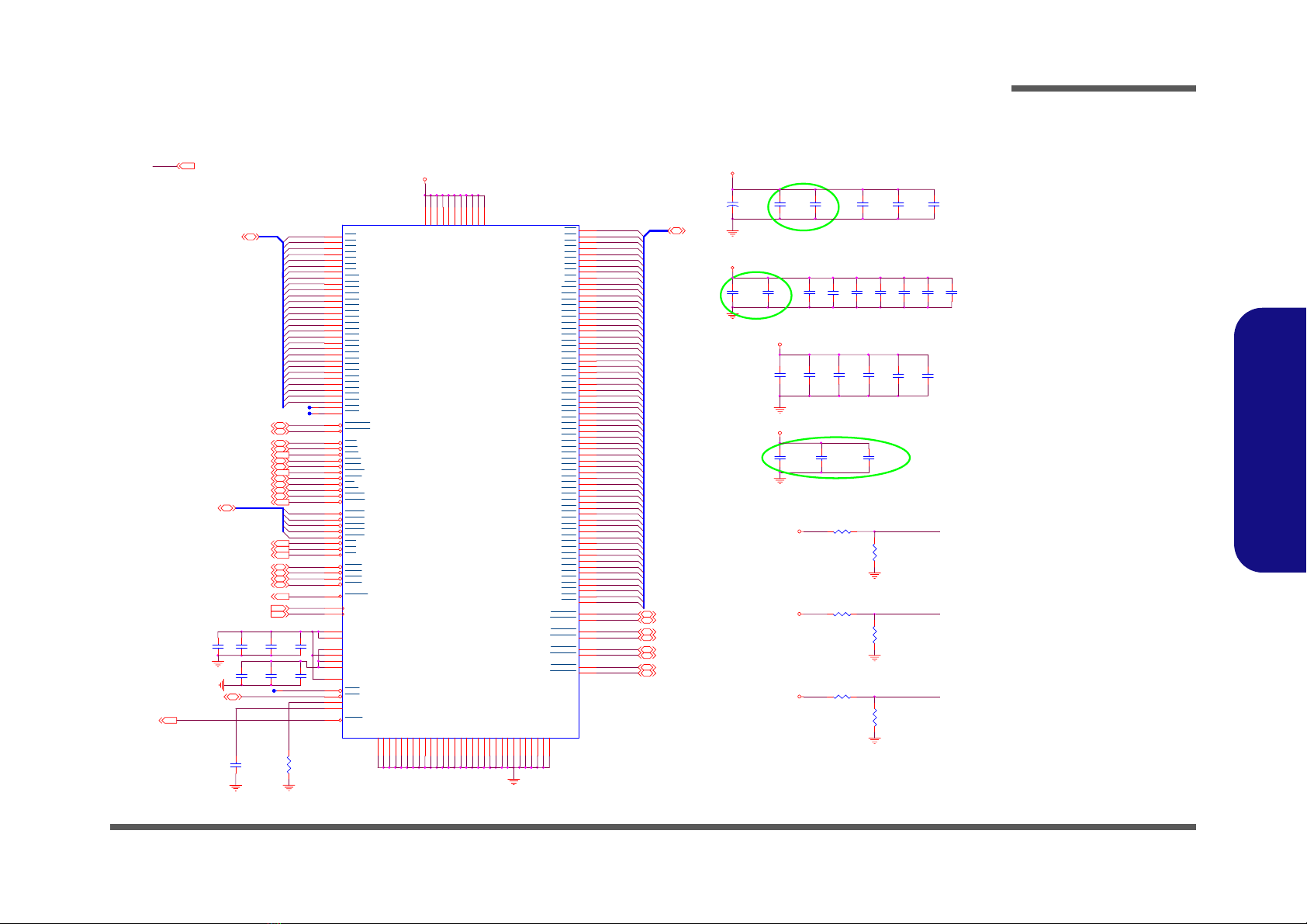

ADDR GROUP 0

CONTROL

XDP/ITP SIGNALS

THERMH CLK

JSKT1A

PZ47913-2741-01

J4

L4

M3

K5

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

L2

K3

H2

K2

J3

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

B25

T22

D2

F6

D3

C1

AF1

D22

C23

C24

A22

A21

D21

A24

A25

C7

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

G6

E4

B1

F3

F4

G3

G2

D20

B3

H4

F1

H5

F21

E1

H1

E2

G5

A[ 3] #

A[ 4] #

A[ 5] #

A[ 6] #

A[ 7] #

A[ 8] #

A[ 9] #

A[ 10] #

A[ 11] #

A[ 12] #

A[ 13] #

A[ 14] #

A[ 15] #

A[ 16] #

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[ 17] #

A[ 18] #

A[ 19] #

A[ 20] #

A[ 21] #

A[ 22] #

A[ 23] #

A[ 24] #

A[ 25] #

A[ 26] #

A[ 27] #

A[ 28] #

A[ 29] #

A[ 30] #

A[ 31] #

ADSTB[1]#

A20M#

FERR #

IGNNE#

STPC LK#

LINT0

LINT1

SMI#

RSVD[01]#

RSVD[02]#

RSVD[03]#

RSVD[04]#

RSVD[05]#

RSVD[06]#

RSVD[07]#

RSVD[08]#

RSVD[09]#

RSVD[10]#

RSVD[11]#

RSVD[12]#

RSVD[13]#

RSVD[14]#

RSVD[15]#

RSVD[16]#

RSVD[17]#

RSVD[18]#

RSVD[19]#

RSVD[20]#

BC LK[ 0]

BC LK[ 1]

PR OC H OT

TH E RM D A

TH E RM D C

TH ER MTRI P#

BPM[ 0]#

BPM[ 1]#

BPM[ 2]#

BPM[ 3]#

PRDY #

PREQ#

TC K

TD I

TD O

TMS

TR ST #

DBR#

HIT#

HITM#

RESET#

RS[0]#

RS[1]#

RS[2]#

TR DY #

IERR#

INIT#

LOCK#

BR0#

DEFER#

DRDY#

DBSY#

ADS#

BNR#

BPR I #

R14 *10K_04

H_BREQ0#

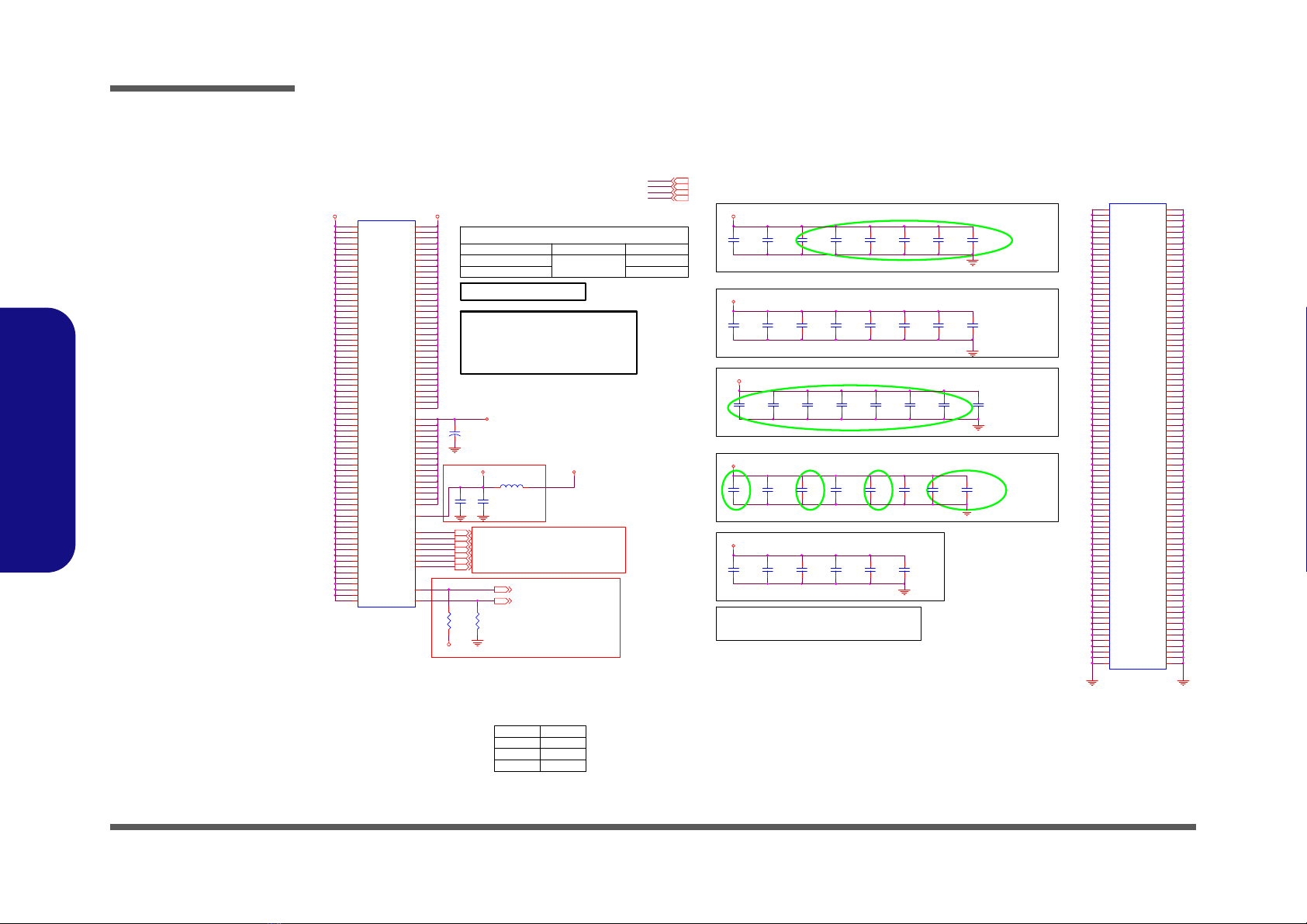

DATA GRP 3

DATA GRP 0 DATA GRP 1

MISC

DATA GRP 2

JSKT1B

PZ47913-2741-01

E22

F24

E26

H22

F23

G25

E25

E23

K24

G24

J24

J23

H26

F26

K22

H25

H23

G22

J26

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

M24

N25

M26

AD26

C26

D25

B22

B23

C21

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

COMP[ 0]

COMP[ 1]

COMP[ 2]

COMP[ 3]

DPRSTP#

DPSLP#

DPWR#

PWR GOOD

SLP#

PSI #

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

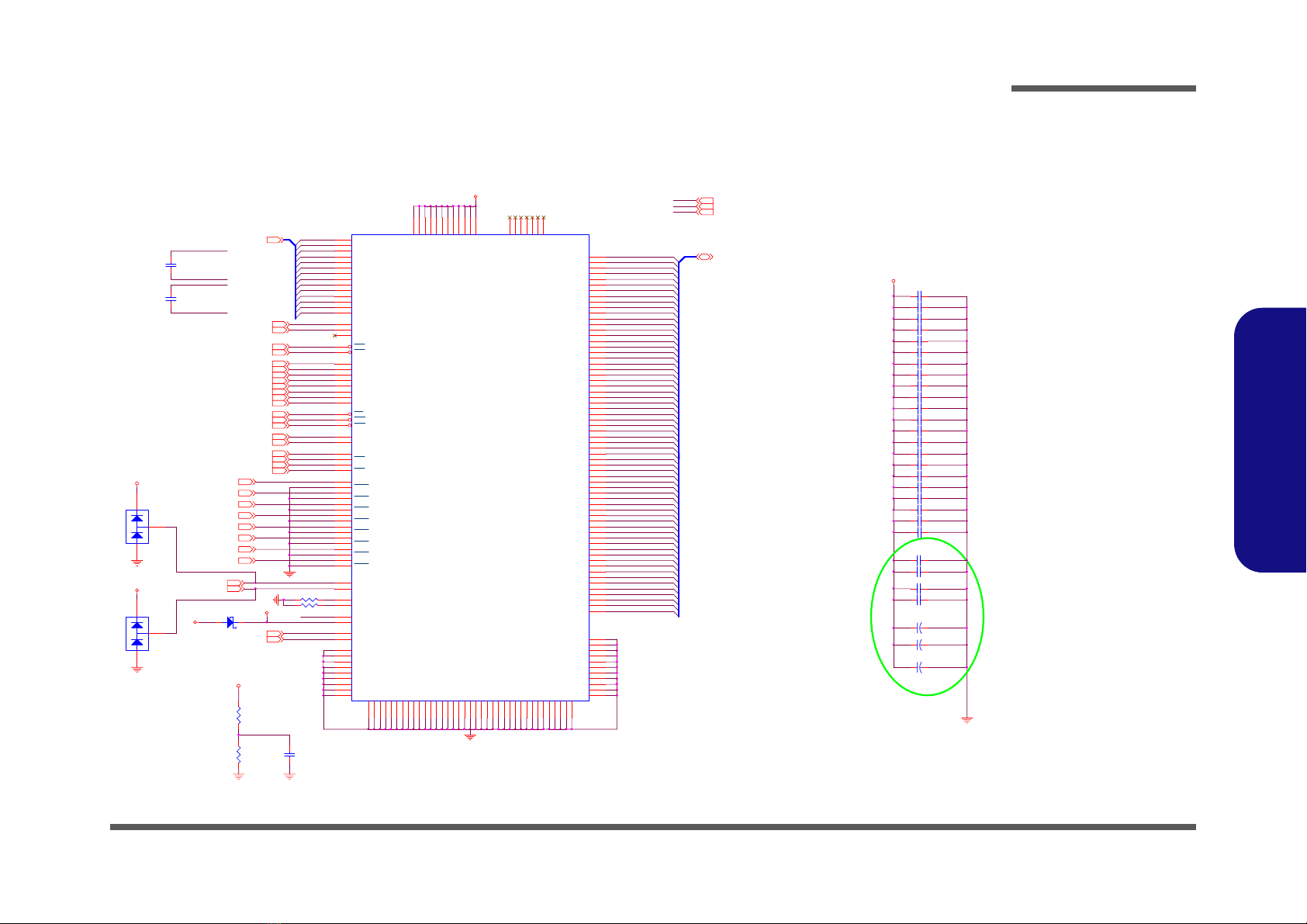

Layout note:

H_D#[63:0] 4

H_D#38

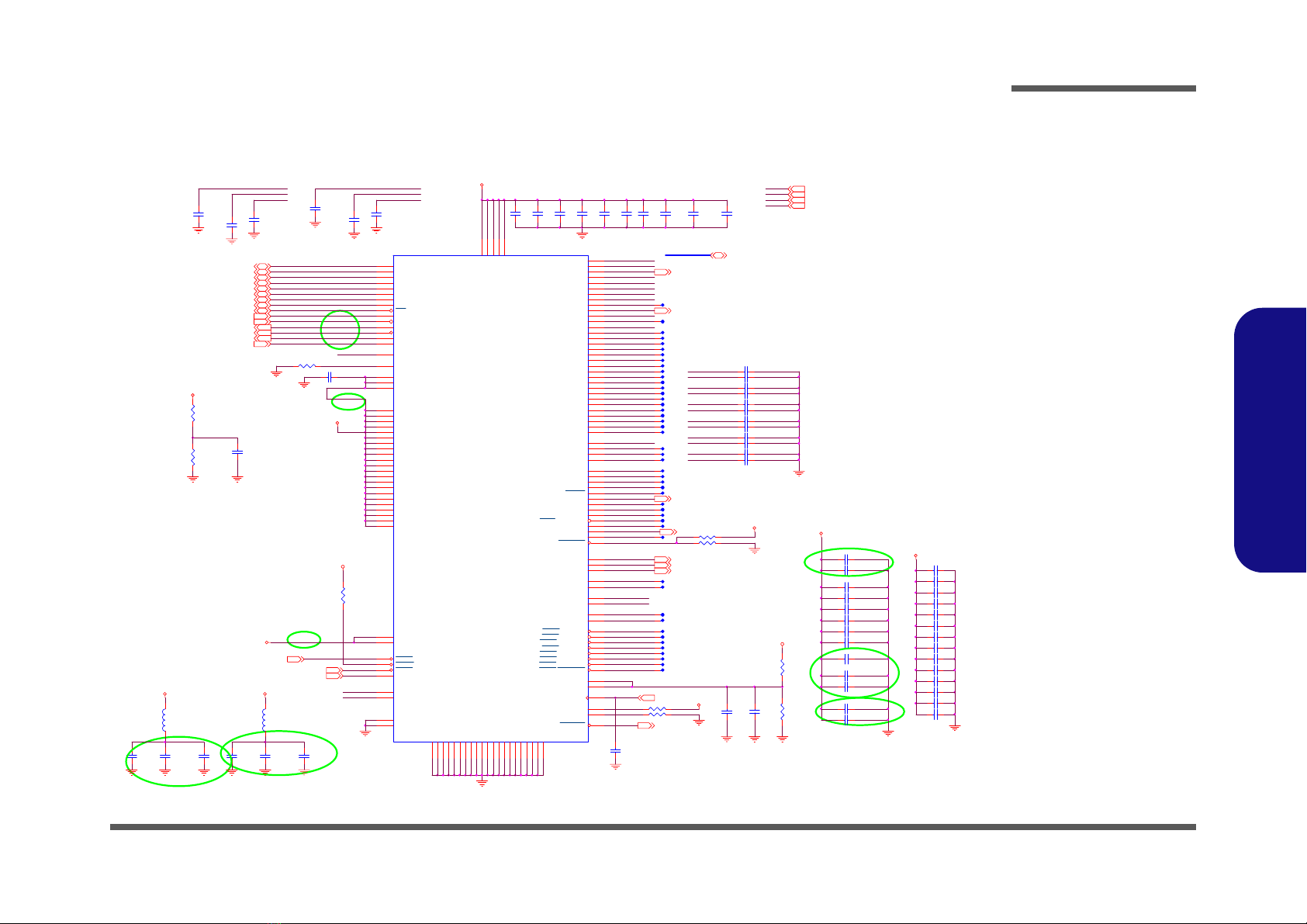

H_A#6

R316

100K_04 R335

10K_ 04

U19

ADM1032ARM

1

2

3

4

5

6

7

8

VD D

D+

D-

TH E RM

GND

ALERT

SDATA

SCLK

R339 1K_1%_06

Change Q4,Q5,Q47 from FDN337N to 3904

H_D#25

Q48

2N3904

B

E C

+V D D3

H_CPURST# 4

H8_THERM_ALERT# 20

H_PROCHOT# H_DSTBN#3 4H_ADSTB#14

H_D#50

H_DPSLP#

H_TCK

H_TCK

R312 330_04

H_DBSY# 4

SMD_THERM 20

PM_THRMTRIP#

R306

680_04

H_HITM# 4

H_D#39

H_TDI

H_STPCLK#

R19 54. 9_1%_06

TH E RM TR I P# 3 0

H_D#45

[13]

H_REQ#2

H_A#31

FERR#

R285

54.9_1%_06

R20 54. 9_1%_06

Q47

2N3904

B

E C

Zo=55ohm, 0.5" max for GTLREF, Space any other switch

signals away fromGTLREF with a minimumof 25mils.

SMC_THERM 20

H_BPM3#

H_A#23

H_THERMDC

H_CPUSLP#

If FERR# isn't used,

thenit must be

terminated with a 56

Ohm +-5% pull-up to

Vccp(1.05V)

H_D#14

R298 150_04

H_D#[63:0] 4

H_D#18

H_D#49

COMP0

H_BPM2#

R307 150_04

+V CC P

H_DBI#14

THERM_ALER T# 14

H_BPM0#

H_A#11

H_TDO

R336

2K_1%_06

[13]

H_IERR#

H_A20M#

Q4

2N390 4

B

EC

Don't allow the GTLREF routing to create splits or

discontinuities in the referenceplanes of the FSB

signals

H_D#27

H_DSTBN#2 4

TH ER M_R ST#20

H_D#46

H_D#2

H_CPURST#

H_STPCLK#

+V C CP

H_D#24

H_A#16

H_DRDY# 4

H_D#47

R309 150_04

R284 54.9_1%_06

R344

27.4_1%_06

R320

100K_04

H_TDI

Q5

2N390 4

B

E C

+V C C _TH R M

Comp1,3 connect with Zo=55ohm, make trace

length shorter than 0.5" and width is 5mils

C482

0.1u/16V_04

Route H_THERMDA and

H_THERMDC on same layer.

10 mil trace on 10 mil

spacing.

H_DBI#2 4

H_D#29

COMP3

H_BPM2#

R305

*10K_04

Place testpoint on

H_IERR# with a GND

0.1" away.

H_PWRGD 21

H_A#5

H_TMS

H_D#11

H_D#56

H_NMI

H_DPRSLPVR

R313 150_04

H_D#58

H_BPM1#

C443

*10u/10V_08

H_A#[31:3]4

H_TRST#

R283 54.9_1%_06

+V D D 3

H_RS#0 4

H_PWRGD

H_IGNN E#

H_A#10

R324

4.7K_04

If PROCHOT# is routed

between CPU, IMVP and

MCH, pull-up resistor

has to be 75 ohm ? 5%

+2. 5 VS

H_BPRI# 4

H_DBI#04

R314 150_04

CLK_CPU_BCLK# 10

H_D#48

H_D#0

H_PSI#

H_D#63

H_BNR# 4

H_TMS

H_D#13

H_A#9

H_A#13

R294 *51_1%_06

R343

54.9_1%_06

H_A#29

PSI# trace:space (4:8 or

5:10),Zo=55ohm +-15%

Comp0,2 connect with Zo=27.4ohm, make trace

length shorter than 0.5" andwidth is 18mils.

H_PROCHOT#

H_A#25

H_THERMDA

CPU_BSEL110

H_STPCLK#15

H_ADS# 4

H_IGNNE#

H_INIT#

H_D#44

H_DEFER# 4

H_NMI

H_A#26

H_D#1

Place Series Resistor on

H_PWRGD_XDP Without Stub

C483

1u/10V

+V D D3

H_D#37

COMP1

Q46

2N3904

B

E C

R66 51_ 1%_06

Q49

2N700 2

G

DS

Comp 0~3 traces should be at least 25mils

away fromany other togging signal

H_SMI#

H_D#[63:0]4

H_BPM1#

H_A#4

H_A#8

H_D#30

H_PSI#

H_INIT# 15

H_D#62

C473

1000p/ 50V

R311

680_04

Q50

NDS352AP

G

DS

H_A#[31:3]4

H_D#43

H_D#5

COMP0

H_REQ#3

ITP_DBRST#

H_D#59

H_A#17

CPU_BSEL010

H_FERR# 15

H_D#3