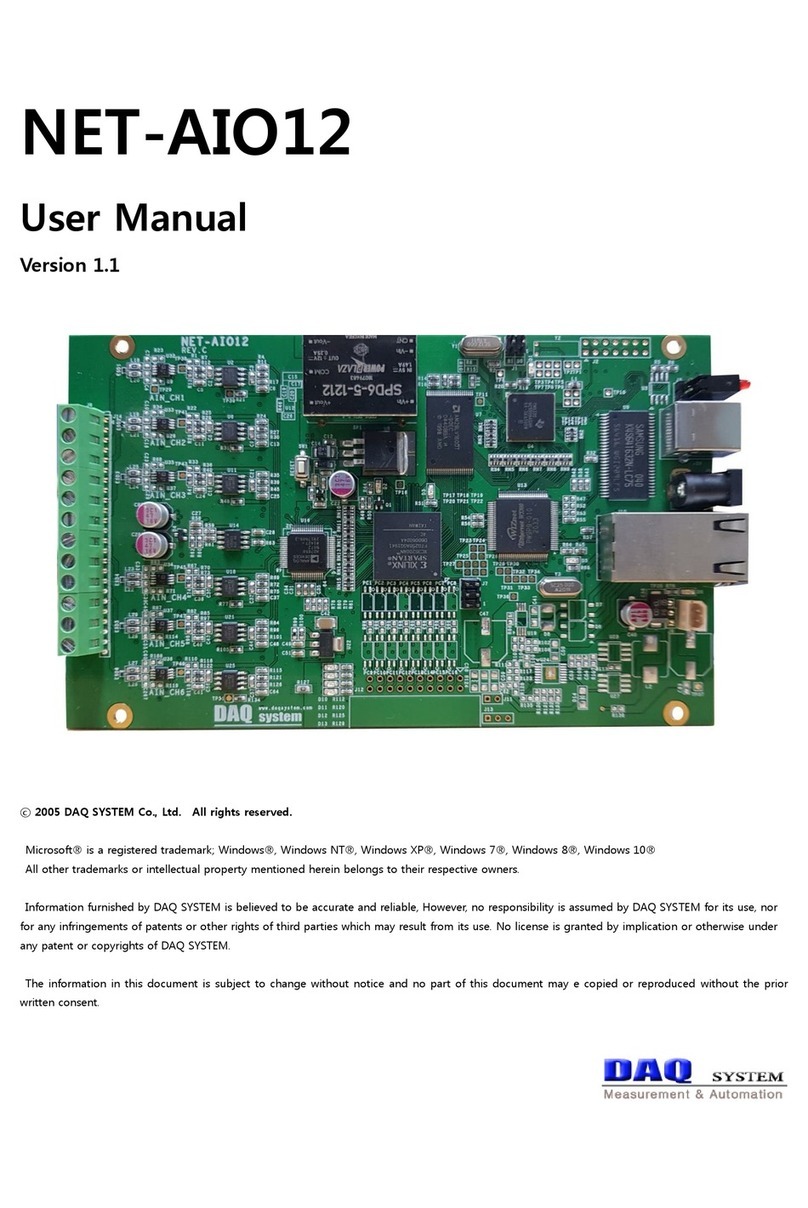

PCIE-FRM24_C User’s Manual

6

2-2 Camera Link

Camera Link is a communication interface developed for use in vision applications. In the past,

camera manufacturers and frame grabber manufacturers used their own standard connectors and

cables. This caused a lot of confusion and cost increase for users. In order to resolve this

confusion, increasing data rate, and confusion in data transmission, the specifications of the

Camera Link interface are the specifications of cable or connector assembly, transmission speed

and It was made with regulations such as transmission method.

Many digital video solutions currently use LVDS (Low Voltage Differential Signal) communication

defined by RS-644. RS-644 LVDS has become the Camera Link standard by improving the existing

RS-422 method, which had inconvenient cables and limited transmission speed. LVDS can transmit

data at high speed by using a differential signal with a low voltage swing. Compared to the

existing single-ended signal using one line, the differential signal transmits the signal using two

complementary lines. This transmission structure has the characteristics of large-scale common-

phase voltage rejection, low power consumption, and excellent noise immunity, which is

impossible with single-ended systems that only reference ground for data transmission.

The camera link has several configurations according to the amount of data to be transmitted.

In case of Base Configuration, it is composed of 28 bits including 24-bit pixel data, Data Valid,

Frame Valid Line Valid, 3-bit video sync signal line of Line Valid, and Line Valid, and one reserved

signal line, and can transmit 2.04 Gbit/s (256 MB/s). Medium Configuration can transmit a 48-bit

video signal at 4.08Gbit/s (510Mb/s), and Full Configuration can transmit a 64-bit video signal at

5.44Gbit/s (680MB/s). Camera Link requires two cables to carry more than the Medium

specification.

The transceiver stage converts this 28/48/64 bit CMOS/TTL data into 4/8/12 LVDS data streams.

The converted signal is transmitted to the MDR cable according to the Transmit Clock, and the

receiver on the other side converts these 4/8/12 LVDS data into a 28/48/64 bit CMOS/TTL parallel

signal according to the Receive Clock. This channel link technology is being used as a low-cost

chipset that is easy to learn and portable, so that it can be used immediately.

Camera Link interface includes Base Configuration, Medium Configuration, and Full

Configuration. Base Configuration uses four RS-644 LVDS pairs for transmitter/receiver and camera

control as shown in [Figure 2-2], and two RS-644 LVDS pairs for communication between camera

and frame grabber. . The data transmitted serially through the 26-Pin MDR Cable is changed to

28-bit parallel image data at the Receive end of the frame grabber and used.