2

AVR-3801

SPECIFICATIONS

!!

!!

!AUDIO SECTION

""

""

"Power Amplifier

Rated output: Front: 105W + 105W (8Ω/ohms, 20Hz ~ 20kHz with 0.05% T.H.D.)

150W + 150W (6Ω/ohms, 1kHz with 0.7% T.H.D.)

180W + 180W (6Ω/ohms, EIAJ)

Center: 105W (8Ω/ohms, 20Hz ~ 20kHz with 0.05% T.H.D.)

150W (6Ω/ohms, 1kHz with 0.7% T.H.D.)

180W + 180W (6Ω/ohms, EIAJ)

Surround: 105W + 105W (8Ω/ohms, 20Hz ~ 20kHz with 0.05% T.H.D.)

150W + 150W (6Ω/ohms, 1kHz with 0.7% T.H.D.)

180W + 180W (6Ω/ohms, EIAJ)

Surround Back: 105W + 105W (8Ω/ohms, 20 Hz ~ 20kHz with 0.05% T.H.D.)

150W + 150W (6Ω/ohms, 1kHz with 0.7% T.H.D.)

180W + 180W (6Ω/ohms, EIAJ)

Dynamic power: 140W ×2ch (8Ω/ohms)

210W ×2ch (4Ω/ohms)

240W ×2ch (2Ω/ohms)

Output terminals: Front, Center, Surr. Back/Multi Zone: 6 ~ 16Ω/ohms

Surround: A or B 6 ~ 16Ω/ohms

A + B 8 ~ 16Ω/ohms

""

""

"Analog

Input sensitivity/input impedance: 200mV/47kΩ/kohms

Frequency response: 10Hz ~ 100kHz: +0, −3dB (DIRECT model)

S/N: 102dB (DIRECT mode)

Distortion: 0.005% (20Hz ~ 20kHz) (DIRECT mode)

Rated output: 1.2V

""

""

"Digital

D/A output: Rated output 2V (at 0dB playback)

Total harmonic distortion 0.008% (1 kHz, at 0 dB)

S/N ratio 102dB

Dynamic range 96dB

Digital input: Format Digital audio interface

""

""

"Phono equalizer (PHONO input

REC OUT)

Input sensitivity: 2.5mV

RIAA deviation: ±1dB (20Hz to 20kHz)

Signal-to-noise ratio: 74dB (A weighting, with 5mV input)

Rated output/Maximum output: 150mV/8V

Distortion factor: 0.03% (1kHz, 3V)

!!

!!

!VIDEO SECTION

""

""

"Standard video jacks

Input/output level and impedance: 1Vp-p, 75Ω/ohms

Frequency response: 5Hz ~ 10MHz +0, −3dB

""

""

"S-video jacks

Input/output level and impedance: Y (brightness) signal 1Vp-p, 75Ω/ohms

C (color) signal 0.286Vp-p, 75Ω/ohms

Frequency response: 5Hz ~ 10MHz +0, −3dB

""

""

"Color component video jacks

Input/output level and impedance: Y (brightness) signal 1Vp-p, 75Ω/ohms

CB(blue) signal 0.7Vp-p, 75Ω/ohms

CR(red) signal 0.7Vp-p, 75Ω/ohms

Frequency response: 5Hz ~27MHz +0, −3dB

!!

!!

!TUNER SECTION [FM] (note: µV at 75Ω/ohms, 0dBf=1 ×10-15 W) [AM]

Receiving Range: 87.50MHz ~ 107.90MHz 520kHz ~ 1710kHz

(for North America and multiple voltage models) (for North America and Multiple voltage models)

87.50MHz ~ 108.00MHz 522kHz ~ 1611kHz

(for Europe, China, Hong Kong, Taiwan R.O.C. and Multiple voltage models) (for Europe, China, Hong Kong, Taiwan R.O.C. and multiple voltage models)

Usable Sensitivity: 1.0µV (11.2dBf) 18µV

50dB Quieting Sensitivity: MONO: 1.6µV (15.3dBf)

STEREO: 23µV (38.5dBf)

S/N (IHF-A): MONO: 80dB

STEREO: 75dB

Total Harmonic Distortion (at 1kHz): MONO: 0.15%

STEREO: 0.3%

!!

!!

!GENERAL

Power supply: AC120V, 60Hz (for North America and Taiwan R.O.C. models)

AC230V, 50Hz (for Europe model)

AC220V, 50Hz (for China model)

AC115V/230V, 50/60Hz (for Hong Kong and Multiple voltage models)

Power consumption: 7.0A (for North America model)

400W (for Europe, China, Hong Kong and Multiple voltage models)

360W (for Taiwan R.O.C. model)

2.0W Max (Standby)

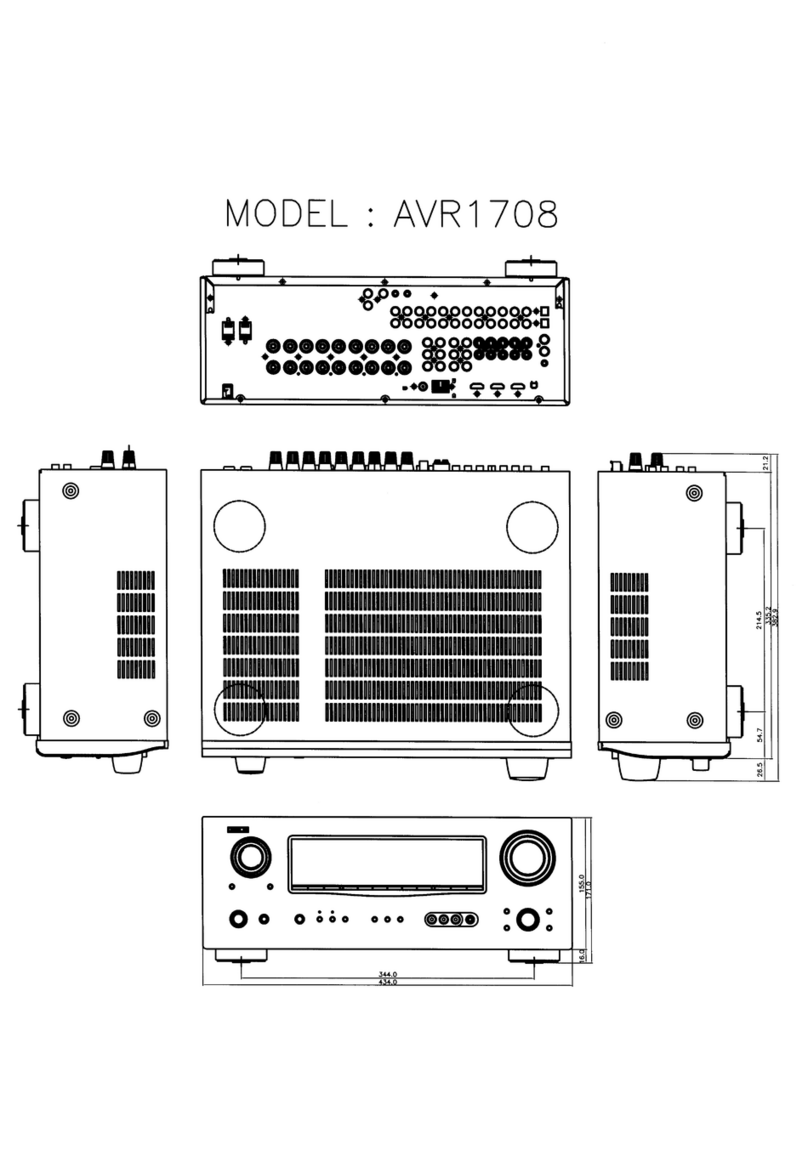

Maximum external dimensions: 434 (W) ×171 (H) ×416 (D)mm (17-3/32″×6-11/32″×16-3/8″)

Weight: 17.0kg (37 lbs 8 oz)

!!

!!

!REMOTE CONTROL UNIT (RC-883: for North America, China, Hong Kong,Taiwan R.O.C. and Multiple voltage models)

(RC-884: for Europe model)

Batteries: R6P/AA Type (three batteries)

External dimensions: 61 (W) ×230 (H) ×34 (D)mm (2-13/32″×9-1/16″×1-11/32″)

Weight: 200g (Approx. 7 oz) (including batteries)

* For purposes of improvement, specifications and design are subject to change without notice.

SAFETY PRECAUTIONS

The following check should be performed for the continued protection of the customer and service technician.

LEAKAGE CURRENT CHECK

Before returning the unit to the customer, make sure you make either (1) a leakage current check or (2) a line to chassis

resistance check. If the leakage current exceeds 0.5 milliamps, or if the resistance from chassis to either side of the

power cord is less than 460 kohms, the unit is defective.

Spec.p65 00/09/12, 14:36Page 2 AdobePageMaker6.5J/Win