dg_nvmeip_raid0x2_fpgasetup_xilinx_en.doc

3-Aug-22 Page 1

FPGA setup for 2-Ch RAID0 by NVMe-IP Demo

Rev2.2 3-Aug-22

This document describes the FPGA and test environment setup for running 2-ch RAID0 by using

NVMe-IP, NVMeG3-IP, NVMeG4-IP, or NVMe-IP for Gen4 demo on FPGA development board by

using the AB17-M2FMC board or AB18-PCIeX16 board with Quad M.2 card for connecting with

two M.2 NVMe SSDs. It is recommended to use the same SSD models for RAID0 operation to

match SSD characteristic. User controls test operation via Serial console.

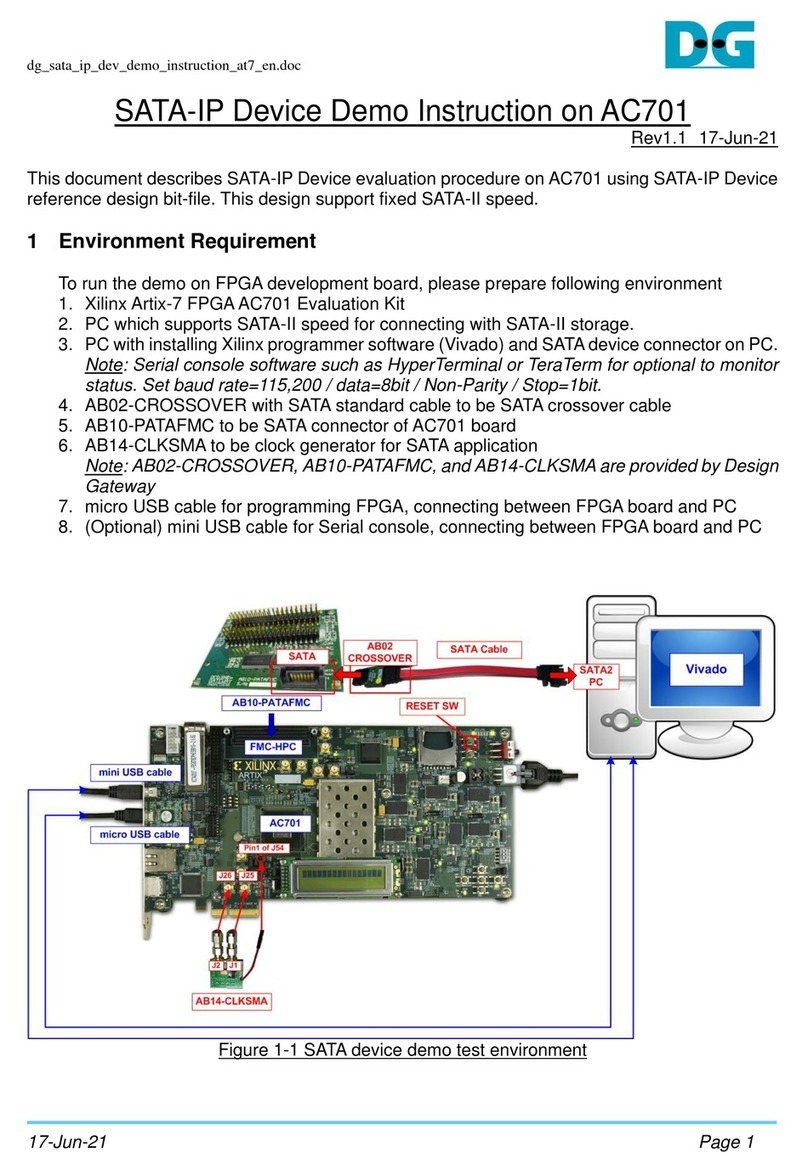

1 Test Environment setup

To run the demo on FPGA development board, please prepare following environment.

1) FPGA development board: VCK190, VCU118, ZCU106, ZCU102, KCU105

2) The adapter of M.2 SSD

a. AB17-M2FMC board

https://dgway.com/ABseries_E.html

b. AB18-PCIeX16 board with Quad M.2 card

https://dgway.com/ABseries_E.html

https://www.asrock.com/mb/spec/product.asp?Model=ULTRA%20QUAD%20M.2%20CA

RD

3) Two M.2 NVMe SSDs, inserting to M.2 connector on AB17/Quad M.2 card

4) For AB18 only,ATX power supply for PCIe adapter board

5) Xilinx power adapter for FPGA board

6) Two micro USB cables/one USB type-C cable for programming FPGAand Serial console,

connecting between FPGA board and PC

7) PC installing Xilinx programmer software (Vivado) and Serial console software such as

TeraTerm and HyperTerminal