dg_toe100gip_fpgasetup_xilinx.doc

28-Apr-21 Page 3

2 Test environment setup when using FPGA and PC

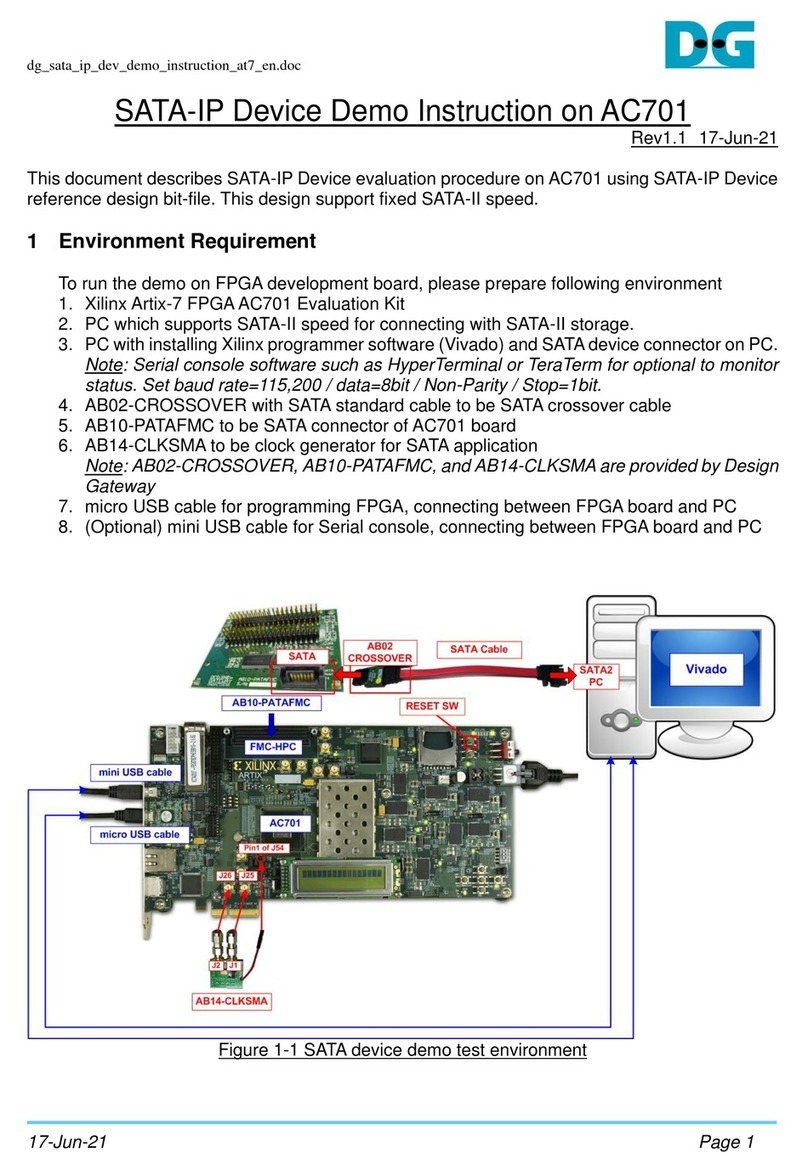

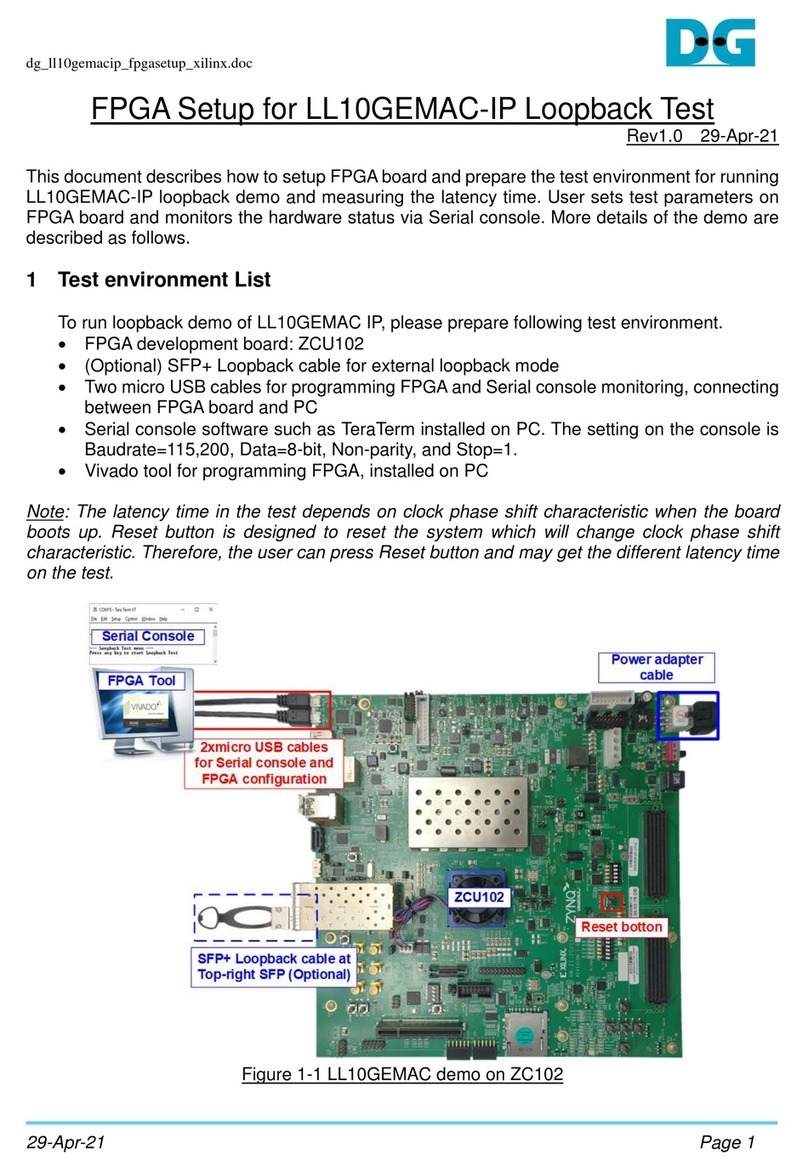

To run the demo on FPGAdevelopment board, please prepare following environment.

•FPGA development boards: KCU116 board, Alveo U250 card, and FB2CGHH@KU15P

card

•PC with 100 Gigabit Ethernet card

•100Gb Ethernet cable:

a) KCU116 board: 4xSFP28 transceiver (25GBASE-SR), QSFP28 transceiver

(100GBASE-SR), and MTP to 8xLC Fiber cable

b) U250 card and FB2CGHH@KU15P card: 2xQSFP28 transceiver (100GBASE-SR) and

MPO to MPO cable.

•USB cable for connecting between FPGAand PC

a) KCU116: 2 micro USB cables for programming FPGA and Serial console

b) U250 card: 1 micro USB cable for programming FPGA and Serial console

c) FB2CGHH@KU15P card: 1 mini USB cable for programming FPGA and JTAGAURT

•For FB2CGHH@KU15P card, use AB18-PCIeX16 board provided by Design Gateway

with ATX power supply to be power board for the card. More details of AB18 card are

displayed on following website.

https://dgway.com/ABseries_E.html

•Test application: “tcpdatatest.exe” and “tcp_client_txrx_40G.exe”, provided by Design

Gateway for running on Test PC

•For KCU116 and U250 card, Serial console software such as TeraTerm installed on PC.

The setting on the console is Baudrate=115,200, Data=8-bit, Non-parity and Stop=1.

•Vivado tool for programming FPGA and JTAGUART (when using FB2CGHH@KU15P

card), installed on PC

Note: Example hardware for running the demo is listed as follows.

[1] 100G Network Adapter: NVIDIA Mellanox ConnectX-6 Ethernet Adapter Card

https://store.mellanox.com/products/nvidia-mcx614106a-ccat-connectx-6-en-adapter-ca

rd-100gbe-dual-port-qsfp56-socket-direct-2x-pcie3-0-x16-tall-brackets.html

[2] a) 4xSFP28 to QSFP28 connection

SFP28 Transceiver: AZS85-S28-M1

https://www.sfpcables.com/25gb-s-sfp28-sr-transceiver-850nm-up-to-100m-2866

QSFP28 Transceiver: AMQ28-SR4-M1

https://www.sfpcables.com/100gb-s-qsfp28-sr4-optical-transceiver-module-1499

MTP to 8xLC Fiber cable: OM4-MTP-8LC-1M

https://www.fs.com/products/68047.html

b) QSFP28 to QSFP28 connection

QSFP28 Transceiver: AMQ28-SR4-M1

https://www.sfpcables.com/100gb-s-qsfp28-sr4-optical-transceiver-module-1499

MPO to MPO cable: OM4-MPO-8MPO-1M

https://www.sfpcables.com/mpo-to-mpo-multimode-om4-50-125-m-8-core-4381

[3] PC: Motherboard Gigabyte B460M AORUS PRO, 32 GB RAM, and 64-bit Windows10 OS