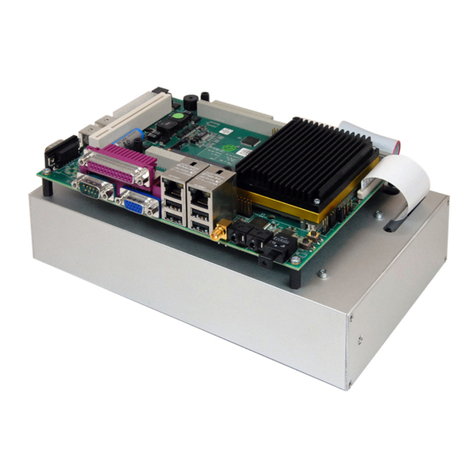

DIGITAL-LOGIC AG PCCP5 Manual V2.3

3

Table of Contents

1PREFACE......................................................................................................................................................................................6

1.1 TRADEMARKS........................................................................................................................................................................6

1.2 DISCLAIMER...........................................................................................................................................................................6

1.3 WHO SHOULD USE THIS PRODUCT ......................................................................................................................................6

1.4 RECYCLING INFORMATION..................................................................................................................................................7

1.5 TECHNICAL SUPPORT ...........................................................................................................................................................7

1.6 LIMITED WARRANTY............................................................................................................................................................7

2OVERVIEW .................................................................................................................................................................................8

2.1 STANDARD FEATURES..........................................................................................................................................................8

2.2 UNIQUE FEATURES................................................................................................................................................................8

2.3 BLOCK DIAGRAM..................................................................................................................................................................9

2.4 PCC-P5 SPECIFICATIONS...................................................................................................................................................10

2.5 THERMOSCAN......................................................................................................................................................................14

2.6 ORDERING CODES...............................................................................................................................................................14

2.7 BIOS HISTORY....................................................................................................................................................................15

2.8 RELATED APPLICATION NOTES.........................................................................................................................................15

2.9 THIS PRODUCT IS “YEAR 2000 CAPABLE” ..............................................................................................15

2.10 PCC-P5L INCOMPATIBILITIES TO A STANDARD PC/AT............................................................................................15

2.11 MECHANICAL DIMENSIONS...............................................................................................................................................16

3THE ISA AND PC/104 BUS SIGNALS..............................................................................................................................17

3.1 EXPANSION BUS..................................................................................................................................................................20

4DETAILED SYSTEM DESCRIPTION..............................................................................................................................21

4.1 POWER REQUIREMENTS.....................................................................................................................................................21

4.2 CPUS, BOARDS AND RAMS..............................................................................................................................................21

4.2.1 CPUs of this MICROSPACE Product....................................................................................................................21

4.3 INTERFACES.........................................................................................................................................................................22

4.3.1 PS/2-Keyboard...........................................................................................................................................................22

4.3.2 PS/2-Mouse Interface...............................................................................................................................................22

4.3.3 Line Printer Port LPT1.............................................................................................................................................22

4.3.4 Serial Ports COM1-COM2......................................................................................................................................23

4.3.5 Floppy disk interface................................................................................................................................................24

4.3.5.1 Supported floppy formats.........................................................................................................................................24

4.3.5.2 Floppy interface connector.......................................................................................................................................24

4.3.6 Speaker interface.......................................................................................................................................................25

4.4 CONTROLLERS.....................................................................................................................................................................26

4.4.1 Interrupt Controllers................................................................................................................................................26

4.5 TIMERS AND COUNTERS.....................................................................................................................................................26

4.5.1 Programmable Timers..............................................................................................................................................26

4.5.2 Battery backed clock (RTC)....................................................................................................................................27

4.5.3 Watchdog....................................................................................................................................................................27

4.6 BIOS......................................................................................................................................................................................28

4.6.1 ROM-BIOS Sockets...................................................................................................................................................28

4.6.1.1 Standard BIOS FLASH 29F010...............................................................................................................................28

4.6.1.2 VGA BIOS FLASH 29F010....................................................................................................................................28

4.6.2 EEPROM Memory for Setup...................................................................................................................................29

4.6.3 CMOS RAM Map.......................................................................................................................................................30

4.6.4 BIOS CMOS Setup....................................................................................................................................................36

4.6.5 CMOS Setup Harddisk list.......................................................................................................................................37

4.6.6 Harddisk PIO Modes................................................................................................................................................37

4.6.7 EEPROM saved CMOS setup..................................................................................................................................38

4.7 DOWNLOAD THE VGA-BIOS AND THE CORE-BIOS..................................................................................................39

4.7.1 VGA- BIOS Download Function............................................................................................................................40

4.8 MEMORY ..............................................................................................................................................................................41

4.8.1 Onboard DRAM Memory.........................................................................................................................................41

4.8.2 System Memory Map.................................................................................................................................................41