Embedded Solutions Page 9 of 37

Theory of Operation

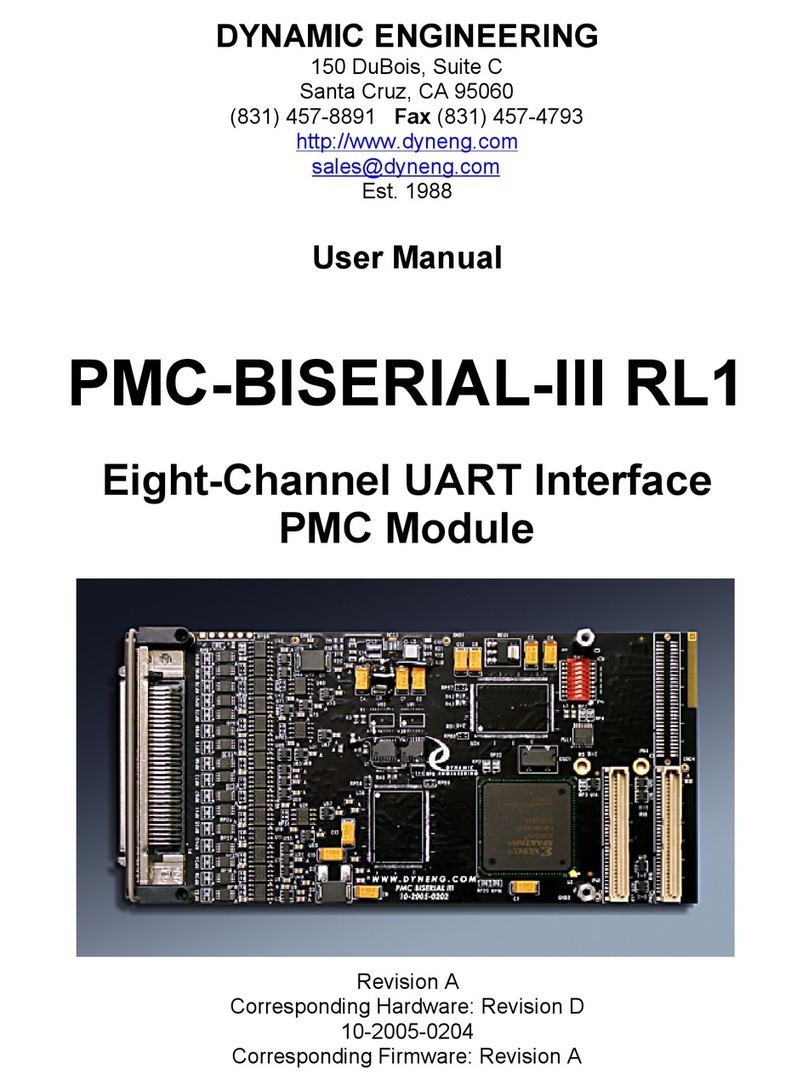

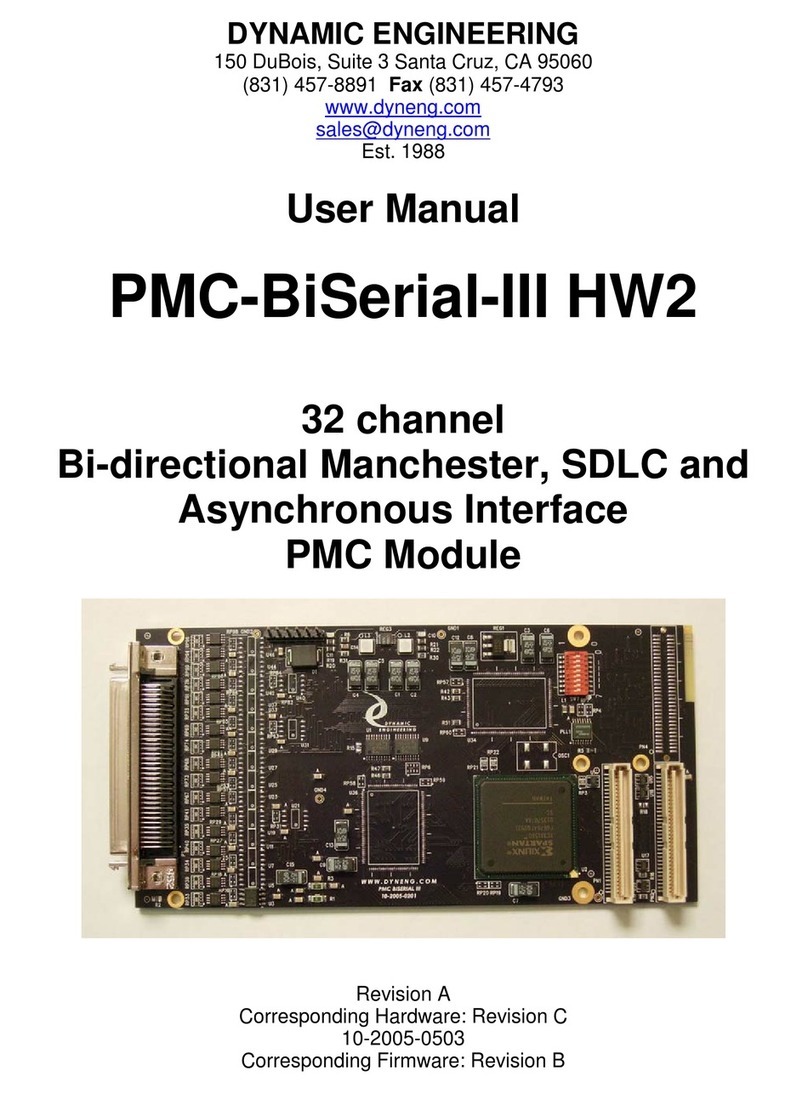

The PMC BiSerial-III-SDLC features a Xilinx FPGA. The FPGA contains all of the

registers and protocol controlling elements of the BiSerial III design. Only the PLL,

transceivers, and switches are external to the Xilinx device.

The PCI interface to the host CPU is controlled by a logic block within the Xilinx. The

BiSerial III design requires one wait state for read or write cycles to any address. The

PMC BiSerial-III is capable of supporting 40M Bytes per second into and out of the

DPR. With a Windows® read/write loop better than 20 MB/sec is attained on most

computers. The wait states refer to the number of clocks after the PCI core decode

before the “terminate with data” state is reached. Two additional clock periods account

for the 1 clock delay to decode the signals from the PCI bus and to convert the

terminate-with-data state into the TRDY signal.

The BiSerial III can support many protocols. The PMC BiSerial-III-SDLC supports

eight-channel full-duplex SDLC interfaces. This is a synchronous interface with

separate clock and data inputs and outputs. Each message is delimited by eight-bit

flag characters. The beginning flag and the ending flag enclose the SDLC frame. Both

beginning and ending flags have the binary format 01111110. The ending flag for one

frame may serve as the beginning flag for the next frame. Alternatively, the ending zero

of an ending flag may serve as the beginning zero of a beginning flag, thus forming the

pattern ‘011111101111110’. Also, the transmitter may insert multiple flags between

frames to maintain the active state of the link if time fill between message frames is

required. In order to avoid false flag detection from the data pattern, the SDLC

interface uses zero insertion. If five consecutive ones appear anywhere in the data

stream, a zero is inserted to avoid having six consecutive one bits. On the receive side,

when five ones are received the sixth bit is monitored. If it is a zero, it is removed from

the data stream, if it is a one then either a start/stop flag or an abort character (0xFE)

has been detected. Any ending flag may be followed by a frame, by another flag, or by

an idle condition. The idle condition is signaled by a minimum of 15 consecutive one

bits. As long as one bits continue to be sent, the link remains in the idle state.

To send a message, write the message data to the transmit DPRs, specify the start and

stop addresses and configuration control bits, then enable the transmitter. The state-

machine will load the start address, send the beginning flag character and then send

the data sequentially LSB first until the end address is reached and the ending flag is

sent. As soon as the beginning flag is sent, the sending status bit will be asserted. At

that time the ending address will be latched in the transmitter and new addresses can

be written for the next message to be sent. This message will be sent as soon as the

current message completes. If a new transmit starting address is not written, the

transmitter will continue reading data with the next address after the stop address of the

current frame. A new transmit end address must be written to trigger sending an

additional message-frame.