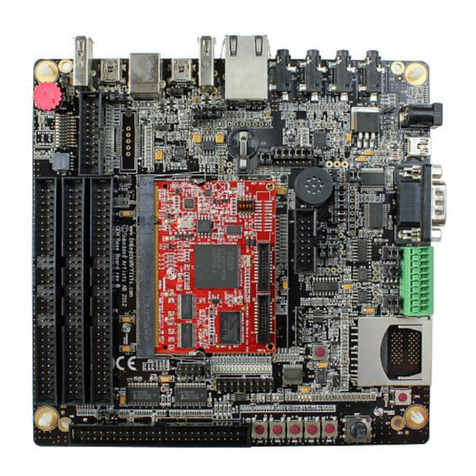

The LPC3152 OEM Board uses the external SDRAM bank 0 as well as NAND bank 0. It is mainly the

two external SRAM banks that are available for the off-board external memory interface of the

LPC3152 OEM Board. Chip select signals N_STCS0 and N_STCS1 are free for external use via the

buffered memory interface. Both the address and the data busses are buffered.

3.4.1.2 SDRAM

A 512 MBit (64 MByte) Mobile SDRAM is used, MT48H32M16LF from Micron. The chip is powered by

1.8V and is organized as 32Mbit x16, i.e. it has 16-bit databus width. The chip occupies the only

available memory bank for dynamic RAM at address range 0x3000 0000 –0x33FF FFFF.

3.4.1.3 NAND Flash

A 2 Gbit (256) NAND flash is used, MT29F2G08ABDHC from Micron. The chip is powered by 1.8V and

has 8-bit databus width. The NAND flash builds on a single-level cell (SLC) technology and has a page

size of 2112 bytes (2,048 + 64 bytes). The chip is connected to NAND bank 0. Note that the chip is not

directly accessible via the memory bus. Instead, all accesses must be done via the on-chip NAND

flash controller of the LPC3152.

Embedded Artists can choose to mount a different brand of NAND flash dependent on component

availability at the time of production. The application program should always read out the NAND flash

chip id and determine type and features.

3.4.1.4 Buffers to External Interface

The LPC3152 memory interface is available on the expansion connector. The data bus width is 16-bits

on the external interface. The relevant signals are buffered. The buffers are disabled by default unless

enabled by external signals.

By pulling signal N_ABUF_EN low, the two buffers for address and control signals are enabled and act

as outputs (from the LPC3152 OEM Board).

The data bus buffer is controlled by the signal N_DBUF_EN. By pulling this signal low, the data bus

buffer is enabled. The buffered version of the LPC3152 signal OE controls the direction of the data bus

buffer. During read operations the buffer acts as an input and during write operations it acts as an

output.

Note that N_DBUF_EN must not be pulled low constantly. In that case the buffer will collide with the

board’s internal data bus. N_DBUF_EN must only be pulled low when an external memory/IO device is

accessed. If only one of the static chip selects is used externally, just connect that signal to

N_DBUF_EN. If more than one chip select signal is used, (logically) AND all chip select signal together

before driving the N_DBUF_EN signal, in this case, just AND the two signals B_N_STCS0 and

B_N_STCS1.

There is an additional important note when booting from NAND flash, read section 4.6 for details about

the N_DBUF_EN signal.

If the external memory interface is not used, leave ABUS_EN and DBUS_EN unconnected.

The buffers are dual voltage buffers and act as level translators between the internal 1.8V signal levels

and the external levels. Connect the external bus voltage to VDD_EXT. See the datasheet of

74AVCA164245 for exact details about voltage range. Normally 3.3V powering is used.

3.5 Schematic Page 6: Expansion Connector

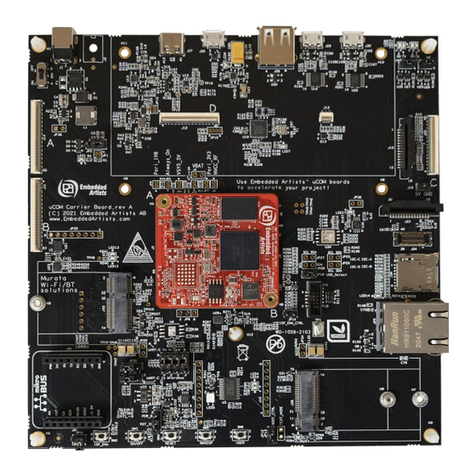

The LPC3152 OEM Board integrates the core part of a typical LPC3152 board design with a

reasonable large amount of external memories. All relevant signals of LPC3152 are available on the

200 pos, 0.6mm pitch expansion connector (SODIMM-200 format). See the next section for a detailed

list of available pins.