EWA CORELIS PXIE-1149.1/4E User manual

PXIE-1149.1/4E

PXIE-1149.1/4E

High-Speed PXIE

Boundary-Scan Controller

User’s Manual

Copyright © 2019, Corelis Inc.

Corelis, Inc.

13100 Alondra Blvd. Suite 102

Cerritos, CA 90703-2262

Telephone: (562) 926-6727 • Fax: (562) 404-6196

i

Preface

PRINTING HISTORY

Updated versions of this manual represent the text has been modified and are dated at the time of

the most recently published version of this document.

The date of this manual also references the most recent version of the software product at the time

the manual was published, or update or product update was issued. Many product updates and fixes

do not require manual changes and, conversely, manual corrections may occur without

accompanying product changes.

Edition 1, September 2019

GENERAL NOTICE

Information contained in this document is subject to change without notice. CORELIS shall not be

liable for errors contained herein for incidental or consequential damages in connection with the

furnishing, performance, or use of material contained in this manual.

This document contains proprietary information that is protected by copyright. All rights reserved.

No part of this document may be reproduced or translated to other languages without the prior

written consent of CORELIS. This manual is a CORELIS proprietary document and may not be

transferred to another party without the prior written permission of CORELIS.

CORELIS assumes no responsibility for the use of or reliability of its software on equipment that is

not furnished by CORELIS.

ENVIRONMENTAL NOTICE

This product must be disposed of in accordance with the WEEE directive.

TRADEMARK NOTICE

Pentium is a registered trademark of Intel Corporation.

Windows is a registered trademark of Microsoft Corporation.

I2C Bus is a registered trademark of Philips Electronics N.V.

Other products and services named in this book are trademarks or registered trademarks of their

respective companies. All trademarks and registered trademarks in this book are the property of

their respective holders.

PRODUCT WARRANTY

For product warranty and software maintenance information, see the PRODUCT WARRANTY

AND SOFTWARE MAINTENANCE POLICY statement included with your product shipment.

ii

EXCLUSIVE REMEDIES

THE REMEDIES CONTAINED HEREIN ARE THE CUSTOMER'S SOLE AND

EXCLUSIVE REMEDIES. CORELIS SHALL NOT BE LIABLE FOR ANY DIRECT,

INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER

BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

Product maintenance agreements and other customer assistance agreements are available for Corelis

products. For assistance, contact your nearest Corelis Sales and Service Office.

RETURN POLICY

No items returned to CORELIS for warranty, service, or any other reason shall be accepted unless

first authorized by CORELIS, either directly or through its authorized sales representatives. All

returned items must be shipped pre-paid and clearly display a Returned Merchandise Authorization

(RMA) number on the shipping carton. Freight-collect items will NOT be accepted. Customers or

authorized sales representatives must first contact CORELIS with notice of request for return of

merchandise. RMA's can only originate from CORELIS. If authorization is granted, an RMA

number will be forwarded to the customer either directly or through its authorized sales

representative.

CONTACT INFORMATION

For any support related questions, please enter a support request at www.corelis.com/support or

For more information about other products and services that Corelis offers, please visit

www.corelis.com.

iii

Table of Contents

Chapter 1: Product Overview.....................................................................................................1

Introduction ..................................................................................................................................................... 1

What is IEEE Standard 1149.1? ........................................................................................................................ 2

Features of the PXIE-1149.1/4E....................................................................................................................... 2

Adjustable Voltage Levels............................................................................................................................................................ 3

Discrete Input/Output Signals ................................................................................................................................................... 3

PXIE Interface .............................................................................................................................................................................. 3

Programmable Clocks................................................................................................................................................................... 3

Controllable Slew Rate ................................................................................................................................................................. 4

Software Pin Configuration......................................................................................................................................................... 4

Pin Protection ................................................................................................................................................................................ 4

PXIE-1149.1/4E Hardware Specifications ....................................................................................................... 5

Physical............................................................................................................................................................................................ 5

Operating Environment............................................................................................................................................................... 5

Storage Environment.................................................................................................................................................................... 5

Host Interface ................................................................................................................................................................................ 5

Power Requirements..................................................................................................................................................................... 5

PXIE-1149.1/4E Electrical Specifications ........................................................................................................ 6

JTAG TAP Interface .................................................................................................................................................................... 6

Chapter 2: PXIE-1149.1/4E Installation....................................................................................7

Software Must Be Installed. ............................................................................................................................. 7

PXIE-1149.1/4E Hardware Installation ........................................................................................................... 7

Installation Steps ........................................................................................................................................................................... 7

Chapter 3: Connecting to the Target....................................................................................... 11

Connecting to the Target ................................................................................................................................11

Connecting the TAP Signals ...........................................................................................................................13

Chapter 4: Using the PXIE-1149.1/4E with ScanExpress....................................................... 15

Hardware Setup...............................................................................................................................................15

Using PXIE-1149.1/4E with ScanExpress Tools.............................................................................................15

Chapter 5: Third Party Application Interface ......................................................................... 17

Using the PXIE-1149.1/4E with the ScanExpress Runner Command-line.....................................................17

Appendix A: Recommended Target Connectors ....................................................................23

10-pin TAP Connector.................................................................................................................................... 23

Flash Programming TAP Connector ............................................................................................................. 26

iv

20-pin TAP Connector.................................................................................................................................... 29

Appendix B: Self-Test Utility Software ...................................................................................33

Self-Test ......................................................................................................................................................... 33

v

List of Figures

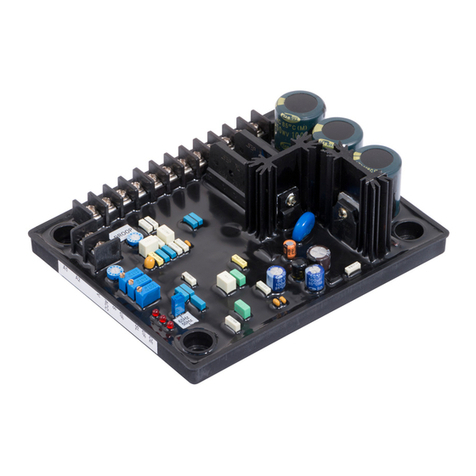

Figure 1-1. PXIE-1149.1/4E Boundary-scan Controller ..........................................................................1

Figure 1-2. Minimal Test Access Port..........................................................................................................2

Figure 2-1. Found New Hardware Wizard..................................................................................................8

Figure 2-2. Found New Hardware Wizard..................................................................................................9

Figure 2-3. Installation Successfully Completed.........................................................................................9

Figure 2-4. Windows Device Manager.......................................................................................................10

Figure 3-1. PXIE-1149.1/4E 80-pin TAP Connectors...........................................................................11

Figure 4-1. Controller Configuration Screen.............................................................................................15

Figure 4-2. PXIE-1149.1/4E Setup Screen ..............................................................................................16

Figure A-1. Standard TAP connector (top view)......................................................................................23

Figure A-2. TAP Connector Schematic.....................................................................................................25

Figure A-3. Boundary-scan Flash Programming 16 Pin TAP Connector (top view) .........................26

Figure A-4. Flash Programming TAP Connector Schematics ...............................................................28

Figure A-5. Boundary-scan Flash Programming 20-Pin TAP Connector (top view).........................29

Figure A-6. 20-pin TAP Connector Schematic for JTAG .......................................................................31

Figure B-1. Self-Test Results for the PXIE-1149.1/4E..........................................................................33

vi

List of Tables

Table 1-1. Programmable TCK Frequencies ...............................................................................................3

Table 1-2. PXIE-1149.1/4E DC and Switching Characteristics ..............................................................6

Table 3-1. JTAG Connector Pin Assignments (Default) ........................................................................13

Table 3-2. I2C/SPI Connector Pin Assignments (Default)....................................................................14

Table A-1. Signal Description and Termination .......................................................................................24

Table A-2. Standard 10-Pin TAP Connector ............................................................................................24

Table A-3. Flash Programming TAP 16 Pin Connector .........................................................................27

Table A-4. Signal Description and Termination.......................................................................................27

Table A-5. Flash Programming TAP 20-Pin Connector.........................................................................30

Table A-6. Signal Description and Termination.......................................................................................30

Product Overview

1

Chapter 1:

Product Overview

Introduction

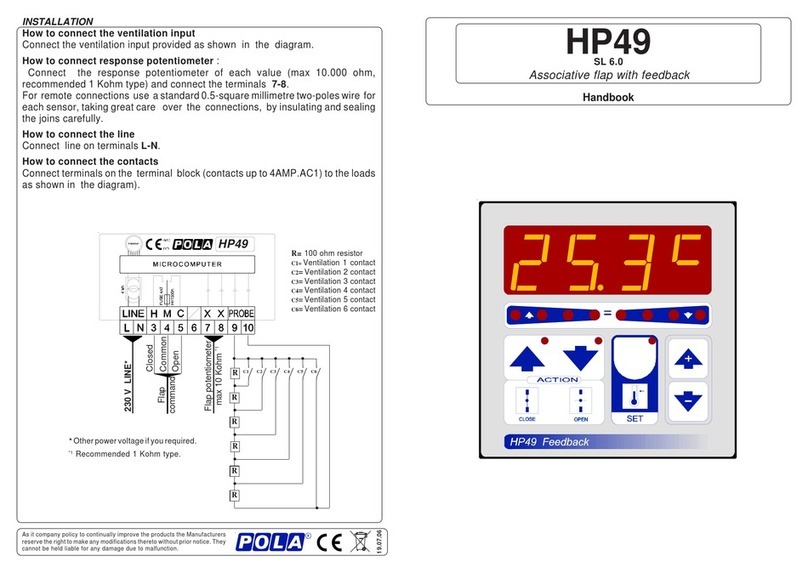

The PXIE-1149.1/4E High-Speed Boundary-Scan (JTAG) Controller is a member of the Corelis

ScanExpress™ family of scan-based test, analysis, and diagnostic tools. The PXIE-1149.1/4E

interfaces between a PC equipped with a PXIE bus and any IEEE Standard 1149.1 compatible

target. The PXIE-1149.1/4E is designed to control the operation of an IEEE Standard 1149.1

boundary-scan (JTAG) test access port (TAP) by generating the proper signals under software

control to interface with the target device. It contains memory-behind-the-pin architecture and

supports scan operations at continuous JTAG clock (TCK) speeds of up to 75 MHz.

Figure 1-1. PXIE-1149.1/4E Boundary-scan Controller

Product Overview

2

What is IEEE Standard 1149.1?

The PXIE-1149.1/4E facilitates software-controlled boundary-scan operations per IEEE Standard

1149.1. It provides command access to the target’s Test Access Port (TAP), accessing device

internal registers and on-chip debugger, verifying PCB interconnects, performing functional testing

and debug, without manual probing. The JTAG interface also provides access to internal device

functions that are not accessible via external probing, thus enabling fault isolation within the device

itself. The JTAG interface also enables programming target Flash and CPLD devices, as well as data

download and uploading to and from the target memory devices.

The PXIE-1149.1/4E is often used to perform microprocessor emulation via the device JTAG port.

It is used for firmware development providing single-step, break, and content update/visibility

access.

The IEEE-1149.1TestAccess Port

Interface (TAP)consists offour

required signals:

TestMode Select(TMS)

TestClock (TCK)

TestData In(TDI)

TestData Out(TDO)

A fifthsignal is defined as optional:

TestReset(TRST*)

TMS

TCK

TDI

TDO

TRST*

T

A

P

Figure 1-2. Minimal Test Access Port

Features of the PXIE-1149.1/4E

The Corelis PXIE-1149.1/4E is a sophisticated test controller that can access devices, boards or

systems that are compliant with IEEE Standard 1149.1. The PXIE bus-compatible card supports up

to four JTAG boundary-scan chains (TAPs). In addition, three general purpose, bi-directional

discrete I/O signals per TAP can test or control non-boundary-scan areas of the unit under test

(UUT). The discrete I/O signals can also assist in greatly expediting certain long scan activities,

such as Flash programming. With its software-controlled voltage translating logic for all the above

signals, the PXIE-1149.1/4E can test low-voltage systems.

The PXIE-1149.1/4E also contains several performance enhancing functional sections aimed at

streamlining test vector throughput and emulator target download/upload transfers. Key functional

elements include the TAP controller, and the memory resources that support it. The on-board

memory provides scan data buffering and can at times store the entire scan data for maximum

performance, real-time scan operations.

A test system operates the TAP controller and its associated memory through the host PXIE Port,

while the Test Clock (TCK) rate can operate up to 100 MHz depending on selected signal voltages

and target conditions. The on-board memory elements further decouple the scan operations from

the host software. A hardware state machine that contains status and control registers accessible

through the PCIE interface directly controls all functions of the PXIE-1149.1/4E.

Product Overview

3

Hardware mechanisms enable optimal data flow between the PCIE port and the memory resources

paced by the port and/or scanning rates underway, in both directions.

A programmable, time-delay skew compensation mechanism supports the PXIE-1149.1/4E’s high

TCK rates. It accommodates the returned, target scan stream-delays due to signal travel time down

and up the cable. It can also adjust for a target’s internal TCK-to-TDO response delay.

Adjustable Voltage Levels

The software-programmable voltage level of the TAP interfaces and discrete I/O can be set to any

voltage between 1.25 V and 3.30 V in increments of about 0.05V. Each of the four TAPs has its

own programmable voltage settings.

Discrete Input/Output Signals

The PXIE-1149.1/4E operates three discrete input/output signals under software control. These

attach to the target TAP connector. They are driven or sensed as directed by software, in

coordination with the scanning operation. Each signal can be configured independently as TTL

output, open-collector (open-drain) output, or as input at the programmable voltage level. As open-

collector drivers, they can readily tie to similar target signals without the need to alter its circuitry, yet

still gain control of related functions, such as a Flash write signal.

As outputs, these discrete signals are useful for providing control functions on the user target system

such as general reset, power control, device write pulse, disable/enable and/or similar signals for

non-boundary-scan target stimulus.

Conversely, as inputs, they enable host sensing of the target to pace scanning activity or related

conditions (such as a Flash ready signal).

PXIE Interface

The PXIE-1149.1/4E is a PXI peripheral module that fits in a 3U slot utilizing 1 lane of PCIe. This

PXI interface supplies the power to operate the PXIE-1149.1/4E. The PXIE-1149.1/4E is not hot

pluggable. Power should be off while install and removing the PXIE-1149.1/4E controller.

Programmable Clocks

The PXIE-1149.1/4E’s programmable TCK output to the IEEE Standard 1149.1 compatible target

system can be configured over a wide range of frequencies, using on-board clock-generation

circuitry. A programmable Phase Locked Loop (PLL) enables a wide range as well as fine- selection

resolution. See Table 1-1 for the set of programmable values.

TCK range (MHz)

Rate Resolution (MHz)

15 to 75

1

1 to 15

0.5

0.05 to 1

0.05

Table 1-1. Programmable TCK Frequencies

Product Overview

4

Controllable Slew Rate

The PXIE-1149.1/4E supports slow or fast slew rate on the outputs.

Software Pin Configuration

The PXIE-1149.1/4E’s pins are remappable in the ScanExpress software.

Pin Protection

The PXIE-1149.1/4E features voltage-detection circuitry to prevent the drivers from being

damaged if the outputs are inadvertently shorted to power or ground.

Product Overview

5

PXIE-1149.1/4E Hardware Specifications

Physical

Mechanical Dimensions (box)

8.5 inches x 0.8 inches x 5.1 inches (+/-

0.25”)

Operating Environment

Temperature

0°C to 55°C

Relative Humidity

10% to 90%, non-condensing

Storage Environment

Temperature

-40°C to 85°C

Host Interface

PXI interface

3U slot using 1 lane of PCIE.

Required Host CPU

Pentium III @ 1GHz or better

Required Operating System

Windows 7, Windows 10

Power Requirements

12V, 3.3V

Provided by the PXI interface. No external

power supply needed.

Product Overview

6

PXIE-1149.1/4E Electrical Specifications

JTAG TAP Interface

PXIE-1149.1/4E TAP Connectors

20-pin (2x10) IDC header (0.050” x 0.100"),

AMP/Tyco part number 5-104069-1

PXIE-1149.1/4E TAP Connector

Mating Connectors

20-pin (2x10) IDC receptacle (0.050” x 0.100"),

AMP/Tyco part number 1-111196-8 or equivalent

Minimum TCK Frequency

0.05 MHz

Maximum TCK Frequency

75 MHz

TCK Frequency Steps

0.05 MHz increments between 0.05 and 1 MHz

0.50 MHz increments between 1 and 15 MHz

1.0 MHz increments between 15 and 75 MHz

Maximum scanning data length

unlimited

Programmable Voltage (V_adj) Range

1.25V to 3.3V in 0.05V steps

Symbol

Test Conditions

Limit Min

Limit Max

Units

VIH

V_adj >= 2.7 V

2

V_adj + 0.5

V

V_adj < 2.7 V

0.65 × V_adj

V_adj + 0.5

V

VIL

V_adj >= 2.7

0.8

V

V_adj <= 2.0

0.35 × V_adj

V

VOH

IOH= -12 mA

V_adj –0.5

V

VOL

IOL = 12 mA

0.4

V

Table 1-2. PXIE-1149.1/4E DC and Switching Characteristics

PXIEPXIE-1149.1/4E Installation

7

Chapter 2:

PXIE-1149.1/4E Installation

Installing the ScanExpress software and PXIE-1149.1/4E hardware

The PXIE-1149.1/4E product consists of the following components:

•PXIE-1149.1/4E Hardware

•PXIE-1149.1/4E User’s Manual

•One 80-pin to Four 20-pin TAP Cable, Corelis P/N 15467

Please ensure that all items listed above are present and free from visible damage or defects before

proceeding. If anything appears to be missing or damaged, immediately contact Corelis at the

number shown on the title page of this manual.

Software Must Be Installed.

The PXIE-1149.1/4E installation procedure requires the use of software that contains the driver for

the PXIE-1149.1/4E module. Obtain the ScanExpress CD-ROM (or any other Corelis application

that supports the PXIE-1149.1/4E module) in order to proceed with installation. Install the PXIE-

1149.1/4E controller before installing the ScanExpress Application Software.

PXIE-1149.1/4E Hardware Installation

To install the PXIE-1149.1/4E on a host PC, follow the installation steps below. Plug in the PXIE-

1149.1/4E controller into an available PXIE port on the host PC while powered down. The

following section describes this process in detail for installing using Windows 7 and Windows 10.

Note that depending on the version of Windows used, the procedure may differ slightly.

Installation Steps

1. While powered down, install the PXIE-1149.1/4E module into the any available PXIE

peripheral slot. Then power on.

2. Install the application software, such as “ScanExpress Runner,”from the CD on your

computer.

PXIEPXIE-1149.1/4E Installation

9

5. The following dialog box as shown in Figure 2-2 will pop up. Select “Install the software

automatically (Recommended)” and click on the Next button.

Figure 2-2. Found New Hardware Wizard

6. After the necessary files are copied to the system, the following dialog box, Figure 2-3, will

pop up indicating that the device driver is successfully installed.

Figure 2-3. Installation Successfully Completed

PXIE-1149.1/4E Installation

10

7. Click on the Finish button to close the dialog box.

8. The installation of the device drivers is now completed. Verify that the PXIE-1149.1/4E is

correctly installed by checking for its entry in the Windows Device Manager. To run the

Device Manager, right-mouse click on the My Computer icon and then select Properties.

Choose the Hardware tab and click on the Device Manager button. Corelis USB-

1149.1/4E JTAG Controller should be listed in the Universal Serial Bus controller

section as shown in Figure 2-4.

Figure 2-4. Windows Device Manager

Congratulations! The PXIE-1149.1/4E drivers have now been successfully installed on your

computer and the controller is now ready to be used. We suggest that you preserve the original

packing material for the future shipment or storage of the PXIE-1149.1/4E.

Using the PXIE-1149.1/4E with ScanExpress

11

Chapter 3:

Connecting to the Target

Connecting to the Target

The connection to the target board/system is through the TAP connectors on the front of the

PXIE-1149.1/4E. Figure 3-1 shows the front view of the PXIE-1149.1/4E box, including the four

TAP connectors, which are clearly marked on the cable: TAP 1, TAP 2, TAP 3 and TAP 4.

Figure 3-1. PXIE-1149.1/4E 80-pin TAP Connectors

Using the PXIE-1149.1/4E with ScanExpress

12

The following PXIE-1149.1/4E TAP connectors are connected to the target board:

TAP1 - when the target has a single TAP connector

TAP1 and TAP2 - when the target has 2 TAP interface connectors

TAP1, TAP2 and TAP3 - when the target has 3 TAP interface connectors

TAP1, TAP2, TAP3 and TAP4 - when the target has 4 TAP interface connectors

To connect the TAP cables to the target (UUT), follow these steps in the order as follows:

1. Verify that the target power is OFF.

2. Plug the TAP cable connector to the mating target header.

3. Now you can turn the target power ON.

ALERT !

Make sure your target board is connected to GROUND prior to powering up the target

board. This assures that the target-power return flows through its power supply return

(GND) signal and not through the ground wire of the PXIE. Otherwise, with a ‘floating’

target, if the user hot-plugs the target power cable from its external supply (such as a ‘brick’ type

power supply), there is no guarantee that the ground will make contact with the target first,

before the power does. In such case, it is possible to momentarily engage the voltage pin of the

target power supply connector prior to engaging the ground (return) pin. During such action, all

target current will momentarily flow through the PXIE to ground, with the resulting transients

possibly resetting the PXIE-1149.1/4E unit.

Table of contents

Popular Controllers manuals by other brands

socomec

socomec ATyS A15 instruction manual

Herz

Herz clever&smart Control Box Clima instruction manual

Lumiax

Lumiax Magicube Series user manual

Leroy-Somer

Leroy-Somer Nidec R180 Installation and Maintenance

Emerson

Emerson Vilter MicroVission Operation and service manual

vacuubrand

vacuubrand CVC 3000 Instructions for use