FII-PRA006/010 Hardware Reference Guide

Fraser Innovation Inc

3 / 38

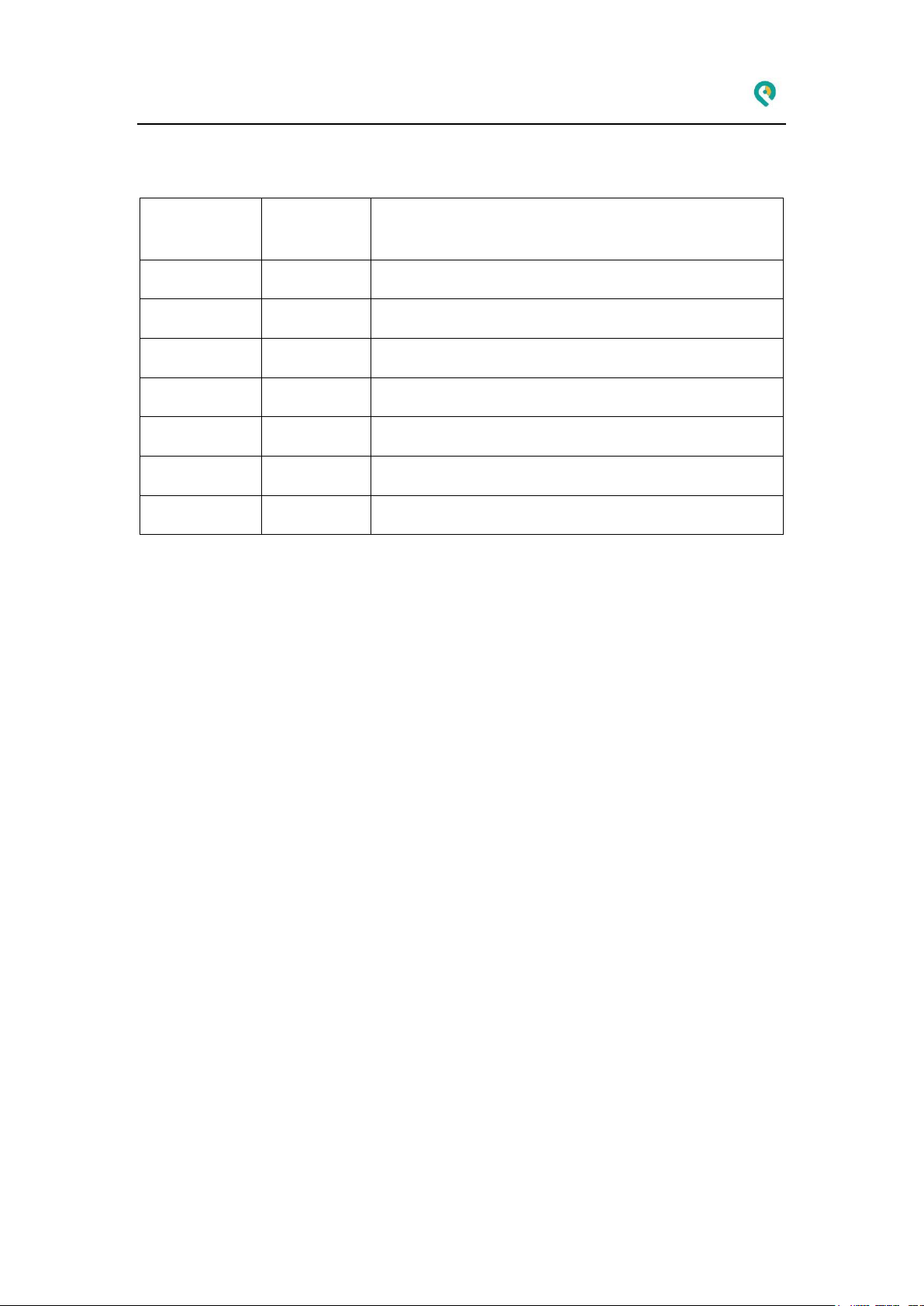

Contents

1. Introduction..................................................................................................................................... 5

2. Basic Features................................................................................................................................. 9

1)FPGA................................................................................................................................................. 9

2)USB Interface................................................................................................................................ 9

3)Oscillator ......................................................................................................................................12

4) Segment LED Display...........................................................................................................13

5)VGA Interface............................................................................................................................. 16

6)EEPROM AT24C02................................................................................................................... 20

7)Gigabit Ethernet Interface...................................................................................................22

8)Push Button ................................................................................................................................25

9)AD/DA Thermistor, Photoresistor and Potentiometer........................................26

10)DIP Switch.................................................................................................................................28

11)LED................................................................................................................................................ 30

12)FLASH Configuration Chip...............................................................................................32

13)GPIO Expansion Bus ............................................................................................................32

14)JTAG Interface.........................................................................................................................35

3. References .........................................................................................................................37