Holt Integrated Circuits

7

First Things First

In order to successfully execute the Holt demo program the PC must be able to detect the card’s PCIe

interface at power up.

1. Reviewing the Holt QSG-2130mPCIe.pdf prior to reading this document is highly recommended.

2. Linux experience and the terminal window with the command line are highly recommended.

3. Power down the PC and install the Holt Mini PCIe card. Connecting the break-out board is not

critical for this step so is optional.

4. The Ubuntu OS on the Holt FD cannot be used to install Ubuntu on a user’s PC. If the user has an

older version of Ubuntu than 18.04 LTS it may be possible to upgrade it.

We recommend downloading Ubuntu 18.04 LTS from the Ubuntu website and using the

provided installation instructions. Holt has not tried any other Linux version as of this date.

Windows support is planned in the future.

https://ubuntu.com/#download

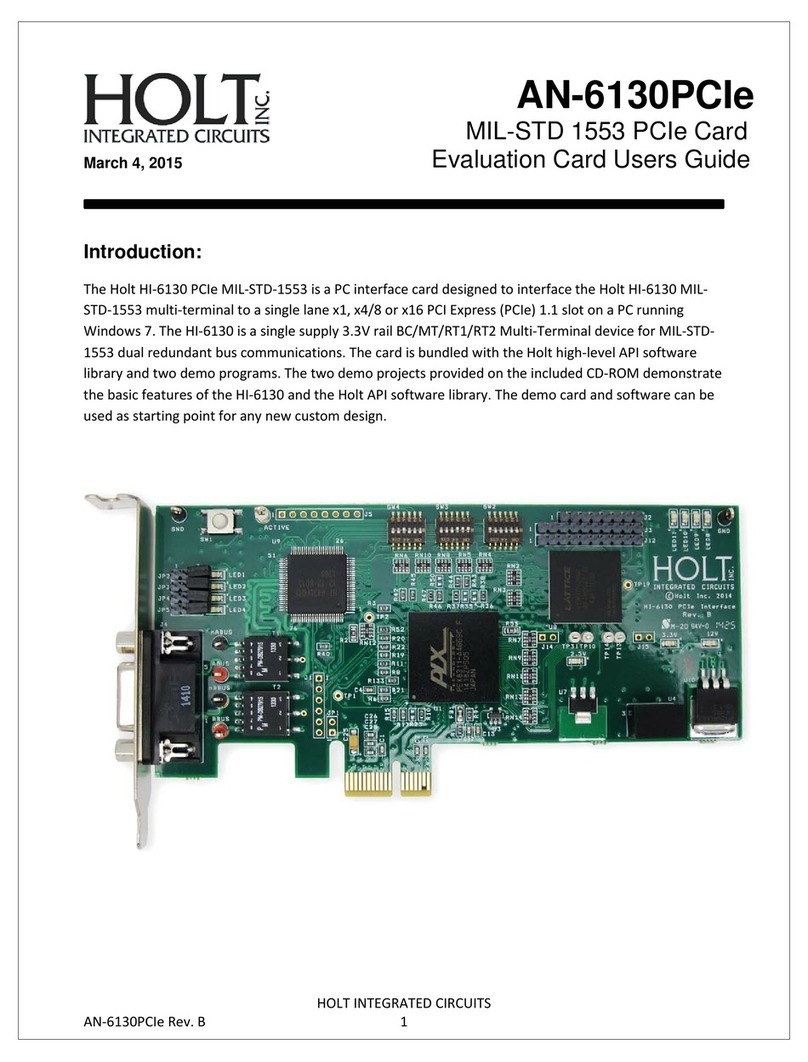

5. Power up the PC. Shortly after powering up the computer the green PCIe Link LED 8 should be

on and the Heart Beat LED 9 should flash on and off.

6. When LED 8 illuminates, the computer boot up sequence has detected the PCIe link on the card.

Another way to verify this is to open a terminal window and execute the following command.

holt@holt-desktop:~/holt$ lspci | grep Xilinx

“Memory controller: Xilinx Corporation Device 7011”

If this is displayed the PC successfully detected the PCIe link.

If the ‘Xilinx Corporation Device 7011” was not displayed try turning off the PC and reinstalling

the card making sure the card is fully plugged in. If the LED’s never light up it might be due to

missing 1.5V on the Mini PCIe slot. Refer to the PC motherboard manual to see if 1.5V needs to

be enabled by a configuration or jumper setting. Another PC may need to be used.