UM_APIX2_ADK_TX (Rev2) Revision 1.2_A1 Inova Semiconductors Confidential Page 2 of 37

User Manual

Table of Contents

1.0 Introduction ......................................................................................................................................... 1

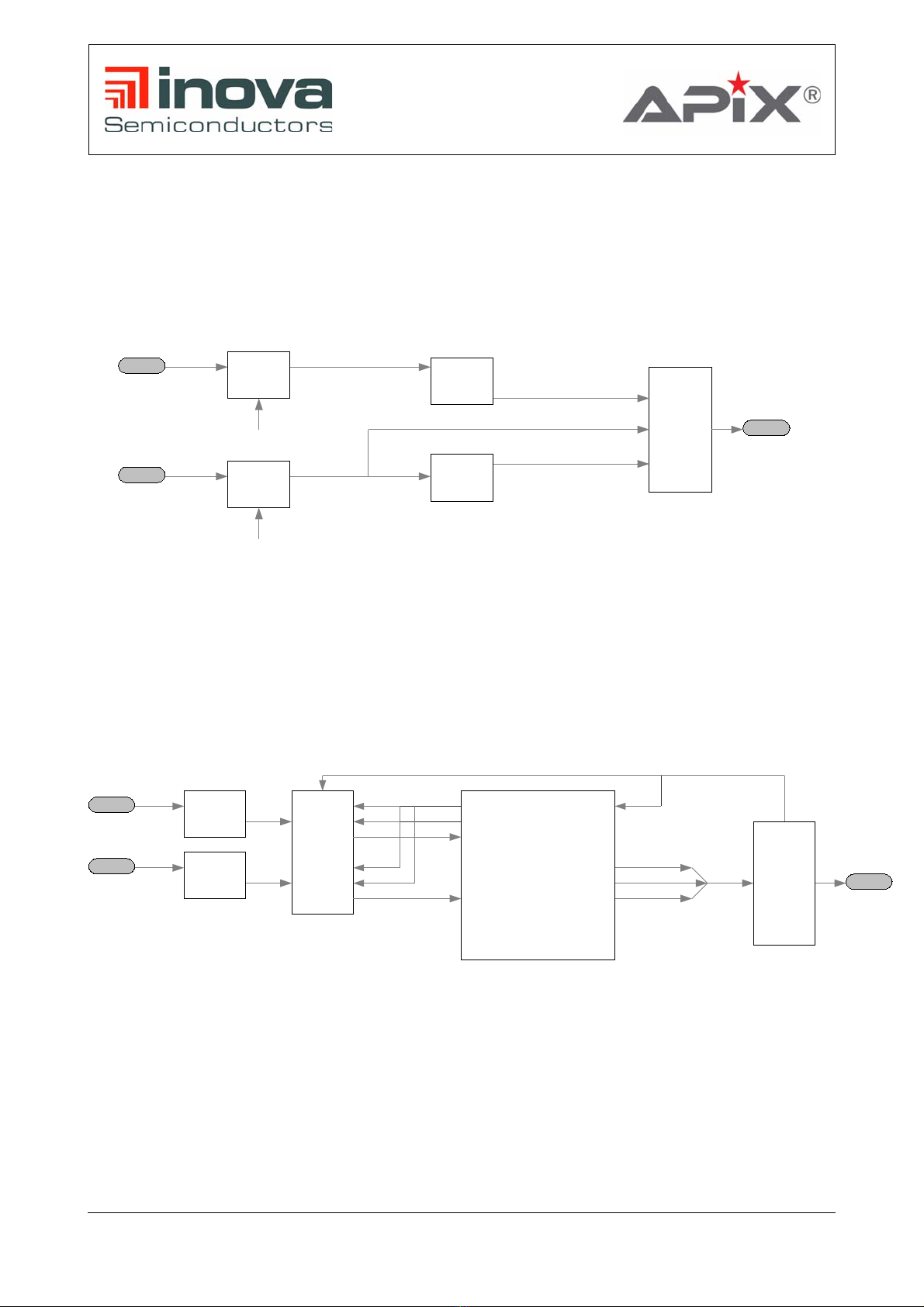

2.0 Functional description ........................................................................................................................ 5

2.1 Video path ........................................................................................................................................... 5

2.2 Audio path ........................................................................................................................................... 5

2.3 Control path ........................................................................................................................................ 5

3.0 Hardware description ......................................................................................................................... 7

3.1 Board connectors ................................................................................................................................ 7

3.1.1 Standard connectors and interfaces .............................................................................................. 7

3.1.2 Connectors and interfaces for bench setups ................................................................................. 7

3.1.3 Connectors and interfaces to expansion boards ............................................................................7

3.1.4 Top Side ......................................................................................................................................... 8

3.1.5 Bottom Side ................................................................................................................................... 9

3.1.6 Connector and interface pin description ...................................................................................... 10

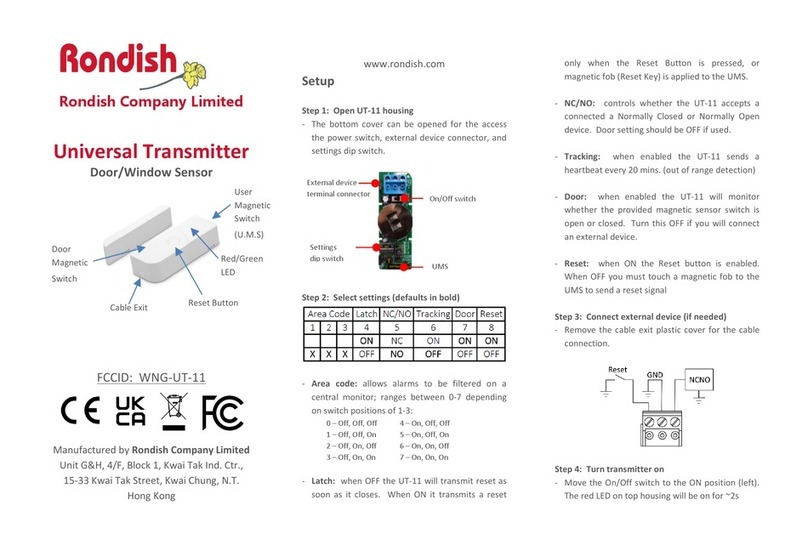

3.1.7 DIP Switches and buttons ............................................................................................................ 16

3.1.8 Jumpers ....................................................................................................................................... 18

4.0 Hardware Configurations ................................................................................................................. 19

4.1 Power supply .................................................................................................................................... 19

4.1.1 12V Main Board supply ................................................................................................................ 19

4.1.2 Low noise board supply ............................................................................................................... 19

4.1.3 Power over APIX (PoA) ............................................................................................................... 19

4.2 Reset ................................................................................................................................................. 19

4.3 LED Indicators .................................................................................................................................. 20

5.0 Microcontroller - NXP LPC1768 ....................................................................................................... 21

5.1 Port description ................................................................................................................................. 21

6.0 Extension Boards (optional) ............................................................................................................ 24

6.1 Ethernet Extender Board .................................................................................................................. 24

6.1.1 Description ................................................................................................................................... 24

6.1.2 Board Setup ................................................................................................................................. 26

6.2 I/O Extender board ............................................................................................................................ 28

6.2.1 Description ................................................................................................................................... 28

6.2.2 Connector description .................................................................................................................. 28

6.2.2.1 Top view .................................................................................................................................. 28

6.2.2.2 Bottom view ............................................................................................................................ 29

6.2.3 Board setup .................................................................................................................................. 32

7.0 Troubleshooting ................................................................................................................................ 34

7.1 Possible Issues ................................................................................................................................. 34

7.2 Reset LVDS transmitters .................................................................................................................. 34

8.0 Ordering information ........................................................................................................................ 36

9.0 Revision History ................................................................................................................................ 36

10.0 References ....................................................................................................................................... 36