CHAPTER 1

GENERAL INFORM ATION Page

Introduction ....... . ......... . . ......... . .. . . . . I-I

Description. ................................... 1-1

Equipment Supplied 1-2

Specifications. . . . . .. . . . . . ......... . ........... . 1-2

CHAPTER 2

PREPARATION FOR USE Page

Introduction . ............... . .............. . . . . 2-1

Unpacking and Inspection. . ...................... 2-1

Installation Considerations2-1

Power Requirement. ............ . . . ...........2-1

Cooling Requirement 2-1

Physical Dimensions . .................. . ... . . . 2-1

Bus Interface Requirements. . ............. . . . . . 2-1

Jumper Configurations 2-1

Memory Base Address 2-5

Multiplexer Input. ...... . ..... . ........... . . . . 2-6

ADC Configuration........................... 2-6

ADC Trigger . . .............................. 2-6

Interrupts . . .......... . ...... . ....... . . . . . ... 2-7

Transfer Acknowledge Delay................... 2-7

Auxiliary Power (Special) . . ..................... . 2-8

Multiplexer Channel Expansion.................. . 2-9

Current Loop InputResistors ... . ................ . 2-9

Analog Input Cabling .. ......................... 2-10

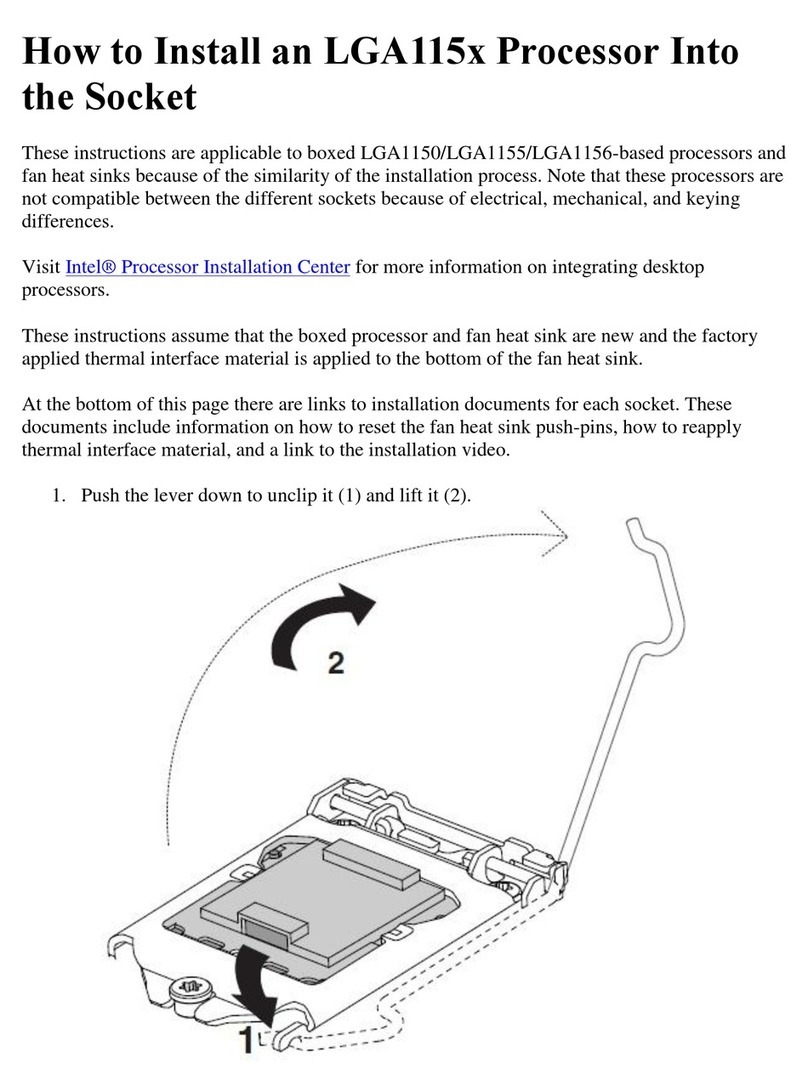

Board Installation 2-13

CHAPTER 3

PROGRAMMING INFORMATION Page

Introduction .................................. . 3-1

Memory Base Address 3-1

Memory Address Assignments.. . ............. . .. . 3-1

Read/Write Formats 3-1

Multiplexer Address andGain. ................. 3-1

Last Channel .. .............................. 3-2

Command................................... 3-2

Status. .................................. . . . 3-2

Clear Interrupt Bit. .. . ........................ 3-2

ADC Data 3-2

Programming Examples 3-3

ONTENTS

I

CHAPTER 4

PRINCIPLES OF OPERATION Page

Introduction ............. . . .. . ................ . 4-1

Functional Description 4-1

Analog Input Multiplexer . . . . ......... . ..... . .. 4-1

Programmable Gain Amplifier. . ........ . ....... 4-1

Sample-and-Hold Amplifier. . . .. . ..............4-1

Analog-to-Digital Converter. . ....... . . ........ . 4-1

DC-DC Converter.... . . . . .. . ...4-1

Control and Bus Interface. . . .................. . 4-1

Circuit Analysis. . . . . ......................... . . 4-1

Initialization. ............................... . 4-2

Base Address Decoding 4-2

Command Decoding. ... .. .... . .4-2

Write Commands. ....................... . . . 4-2

Read Commands. ....... . .................. 4-2

Data Buffers 4-5

Registers 4-5

Command Register . ..... . ..................4-5

Multiplex Address Register 4-5

Last Channel Register. .......... . ......... . . 4-5

Status Register. ........... . . . .......... . . ..4-5

Analog Input Operation 4-6

Random Channel . . . .............. . . .... . ... 4-6

Repetitive Single Channel.................... 4-7

Sequential Channel Scan. . .............. . . . . . 4-7

CHAPTER 5

SER VICE INFORM ATION Page

Introduction . . . ..................... . ..........5-1

Calibration . . ................ . ............... . . 5-1

Test Equipment Required . ..... . . . ............. 5-1

Preliminary Procedure. ........................ 5-1

ADC Calibration Procedure 5-1

PGA Offset..................... . ........ . 5-1

ADC Offset. ............................. . 5-1

ADC Range. ..............................5-2

Service Diagrams 5-2

Reshipment 5-2

APPENDIX A

CALIBRA TION PROGRAM