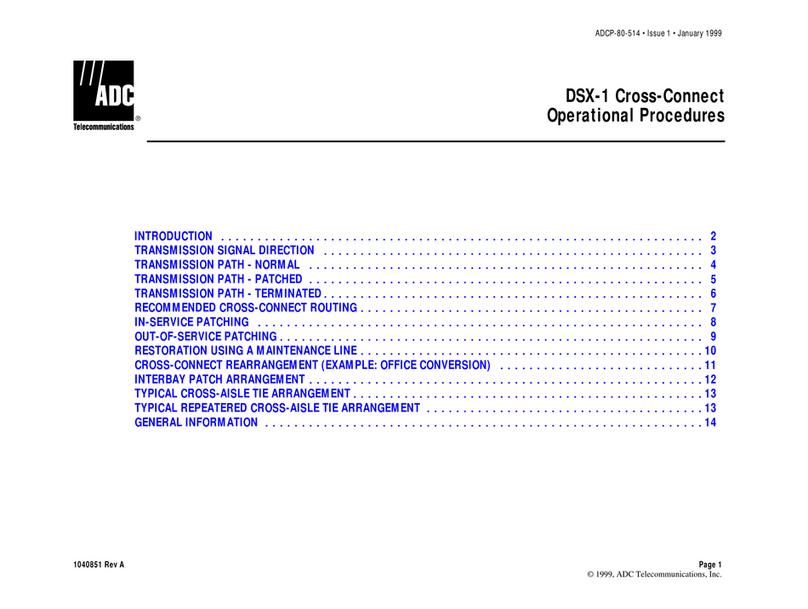

Intel®IXP45X and Intel®IXP46X Product Line of Network Processors—Contents

Intel®IXP45X and Intel®IXP46X Product Line of Network Processors

Developer’s Manual August 2006

4Order Number: 306262-004US

3.1 Memory Management Unit ..................................................................................69

3.1.1 Memory Attributes ..................................................................................70

3.1.1.1 Page (P) Attribute Bit.................................................................70

3.1.1.2 Cacheable (C), Bufferable (B), and eXtension (X) Bits ....................70

3.1.2 Interaction of the MMU, Instruction Cache, and Data Cache..........................72

3.1.3 MMU Control ..........................................................................................73

3.1.3.1 Invalidate (Flush) Operation .......................................................73

3.1.3.2 Enabling/Disabling.....................................................................73

3.1.3.3 Locking Entries .........................................................................74

3.1.3.4 Round-Robin Replacement Algorithm ...........................................76

3.2 Instruction Cache ..............................................................................................77

3.2.1 Operation When Instruction Cache is Enabled.............................................77

3.2.1.1 Instruction-Cache ‘Miss’ .............................................................78

3.2.1.2 Instruction-Cache Line-Replacement Algorithm..............................79

3.2.1.3 Instruction-Cache Coherence ......................................................80

3.3 Branch Target Buffer..........................................................................................83

3.3.1 Branch Target Buffer (BTB) Operation .......................................................83

3.3.1.1 Reset.......................................................................................85

3.4 Data Cache.......................................................................................................85

3.4.1 Data Cache Overview ..............................................................................85

3.4.2 Cacheability...........................................................................................88

3.4.3 Reconfiguring the Data Cache as Data RAM................................................92

3.5 Configuration ....................................................................................................96

3.5.1 CP15 Registers.......................................................................................98

3.5.1.1 Register 0: ID & Cache Type Registers.........................................98

3.5.1.2 Register 1: Control and Auxiliary Control Registers ......................100

3.5.1.3 Register 2: Translation Table Base Register ................................102

3.5.1.4 Register 3: Domain Access Control Register................................102

3.5.1.5 Register 4: Reserved ...............................................................102

3.5.1.6 Register 5: Fault Status Register ...............................................102

3.5.1.7 Register 6: Fault Address Register.............................................103

3.5.1.8 Register 7: Cache Functions......................................................103

3.5.1.9 Register 8: TLB Operations.......................................................104

3.5.1.10 Register 9: Cache Lock Down....................................................105

3.5.1.11 Register 10: TLB Lock Down .....................................................106

3.5.1.12 Register 11-12: Reserved.........................................................106

3.5.1.13 Register 13: Process ID............................................................106

3.5.1.14 The PID Register Affect On Addresses ........................................107

3.5.1.15 Register 14: Breakpoint Registers..............................................107

3.5.1.16 Register 15: Coprocessor Access Register...................................107

3.5.2 CP14 Registers.....................................................................................108

3.5.2.1 Performance Monitoring Registers..............................................109

3.5.2.2 Clock and Power Management Registers.....................................109

3.5.2.3 Software Debug Registers ........................................................110

3.6 Software Debug...............................................................................................111

3.6.1 Definitions ...........................................................................................111

3.6.2 Debug Registers ...................................................................................111

3.6.3 Debug Modes .......................................................................................112

3.6.3.1 Halt Mode ..............................................................................112

3.6.3.2 Monitor Mode..........................................................................112

3.6.4 Debug Control and Status Register (DCSR) ..............................................112

3.6.4.1 Global Enable Bit (GE) .............................................................114

3.6.4.2 Halt Mode Bit (H) ....................................................................114

3.6.4.3 Vector Trap Bits (TF,TI,TD,TA,TS,TU,TR) ....................................114

3.6.4.4 Sticky Abort Bit (SA)................................................................114

3.6.4.5 Method of Entry Bits (MOE) ......................................................114

3.6.4.6 Trace Buffer Mode Bit (M).........................................................114