R34UZ0015EU0102 Rev.1.02 Page 6

Feb 7, 2024

ISLVERSALDEMO2Z Demonstration Board Manual

The VCC PSFP, VCC SOC I/O, VCC PMC and VCC PSLP rails can be adjusted for 0.8V or 0.88V. See Tab l e 5 .

1.4 Output Voltage Monitor Test Points and Load Transient Generators

The ISLVERSALDEMO2Z provides test points for monitoring the output voltage and terminals to apply an external

load current. Certain output rails also provide an onboard transient load generator for a step load. Table 6

summarizes output rail monitoring, test points, and load transient generator input control for the supply rails.

The transient load generator comprises a FET driver controlling a common source NFET that pulls a load resistor

to GND to provide a transient load to the supply rail. The ISL73847_VCCINT 0.8V core rail uses an

ISL71040MRTZ GaN FET driver, while all other load generators use the HIP2211FBZ half-bridge driver. In both

cases, a 0V-5V logic control signal is used to switch the transient load where 0V turns the load off, and 5V turns

the load on. Figure 3 through Figure 8 show the input connection to the transient load generator control. The load

comprises multiple parallel 2W-rated, 2512-sized resistors. The transient load generator is intended for pulse load

operation only where the frequency and duty cycle of the load do not exceed the power dissipation of the

resistors.

Table 5. VCC PSFP, VCC SOC I/O, VCC PMC and VCC PSLP Rail Adjustments

VOUT Jumper Status VCC PSFP VCC SOC I/O VCC PMC VCC PSLP

0.8V Jumper Open

JP452 JP1002 JP551 JP351

0.88V Jumper Short

Table 6. Output Rail Test Points and Transient Load Control Input Connection

ISLVERSALDEMO2Z Node

Name

Oscilloscope Test Point

(2pin jumper)

DC Test Point/External Load

Access (VOUT/GND)

Transient Load

Generator Control

ISL73847_5V0_SYS TP701

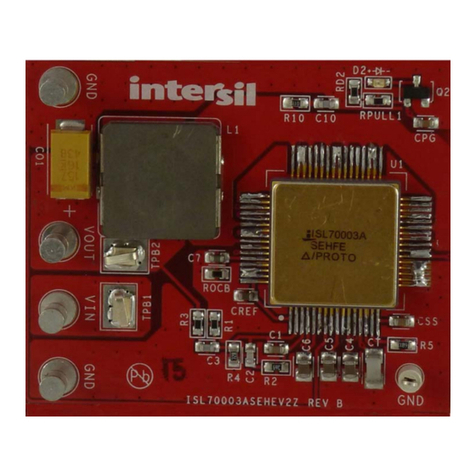

ISL70003A_3V3_SYS TP501 P501/P502

ISL73007_VCCO_50x TP1051 P1051/P1052

ISL73007_VCCO_XPIO TP1101 P1101/P1102 JP1104

ISL73007_VCC_PSFP TP451 P451/P452 JP453

ISL70001A_VCC_SOC/IO TP1001 P1001/P1002 JP1003

ISL73006_VCC_PMC TP551 P551/P552

ISL73006_VCC_PSLP TP351 P351/P352

ISL73847_VCCINT TP1 TERM1/TERM2 TP22

ISL70001A_VCCAUX TP901 P901/P902 JP902

ISL73006_VCCAUX_SMON/PMC TP951 P951/P952

ISL73007_GTY_AVCC TP251 P251/P252

ISL73006_GTY_AVCCAUX TP401 P401/P402

ISL73007_GTY_AVTT TP201 P201/P202 JP201

ISL73005_DDR_VDD TP801 P801/P802

ISL73005_DDR_VTT TP802 P803/P804

ISL73006_DDR_VPP TP851 P851/P852