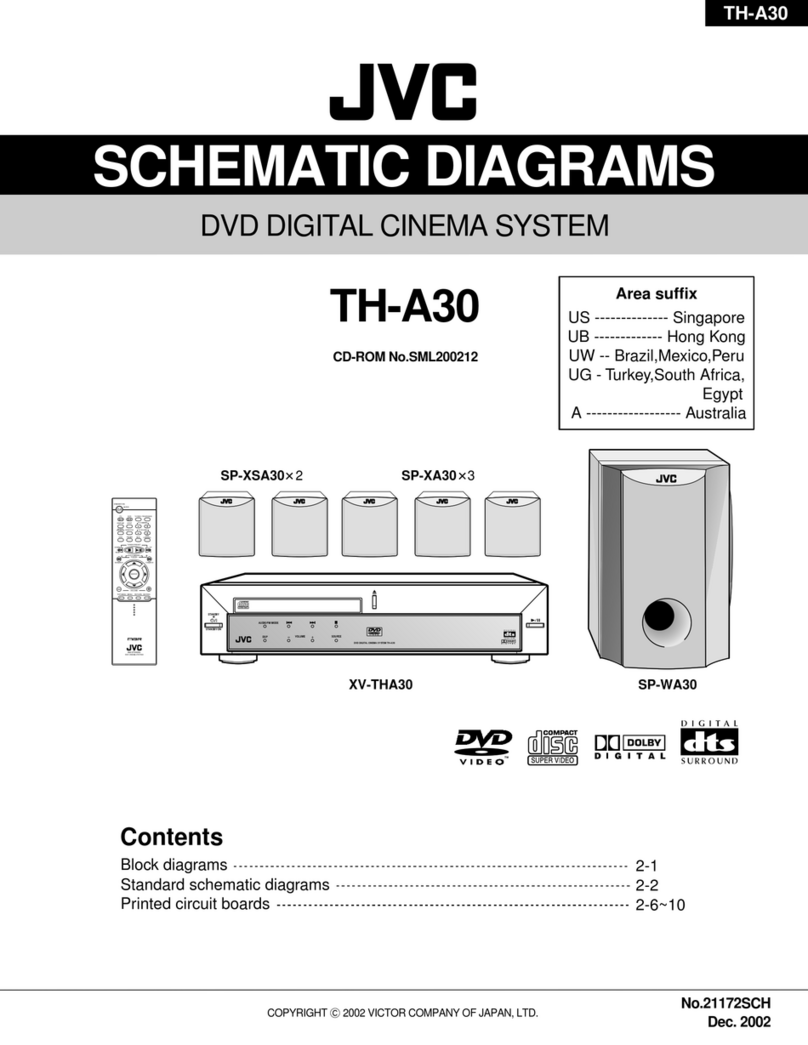

TH-A30

1-2

1. This design of this product contains special hardware and many circuits and components specially for safety

purposes. For continued protection, no changes should be made to the original design unless authorized in

writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services

should be performed by qualified personnel only.

2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product

should not be made. Any design alterations or additions will void the manufacturer`s warranty and will further

relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

3. Many electrical and mechanical parts in the products have special safety-related characteristics. These

characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily

be obtained by using replacement components rated for higher voltage, wattage, etc.Replacement parts which

have these special safety characteristics are identified in the Parts List of Service Manual. Electrical

components having such features are identified by shading on the schematics and by ( ) on the Parts List in

the Service Manual. The use of a substitute replacement which does not have the same safety characteristics

as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or

other hazards.

4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be

separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of

electric shock and fire hazard. When service is required, the original lead routing and dress should be

observed, and it should be confirmed that they have been returned to normal, after re-assembling.

5. Leakage currnet check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts of the product

(antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the

product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage

current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return

path to the chassis, to a known good earth ground.Any leakage current must not exceed 0.5mA AC (r.m.s.).

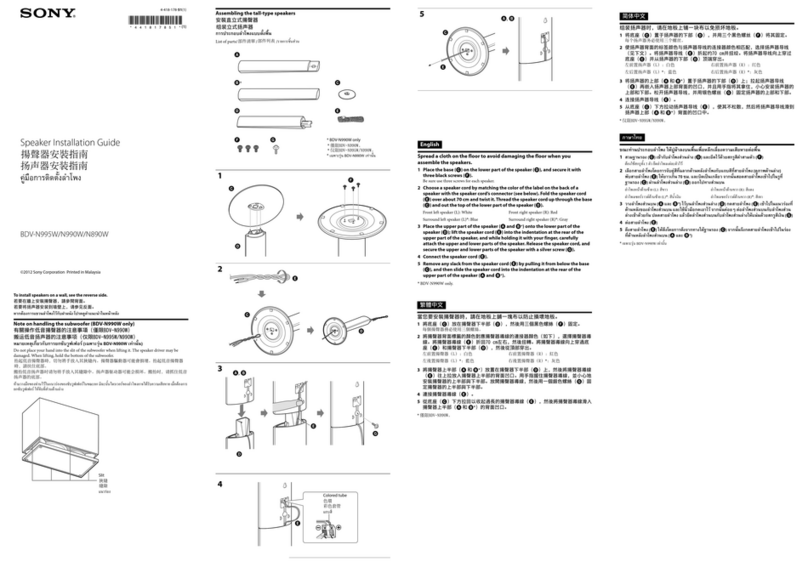

Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more

sensitivity in the following manner.Connect a 1,500 10W resistor paralleled by a 0.15 F AC-type capacitor

between an exposed metal part and a known good earth ground.

Measure the AC voltage across the resistor with the AC

voltmeter.

Move the resistor connection to each exposed metal part,

particularly any exposed metal part having a return path to

the chassis, and meausre the AC voltage across the resistor.

Now, reverse the plug in the AC outlet and repeat each

measurement.Voltage measured any must not exceed 0.75 V

AC (r.m.s.).This corresponds to 0.5 mA AC (r.m.s.).

1.This equipment has been designed and manufactured to meet international safety standards.

2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

3. Repairs must be made in accordance with the relevant safety standards.

4. It is essential that safety critical components are replaced by approved parts.

5. If mains voltage selector is provided, check setting for local voltage.

Good earth ground

Place this

probe on

each exposed

metal part.

AC VOLTMETER

(Having 1000

ohms/volts,

or more sensitivity)

1500 10W

0.15 F AC TYPE

!

Burrs formed during molding may

be left over on some parts of the

chassis. Therefore, pay attention to

such burrs in the case of

preforming repair of this system.

In regard with component parts appearing on the silk-screen printed side (parts side) of the PWB diagrams, the

parts that are printed over with black such as the resistor ( ), diode ( ) and ICP ( ) or identified by the " "

mark nearby are critical for safety.

(This regulation does not correspond to J and C version.)