7

TK-3107

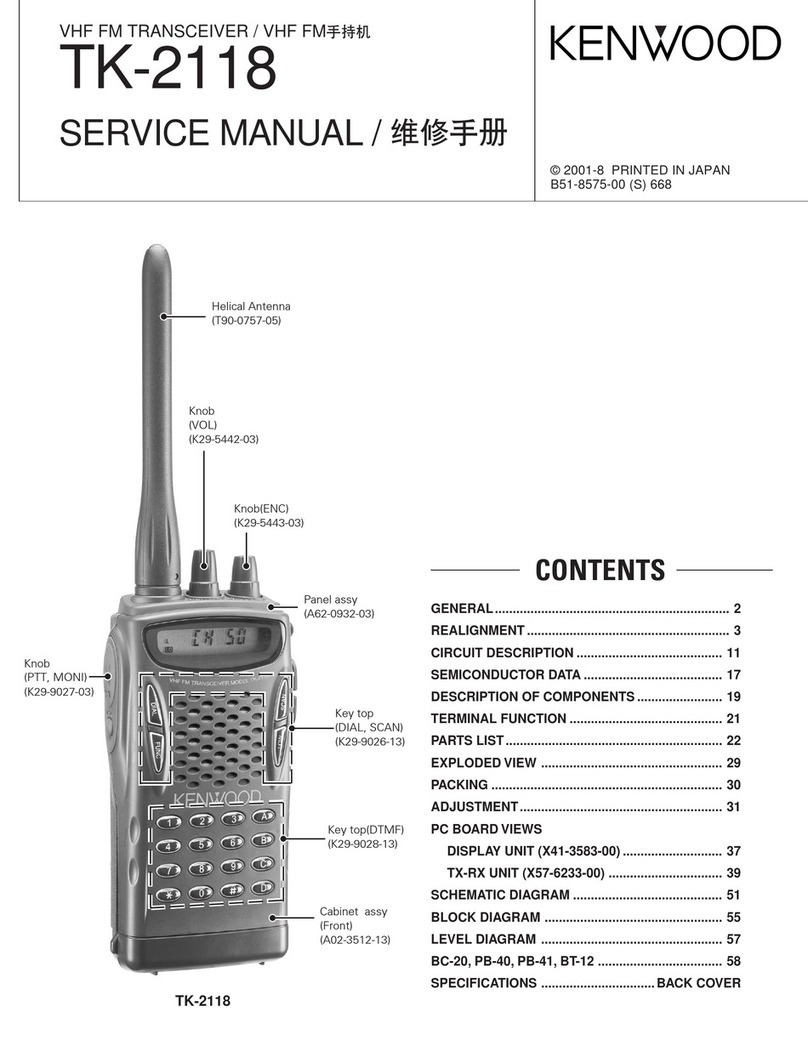

4. Transmitter

1) Transmit audio

The modulation signal from the microphone is amplified by

IC500 (1/2), passes through a preemphasis circuit, and

amplified by the other IC500 (1/2) to perform IDC operation.

The signal then passes through a low-pass filter (splatter fiIter)

(Q501 and Q502) and cuts 3kHz and higher frequencies. The

resulting signal goes to the VCO through the VCO modulation

terminal for direct FM modulation. (See Fig. 6)

2) QT/DQT encoder

A necessary signal for QT/DQT encoding is generated by

IC403 and FM-modulated to the PLL reference signal. Since

the reference OSC does not modulate the loop characteristic

frequency or higher, modulation is performed at the VCO side

by adjusting the balance. (See Fig. 6)

CIRCUIT DESCRIPTION

Fig. 6 Transmit audio QT/DQT

MUTE

VR501

MAX

DEV

BALANCE

X1, IC1

D5, Q4

VCO

REFERENCE

OSC

(TCXO)

MIC

IC500 (1/2)

MIC

AMP IC500 (1/2)

IDC

Q503

SW

PREEMPHASIS

Q501, 502

LPF

(SPLATTER FILTER)

IC403

TO QT/DQT

VR500

3) VCO and RF amplifier

The transmit signal obtained from the VCO buffer amplifier

Q100, is amplified by Q101 and Q102. This amplified signal is

passed to the power amplifier, Q105 and Q107, which

consists of a 2-stage FET amplifier and is capable of

producing up to 4W of RF power. (See Fig.7)

4) ANTswitchandLPF

The RF amplifier output signal is passed through a low-

pass filter network and a transmit/receive switching circuit

before it is passed to the antenna terminal. The transmit/

receive switching circuit is comprised of D101, D102 and

D103. D102 and D103 are turned on (conductive) in transmit

mode and off (isolated) in receive mode.

Fig. 7 APC system

AMP

Q101,Q102 DRIVE AMP

Q105

5T

B

Q103, Q104

B SW

DET

IC100

APC

5T

Q109 SW

Q106

SW

APC

5T

Q108

SW RX

D102,103

ANT SW

FINAL AMP

Q107 ANT SW

D101 LPF

ANT

5T

SW

Q110

TH102

5) APC

The automatic power control (APC) circuit stabilizes the

transmitter output power at a predetermined level by sensing

the drain current of the final amplifier Field Effect Transistor

(FET) . The voltage comparator, IC100 (2/2), compares the

voltage obtained from the above drain current with a reference

voltage which is set using the microprocessor. An APC

voltage proportional to the difference between the sensed

voltage and the reference voltage appears at the output of

IC100 (1/2). This output voltage controls the gate of the FET

power amplifier, which keeps the transmitter output power

constant. The transmitter output power can be varied by the

microprocessor which in turn changes the reference voltage

and hence, the output power.

6) Terminal protection circuit

When the thermistor (TH102) reaches about 80˚C, the

protection circuit turns on Q110 to protect transmitting final

amplifier (Q107) from the over heating.

5. Power supply

A 5V reference power supply [5M] for the control circuit is

derived from an internal battery. This reference is used to

provide a 5V supply in transmit mode [5T], a 5V supply in

receive mode [5R], and a 5V supply common in both modes

[5C] based on the control signal sent from the microprocessor.

6. Control system

The IC403 CPU operates at 7.37MHz . This oscillator has a

circuit that shifts the frequency according to the EEPROM

data.

3) UNLOCK DETECTOR

If a pulse signal appears at the LD pin of IC1, an unlock

condition occurs, and the DC voltage obtained from D7, R6,

and C1 causes the voltage applied to the UL pin of the

microprocessor to go low. When the microprocessor detects

this condition, the transmitter is disabled, ignoring the push-to-

talk switch input signal. ( See Fig.5)

Fig. 5 Unlock detector circuit

IC1

LD

PLL IC

D7

C1

R6

5C

IC403

UL

MPU