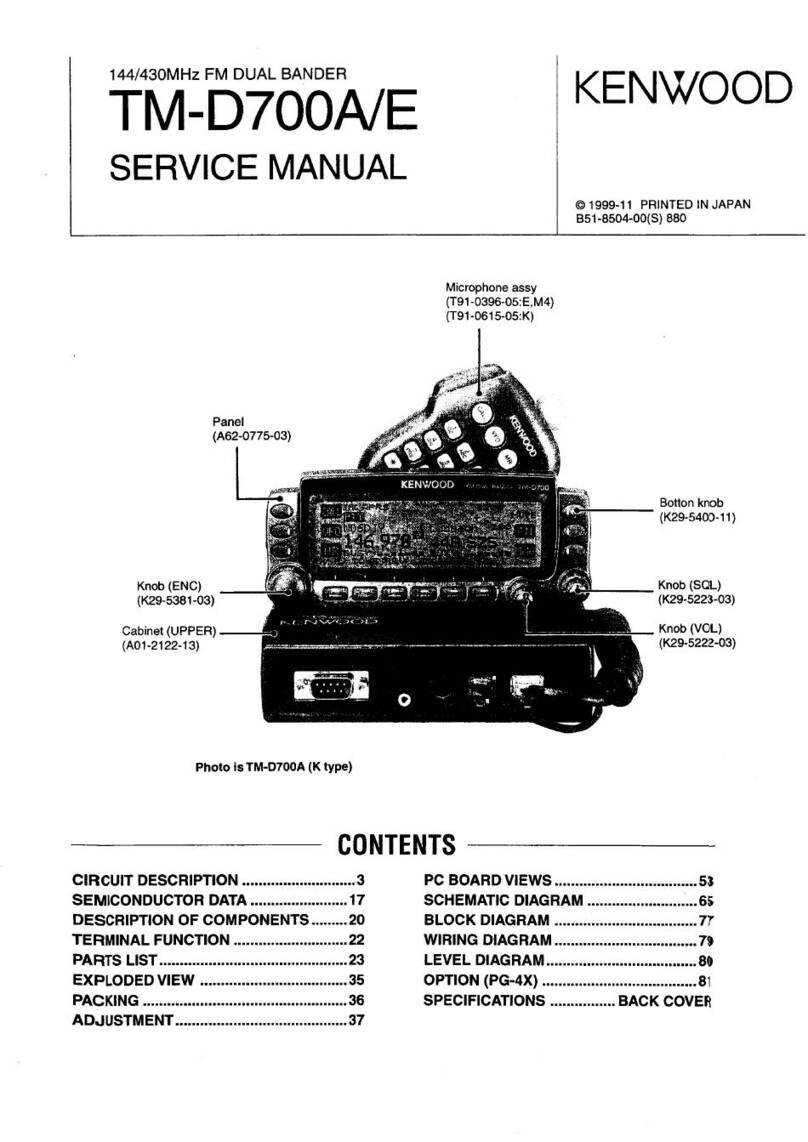

TM-321A TM-321A

CIRCUIT DESCRIPTION

Transmitter system

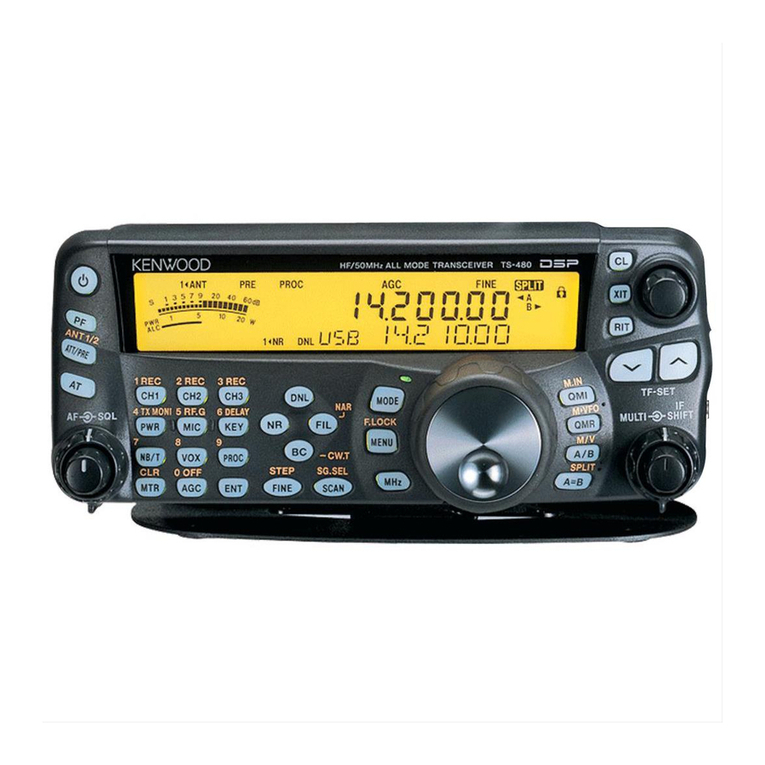

@General

In the transmitter system the desired frequency is pro-

duced directly by an oscillator. Frequency modulation is

obtained directly thru the use of avaractor diode.

@Modulation circuit

Audio signals from the microphone are applied to a

three-stage operational amplifier which adds preemphasis,

performs amplification and limiting, and includes asplatter

filter to remove undesired high-frequency components.

After amplification by the operational amplifier, part of

the audio signal is applied to the microphone check circuit

used in the low-power mode.

In the FM modulation circuit, the frequency of the

VCO is directly modulated by avaractor diode.

q

¥

RS

Ra

RM H/C

METER

Roe ae

TX-RX UNIT

TO FINAL UNIT

@Preamplifier stage circuit

The output from the VCO enters the linear amptifier,

which is capable of high-quality signal amplification

because it operates entirely in linear mode, APC, (Auto-

matic Power Control) is performed by controlling the

collector voltage of the 3stage fina! preamplifier stage.

@Power amplifier circuit

The drive signal is applied to the power module and

amplified to the required fevet. In the model TM-321A

heat is dissipated efficiently by alarge mechanically strong

heatsink,

@APC and SWR protection circuits

Fig. 3shows the basic ALC (Automatic Level Control)

and SWR (Standing Wave Ratio) protection circuits. The

SWR protection circuit incorporates aCM coupler that

detects any reflected power caused by mismatching of the

antenna. After detection and amplification, this circuit

acts to lower the output contro! voltage, which protects

the power module by reducing the gain. The automatic

power control (APC) circuit incorporates adiode that is

used to detect aportion of the output from the power

module. The detected signal is amplified and is then used

to control the power control voltage. The control voitage

is inversely proportional to the output, so aconstant

output level is maintained.

FINAL UNIT

Fig. 3APC and SWR protection circuits

Table 3Power module M57774 absolute maximum ratings

(Finat unit Q1)

CIRCUIT DESCRIPTION

PLL synthesizer

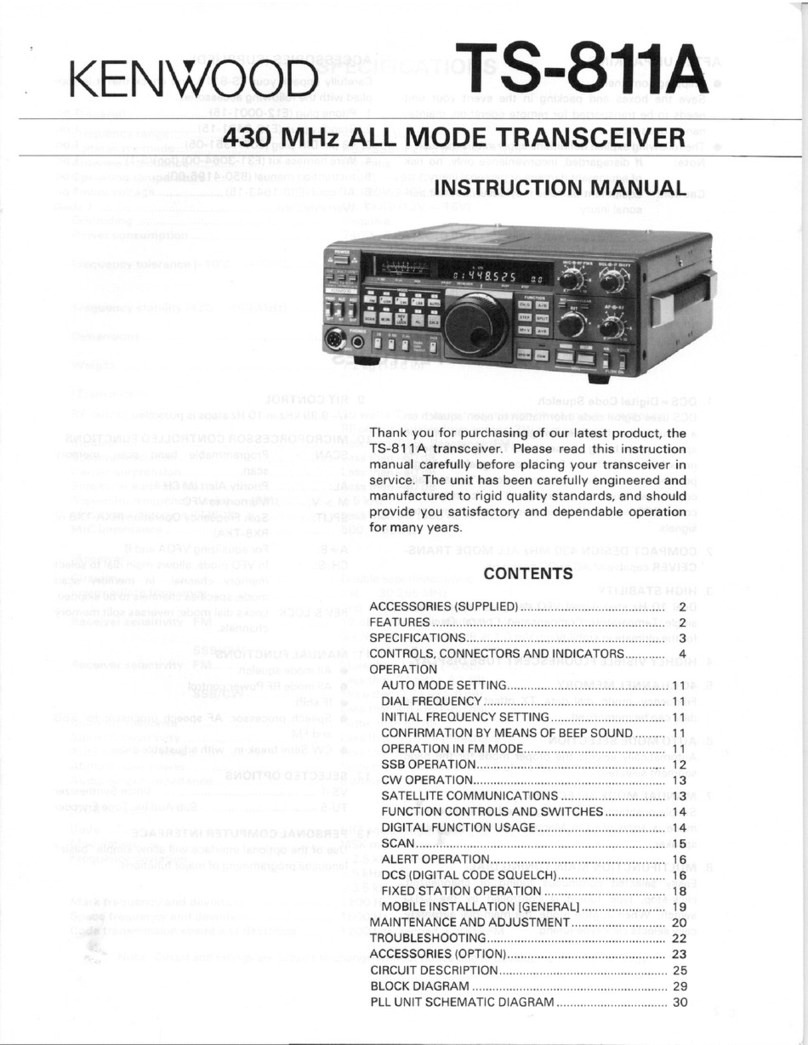

Fig. 4is the PLL system block diagram. The trans-

mitter and. receiver systems of the TM-321A has independ-

ent VCOs and PLLs, but share acommon low-pass filter.

The VCOs are configured as subunits. This construc-

tion minimizes outside influence and improves frequency

stability.

DATA

CLOCK

para

LPF

age

013,14 (c2

Meag5gP

TXVCO

FCONT

03

1SV166

To provide 5, 10, 15, 20, and 25kHz steps, acom-

parison frequency of 5kHz is obtained by dividing the 12.8

MHz frequency of the reference oscillator by 2560. In

both the transmitter and receiver systems the target

frequency is produced directly by the VCO, passed through

one amplifier stage, then applied to apulse-swallow PLL IC

that divides the frequency, performs phase comparison,

and ocks the frequency.

The reference frequency division ratios (four values)

and comparison frequency divison ratio are supplied to

the PLL IC (M54959P) as external serial data. An internal

dual-modulus (1/128 and 1/129) prescaler enables the

entire pulse-swallow PLL circuit to be implemented on

asingle chip. (See Fig. 5.) The switching functions

(SW1 and SW2) of the PLL IC are used to switch between

the 8R (receive) and 8T (transmit) operating voltages

in the transmit and receive modes.

The switch controls are applied together with frequency

division ratio data from the Control unit.

RESET

ait £13(12.8MHz)

2SC2714

2SC2714

a2

ZSK5O8

APC

OIFF. AMP RE PRO/APC CONTROL Sw AMP

RX 189,175~194.170MHz

at a2 8T fat Nout: ai7

DRIVE 28C2712 28C2757 28C2714

+8 AVR

4

(oS) TX 220, 224 Hz

RX VCO

FCONT

aa

2SK508

se

1SV166

DRIVE (X59-3120-11)

Q20 ANT

PRO

RF

APC SND (OB

TX-RX UNIT

us Ros ves 10 VCO (X58-3000-11}

TRI

Fig. 4PLL system block diagram To unlock contro! circuit

12.8MH

178 divider HH trier divider vices 12.8MHe

4Comparison fr

(72it binary}

TIN Programmable divider] fIN/N To LPF

(10-bit binary)

VCO nput 2-modulus 7fio 2

prescaler Dats latch {21-bit}

(1/128, 1/128)

21

5Shift regiver (21-bit)

NUL

Low

sk

15

kdetect

osc

by 2560 Veo

frequency phase 1

1/A divider selection detector

21 cutee counter b- Latch signal

3

aa:

Specifications

Item Symbol Unit Condition

(°c) M57774

Veo 25 17

Operating voltage

Current consumption Iec 25 7

Input power pin 25 2G6=ZL=502 0.6(Vec, $12.5V)

Output power Po 25 ZG=Z=502 40

Case temperature (operating) Telop) °c -30~+110

°c -40~ +110

Storage temperature Tstg

Tc AMP

2

13

4

Beta input

from Control unit

Fig.5 PLL IC ;M54959P block diagram

To8T TosR

control control

circuit circuit

TM-321A TM-321A

CIRCUIT DESCRIPTION

Transmitter system

@General

In the transmitter system the desired frequency is pro-

duced directly by an oscillator. Frequency modulation is

obtained directly thru the use of avaractor diode.

@Modulation circuit

Audio signals from the microphone are applied to a

three-stage operational amplifier which adds preemphasis,

performs amplification and limiting, and includes asplatter

filter to remove undesired high-frequency components.

After amplification by the operational amplifier, part of

the audio signal is applied to the microphone check circuit

used in the low-power mode.

In the FM modulation circuit, the frequency of the

VCO is directly modulated by avaractor diode.

q

¥

RS

Ra

RM H/C

METER

Roe ae

TX-RX UNIT

TO FINAL UNIT

@Preamplifier stage circuit

The output from the VCO enters the linear amptifier,

which is capable of high-quality signal amplification

because it operates entirely in linear mode, APC, (Auto-

matic Power Control) is performed by controlling the

collector voltage of the 3stage fina! preamplifier stage.

@Power amplifier circuit

The drive signal is applied to the power module and

amplified to the required fevet. In the model TM-321A

heat is dissipated efficiently by alarge mechanically strong

heatsink,

@APC and SWR protection circuits

Fig. 3shows the basic ALC (Automatic Level Control)

and SWR (Standing Wave Ratio) protection circuits. The

SWR protection circuit incorporates aCM coupler that

detects any reflected power caused by mismatching of the

antenna. After detection and amplification, this circuit

acts to lower the output contro! voltage, which protects

the power module by reducing the gain. The automatic

power control (APC) circuit incorporates adiode that is

used to detect aportion of the output from the power

module. The detected signal is amplified and is then used

to control the power control voltage. The control voitage

is inversely proportional to the output, so aconstant

output level is maintained.

FINAL UNIT

Fig. 3APC and SWR protection circuits

Table 3Power module M57774 absolute maximum ratings

(Finat unit Q1)

CIRCUIT DESCRIPTION

PLL synthesizer

Fig. 4is the PLL system block diagram. The trans-

mitter and. receiver systems of the TM-321A has independ-

ent VCOs and PLLs, but share acommon low-pass filter.

The VCOs are configured as subunits. This construc-

tion minimizes outside influence and improves frequency

stability.

DATA

CLOCK

para

LPF

age

013,14 (c2

Meag5gP

TXVCO

FCONT

03

1SV166

To provide 5, 10, 15, 20, and 25kHz steps, acom-

parison frequency of 5kHz is obtained by dividing the 12.8

MHz frequency of the reference oscillator by 2560. In

both the transmitter and receiver systems the target

frequency is produced directly by the VCO, passed through

one amplifier stage, then applied to apulse-swallow PLL IC

that divides the frequency, performs phase comparison,

and ocks the frequency.

The reference frequency division ratios (four values)

and comparison frequency divison ratio are supplied to

the PLL IC (M54959P) as external serial data. An internal

dual-modulus (1/128 and 1/129) prescaler enables the

entire pulse-swallow PLL circuit to be implemented on

asingle chip. (See Fig. 5.) The switching functions

(SW1 and SW2) of the PLL IC are used to switch between

the 8R (receive) and 8T (transmit) operating voltages

in the transmit and receive modes.

The switch controls are applied together with frequency

division ratio data from the Control unit.

RESET

ait £13(12.8MHz)

2SC2714

2SC2714

a2

ZSK5O8

APC

OIFF. AMP RE PRO/APC CONTROL Sw AMP

RX 189,175~194.170MHz

at a2 8T fat Nout: ai7

DRIVE 28C2712 28C2757 28C2714

+8 AVR

4

(oS) TX 220, 224 Hz

RX VCO

FCONT

aa

2SK508

se

1SV166

DRIVE (X59-3120-11)

Q20 ANT

PRO

RF

APC SND (OB

TX-RX UNIT

us Ros ves 10 VCO (X58-3000-11}

TRI

Fig. 4PLL system block diagram To unlock contro! circuit

12.8MH

178 divider HH trier divider vices 12.8MHe

4Comparison fr

(72it binary}

TIN Programmable divider] fIN/N To LPF

(10-bit binary)

VCO nput 2-modulus 7fio 2

prescaler Dats latch {21-bit}

(1/128, 1/128)

21

5Shift regiver (21-bit)

NUL

Low

sk

15

kdetect

osc

by 2560 Veo

frequency phase 1

1/A divider selection detector

21 cutee counter b- Latch signal

3

aa:

Specifications

Item Symbol Unit Condition

(°c) M57774

Veo 25 17

Operating voltage

Current consumption Iec 25 7

Input power pin 25 2G6=ZL=502 0.6(Vec, $12.5V)

Output power Po 25 ZG=Z=502 40

Case temperature (operating) Telop) °c -30~+110

°c -40~ +110

Storage temperature Tstg

Tc AMP

2

13

4

Beta input

from Control unit

Fig.5 PLL IC ;M54959P block diagram

To8T TosR

control control

circuit circuit