CrossLink-NX PCIe Bridge Board Basic Demo

User Guide

© 2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

4 FPGA-UG-02145-1.0

Figures

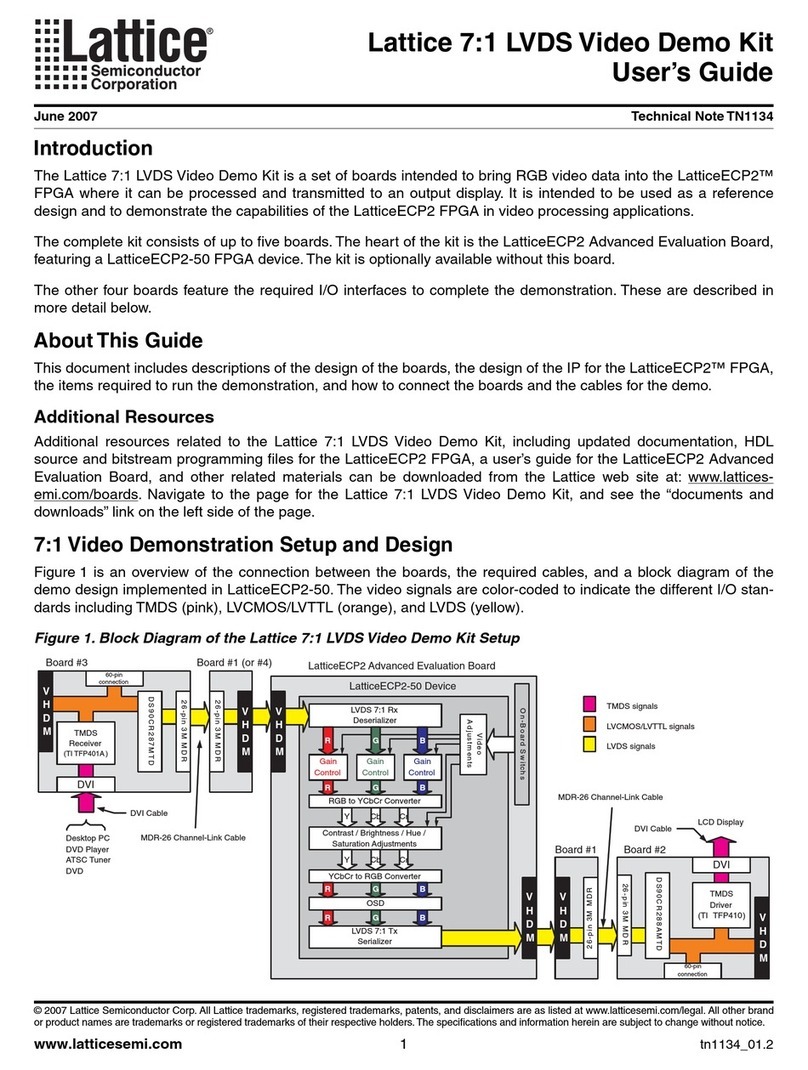

Figure 3.1. CrossLink-NX PCIe Bridge Board Jumper Location..............................................................................................9

Figure 3.2. CrossLink-NX PCIe Bridge Board Connection....................................................................................................10

Figure 3.3. Creating a New Project from a Scan .................................................................................................................10

Figure 3.4. Radiant Programmer Window ..........................................................................................................................11

Figure 3.5. FPGA Device Settings ........................................................................................................................................11

Figure 3.6. Device Properties Window for SPI Flash Programming ....................................................................................12

Figure 3.7. Programmer Menu Bar.....................................................................................................................................12

Figure 3.8. Programmer Output Window...........................................................................................................................12

Figure 3.9. Status LED .........................................................................................................................................................13

Figure 3.10. Running Disable Integrity Checks Command..................................................................................................14

Figure 3.11. Running Test Sign On Command.....................................................................................................................14

Figure 3.12. Troubleshoot Option.......................................................................................................................................15

Figure 3.13. Advanced Options...........................................................................................................................................15

Figure 3.14. Select Startup Settings....................................................................................................................................16

Figure 3.15. Restarting Windows........................................................................................................................................16

Figure 3.16. Device Manager..............................................................................................................................................17

Figure 3.17. Showing Device Properties .............................................................................................................................17

Figure 3.18. Hardware IDs of Basic Demo Device...............................................................................................................18

Figure 3.19. Update Driver Menu in Device Manager........................................................................................................19

Figure 3.20. Update Driver Options....................................................................................................................................19

Figure 3.21. Browse the Driver for Device..........................................................................................................................20

Figure 3.22. Windows Security in Device Manager ............................................................................................................20

Figure 3.23. Driver Installation Status Message .................................................................................................................21

Figure 3.24. Basic Demo Device Name Displayed in Device Manager................................................................................21

Figure 3.25. Preparing to Install Page.................................................................................................................................22

Figure 3.26. Welcome Page ................................................................................................................................................22

Figure 3.27. Destination Folder Page..................................................................................................................................23

Figure 3.28. Summary Page ................................................................................................................................................23

Figure 3.29. Application Installed .......................................................................................................................................24

Figure 3.30. Device Configuration Prompt .........................................................................................................................24

Figure 3.31. Device Driver Installation Wizard ...................................................................................................................25

Figure 3.32. Windows Security in Driver Installation..........................................................................................................25

Figure 3.33. Device Driver Installation Completed .............................................................................................................26

Figure 4.1. Relationship of the Hardware and Software Components...............................................................................30

Figure 4.2. PCIe Basic Demo SW Design .............................................................................................................................31

Figure 4.3. PCIe Basic Demo FPGA Design ..........................................................................................................................31

Figure 5.1. PCIe Test Application Device Info Tab ..............................................................................................................33

Figure 5.2. PCIe Test Application Config Space Tab............................................................................................................34

Figure 5.3. Three 7-Segment Display on Board ..................................................................................................................35

Figure 5.4. Interactive 7 Segment Display Tab ...................................................................................................................35

Figure 5.5. PCIe Test Application Memory Tab...................................................................................................................37

Figure 7.1. TCK Frequency Setting......................................................................................................................................40

Figure 7.2. Port Selection....................................................................................................................................................40

Figure 7.3. User Interface with No Device Driver ...............................................................................................................41

Figure 7.4. Error Message...................................................................................................................................................42

Figure 7.5. lspci -vnm Output Image...................................................................................................................................42

Figure 7.6. Content List of Demonstration/Linux Directory. ..............................................................................................43

Figure 7.7. Content List of Software/Linux Directory .........................................................................................................43