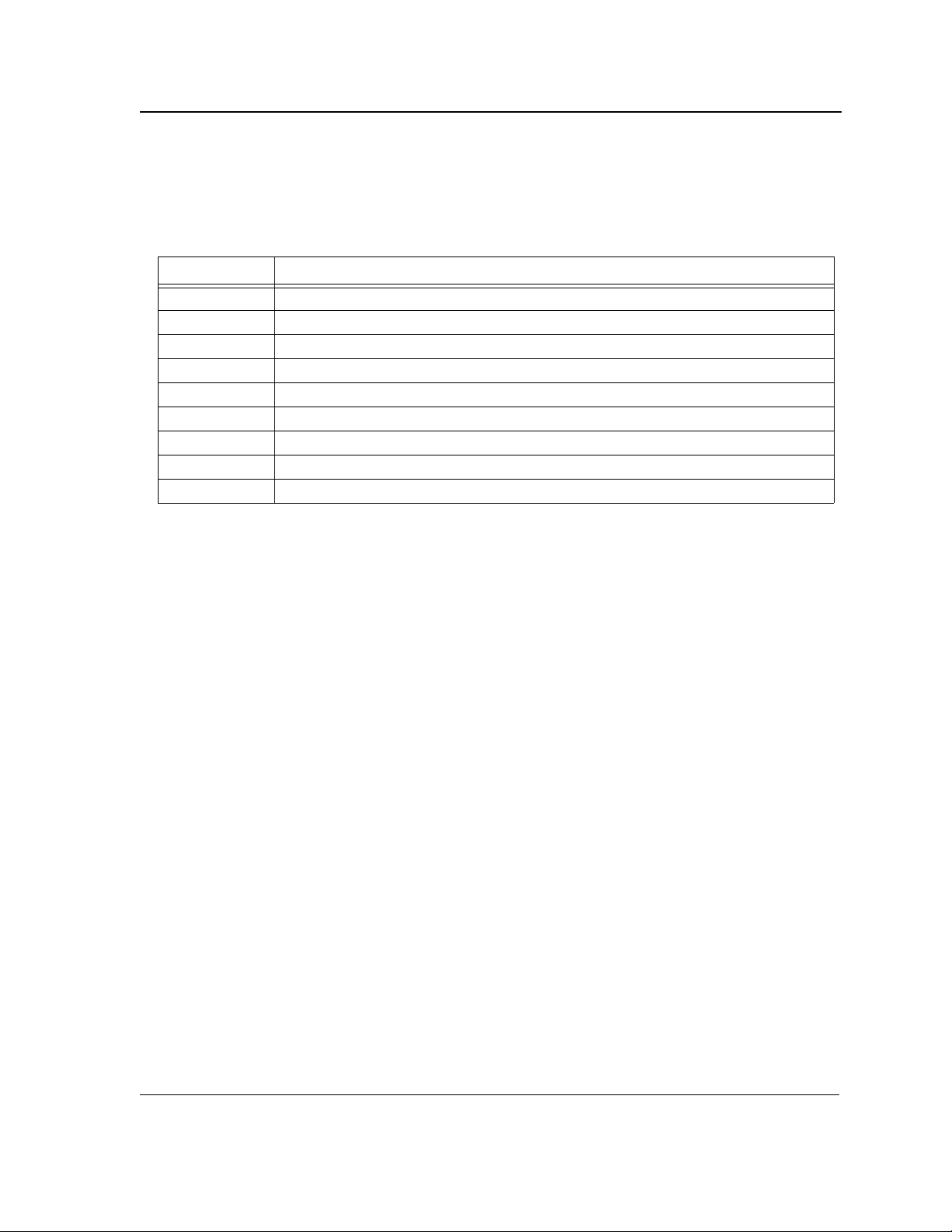

Document Status

Advance

Information

This document contains design specifications for initial product development. Specifications may

change without notice. Contact Marvell Field Application Engineers for more information.

Preliminary

Information

This document contains preliminary data, and a revision of this document will be published at a later

date. Specifications may change without notice. Contact Marvell Field Application Engineers for

more information.

Final

Information

This document contains specifications on a product that is in final release. Specifications may

change without notice. Contact Marvell Field Application Engineers for more information.

Revision Code: Rev. A

Advance Technical Publication: 1.10

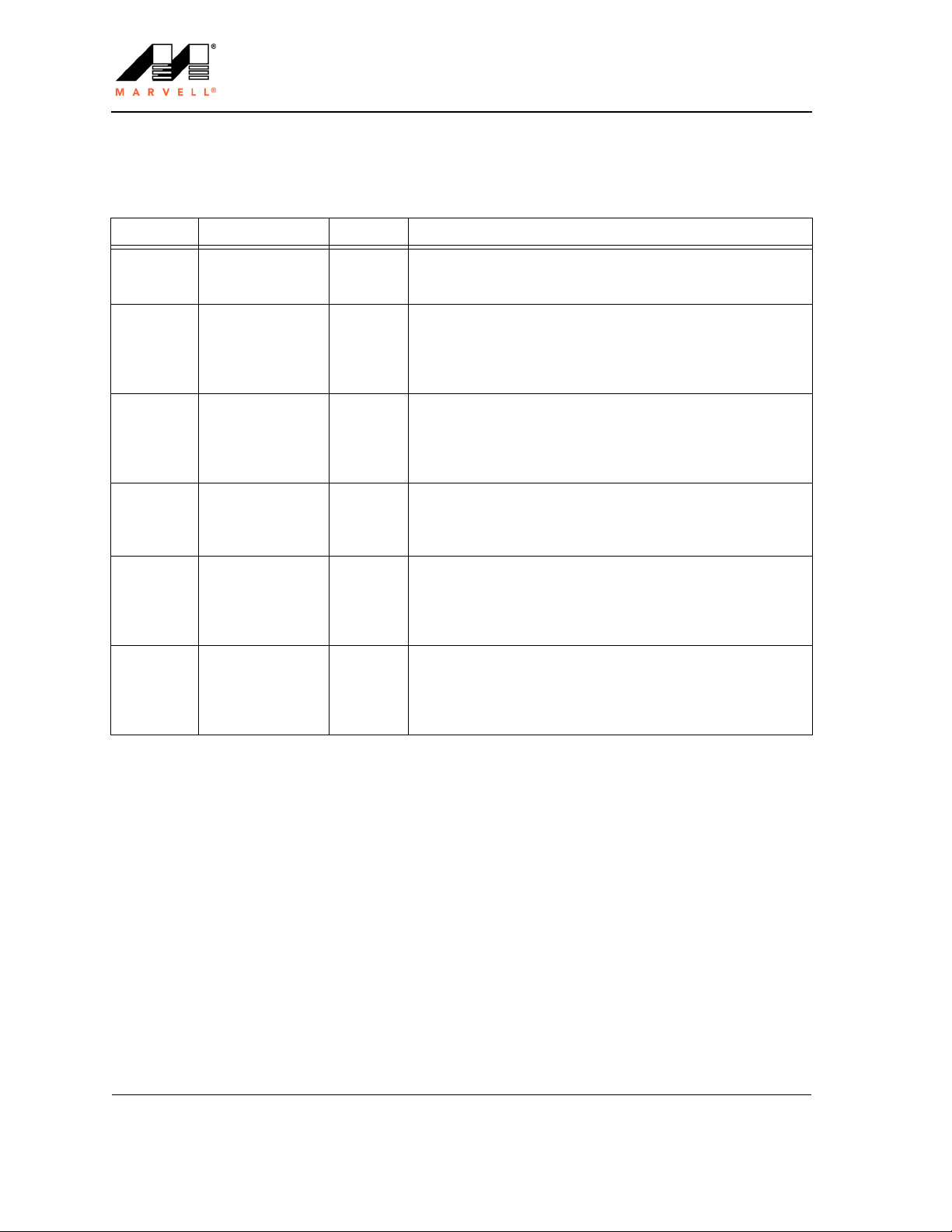

Document Conventions

Note: Provides related information or information of special importance.

Caution: Indicates potential damage to hardware or software, or loss of data.

Warning: Indicates a risk of personal injury.

For more information, visit our website at: www.marvell.com

Disclaimer

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose,

without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any

kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any

particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document.

Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use

Marvell products in these types of equipment or applications.

With respect to the products described herein, the user or recipient, in the absence of appropriate U.S. government authorization, agrees:

1) Not to re-export or release any such information consisting of technology, software or source code controlled for national security reasons by the U.S. Export Control

Regulations ("EAR"), to a national of EAR Country Groups D:1 or E:2;

2) Not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof are

controlled for national security reasons by the EAR; and,

3) In the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a plant,

not to export to EAR Country Groups D:1 or E:2 the direct product of the plant or major component thereof, if such direct product is controlled for national security reasons

by the EAR, or is subject to controls under the U.S. Munitions List ("USML").

At all times hereunder, the recipient of any such information agrees that they shall be deemed to have manually signed this document in connection with their receipt of any

such information.

Copyright © 2008. Marvell International Ltd. All rights reserved. Marvell, the Marvell logo, Moving Forward Faster, Alaska, Fastwriter, Datacom Systems on Silicon, Libertas,

Link Street, NetGX, PHYAdvantage, Prestera, Raising The Technology Bar, The Technology Within, Virtual Cable Tester, and Yukon are registered trademarks of Marvell.

Ants, AnyVoltage, Discovery, DSP Switcher, Feroceon, GalNet, GalTis, Horizon, Marvell Makes It All Possible, RADLAN, UniMAC, and VCT are trademarks of Marvell. All

other trademarks are the property of their respective owners.

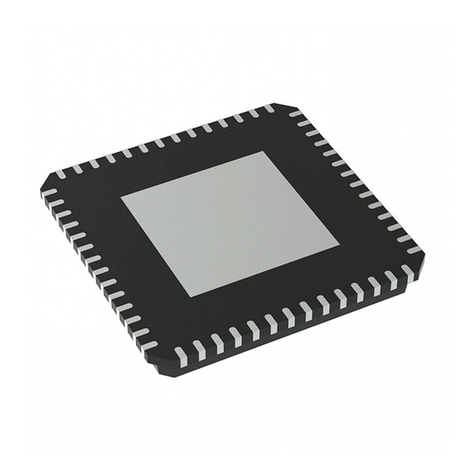

88E3016

Integrated 10/100 Fast Ethernet Transceiver

Doc. No. MV-S103164-00 Rev. A Copyright © 2008 Marvell

Page 2 Document Classification: Proprietary Information January 4, 2008, Advance