3

M722 N/B MAINTENANCE

M722 N/B MAINTENANCE

Table of Contents

0.1. INTRODUCTION…………............................................................................................................................................................................…..6

0.2. SYSTEM HARDWARE PARTS ..........................................................................................................................................................................7

0.2.1 CPU – INTEL MOBILE CELERON/PENTIUM III PROCESSOR IN UPGA2 PACKAGE................................................................................7

0.2.2 INTEL 82440MX-100 CHIPSET HOST BRIDGE ..................................................................................................................................................8

0.2.3 SYSTEM FREQUENCY SYNTHESIZER AND SDRAM BUFFER :ICS9148-101.....................................................................................................11

0.2.4 VGA CONTROLLER: ATI 3D RAGE MOBILITY-M INTEGRATED 4MB SDRAM ..........................................................................................13

0.2.5 PC CARD INTERFACE CONTROLLER: TI1410..................................................................................................................................................16

0.2.6 SINGLE-SLOT PC CARD POWER INTERFACE SWITCH: TPS2211.....................................................................................................................16

0.2.7 AC’97 AUDIO SYSTEM: CRYSTAL CS 4299............................................................................................................................................17

0.2.8 MDC: PCTEL MODEM DAUGHTER CARD...............................................................................................................................................19

0.2.9 SUPER IO: NS PC 97338VJG.........................................................................................................................................................................19

0.2.10 IR MODULE: VISHAY TFDU6101E..........................................................................................................................................................20

0.2.11 KEYBOARD SYSTEM: H8(3434) UNIVERSAL KEYBOARD CONTROLLER.........................................................................................................20

0.2.12 SYSTEM FLASH MEMORY (BIOS)...................................................................................................................................................................22

0.2.13 MEMORY SYSTEM...........................................................................................................................................................................................22

0.2.13.1 On Board Main Memory........................................................................................................................................................................22

0.2.13.2 JEDEC 144-pin SO DIMM sockets........................................................................................................................................................22

0.2.14 LAN : REALTEK RTL8139CL ........................................................................................................................................................................23

0.2-15 IEEE 1394 : NEC UPD72870A....................................................................................................................................................................25

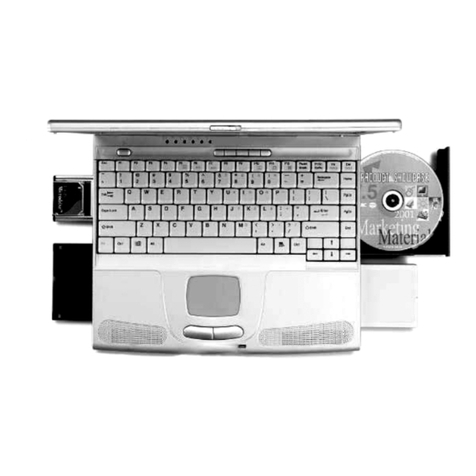

0.3. I/O PORT..............................................................................................................................................................................................................27

0.4. PERIPHERAL COMPONENTS ........................................................................................................................................................................27

0.4.1 LCD PANEL..................................................................................................................................................................................................27

0.4.2 FLOPPY DISK DRIVE(USB) .............................................................................................................................................................................27

0.4.3 HDD...............................................................................................................................................................................................................27

0.4.4 24X CD-ROM DRIVE.....................................................................................................................................................................................28

0.4.5 8X DVD-ROM DRIVE ....................................................................................................................................................................................28

0.4.6 KEYBOARD .....................................................................................................................................................................................................28

0.4.7 TOUCH PAD.....................................................................................................................................................................................................28

0.4.8 FAN.................................................................................................................................................................................................................28

0.5. APPENDIX 1: BANISTER GPIO DEFINITIONS ...........................................................................................................................................29