NM500 Manual 3

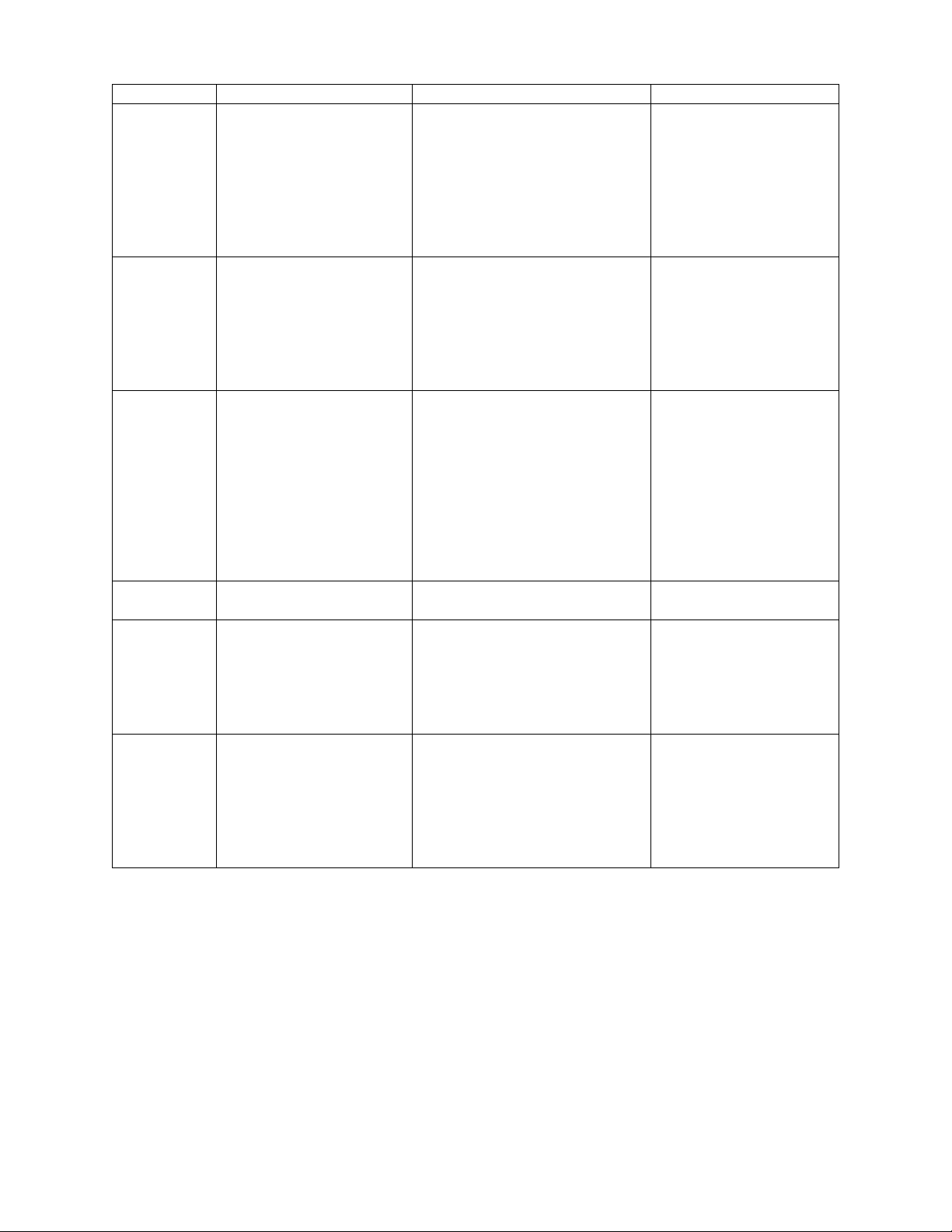

CONTENTS

1Overview................................................................................................................................................................4

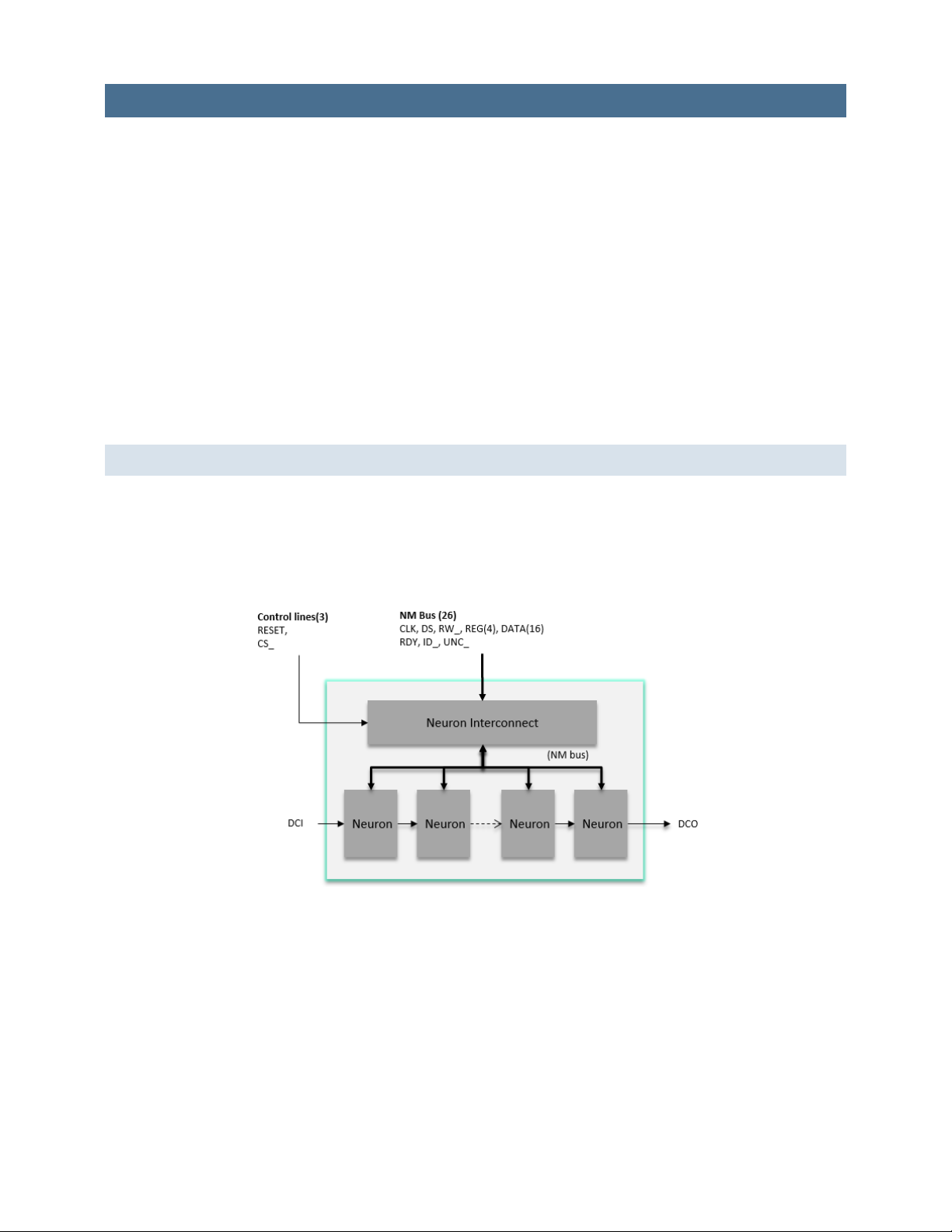

1.1 Architecture .................................................................................................................................................4

1.2 The basic neuron entity................................................................................................................................5

2The control registers..............................................................................................................................................6

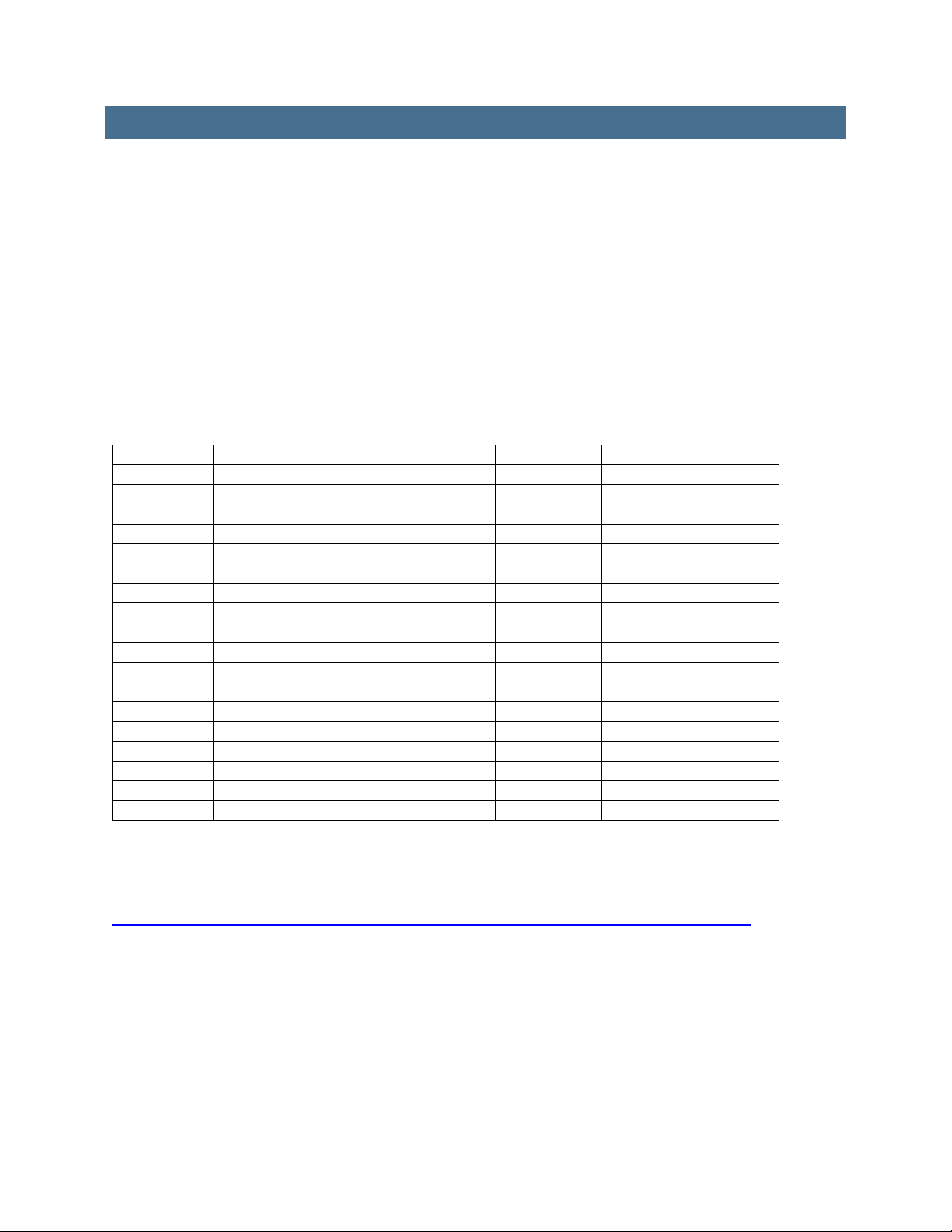

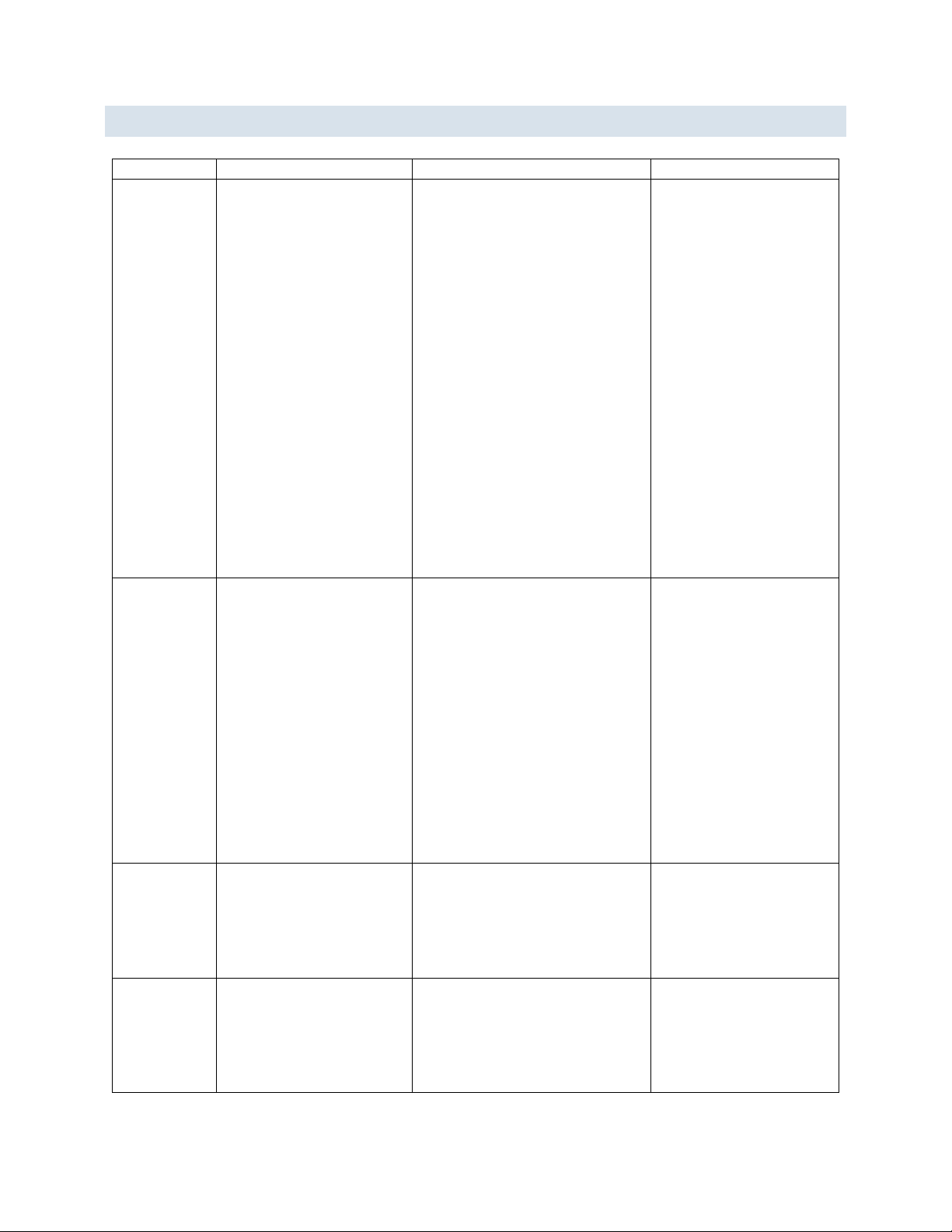

2.1 Neuron registers in detail.............................................................................................................................7

2.2 Registers Access Latency............................................................................................................................11

2.3 Typical latencies per operation ..................................................................................................................12

3NeuroMem bus and control lines........................................................................................................................13

3.1 Clocks, power-up and reset........................................................................................................................14

3.1.1 G_Reset, global reset .............................................................................................................................14

3.1.2 G_CLK, system clock ..............................................................................................................................14

3.1.3 CS_, power saving control line...............................................................................................................14

3.1.4 DCI..........................................................................................................................................................14

3.1.5 DCO ........................................................................................................................................................14

3.2 NeuroMem bus ..........................................................................................................................................15

3.2.1 DS...........................................................................................................................................................15

3.2.2 RW_ .......................................................................................................................................................15

3.2.3 REG[3:0] .................................................................................................................................................15

3.2.4 DATA[15:0].............................................................................................................................................16

3.2.5 RDY.........................................................................................................................................................16

3.2.6 ID_..........................................................................................................................................................16

3.2.7 UNC_ ......................................................................................................................................................16

4Typical Timings Constraints .................................................................................................................................17

4.1 Timings .......................................................................................................................................................17

4.2 Learn a vector.............................................................................................................................................18

4.3 Recognize a vector .....................................................................................................................................19

5Interconnecting chips ..........................................................................................................................................20

5.1 Counting the neurons in a chain of unknown length.................................................................................20

5.2 Verifying the proper interconnectivity of the entire chain ........................................................................20

5.3 If a chain has more than 65535 neurons....................................................................................................21

5.4 Single or multiple chains of neurons..........................................................................................................21

6Pinout ..................................................................................................................................................................22

7Mechanical specifications....................................................................................................................................25

8Electrical Specifications .......................................................................................................................................26

8.1 Recommended Operating Conditions........................................................................................................26

8.2 DC Electrical Charateristics.........................................................................................................................26

9Power Consumption ............................................................................................................................................27

9.1 Peak Power.................................................................................................................................................27

9.2 Intrinsic Power ...........................................................................................................................................27

9.3 UPower saving tips ......................................................................................................................................27

10 FAQ ......................................................................................................................................................................28

10.1 Hardware questions ...................................................................................................................................28

10.2 Functional questions ..................................................................................................................................28

10.3 What is the difference between CM1K and NM500 ..................................................................................29