AN11001 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 1 — 7 March 2011 7 of 17

NXP Semiconductors AN11001

CBTL02042A switching application for mSATA, PCIe Mini-Card

4. Mini-Card/mSATA routing guidelines (summary)

High-speed signals on Mini-Card and mSATA devices are listed in Table 3. PCB design

must follow general guidelines of these high-speed signals as suggested by the chip set

manufacturer. This section briefly discusses these guidelines.

4.1 PCI Express routing guideline (without multiplexer in topology)

The Mini-Card topology supports up to four vias for each transmit or receive differential

signal, with maximum of 10 inches (25.4 cm) of trace length from chip set pin to the

Mini-Card connector. Maximum trace length includes all routing sections, including

breakout region from the chip set, main route, and breakout region to the connector.

Length mismatch within the differential pair should not exceed 5 mils. If signals can be

routed without switching to a different layer, less vias will be used, and impedance change

of the differential pairs can be avoided as well.

Figure 4 illustrates the required routing for PCI Express differential signals from chip set to

a Mini-Card connector. The PCIe interface is an x1 link and can be routed to different

devices at varied locations of the board, it is practical to route TX signals and RX signals

of each link next to each other on the same PCB layer.

•Total trace length from chip set pin to Mini-Card connector should not exceed

10 inches (25.4 cm). If at all possible, it is recommended to route the signals on the

top layer with no vias.

•Maximum main route length should not exceed 8 inches (20.32 cm), and should

include maximum of one via in the main route region for each signal. Route the main

route signals on the PCB top layer if possible so that the trace can be connected to

AC coupling capacitors (also located on the top layer) directly.

•Trace length in the breakout area near chip set side and connector side should be

limited to be less than 0.5 inch (1.27 cm). Similar to main route, maximum of one via

in each breakout region is allowed.

•AC coupling capacitors with values of between 75 nF and 200 nF for the transmit

signals should be located near the connector side. RX signals on the motherboard

sides do not require AC coupling capacitors since those capacitors are located on the

device side.

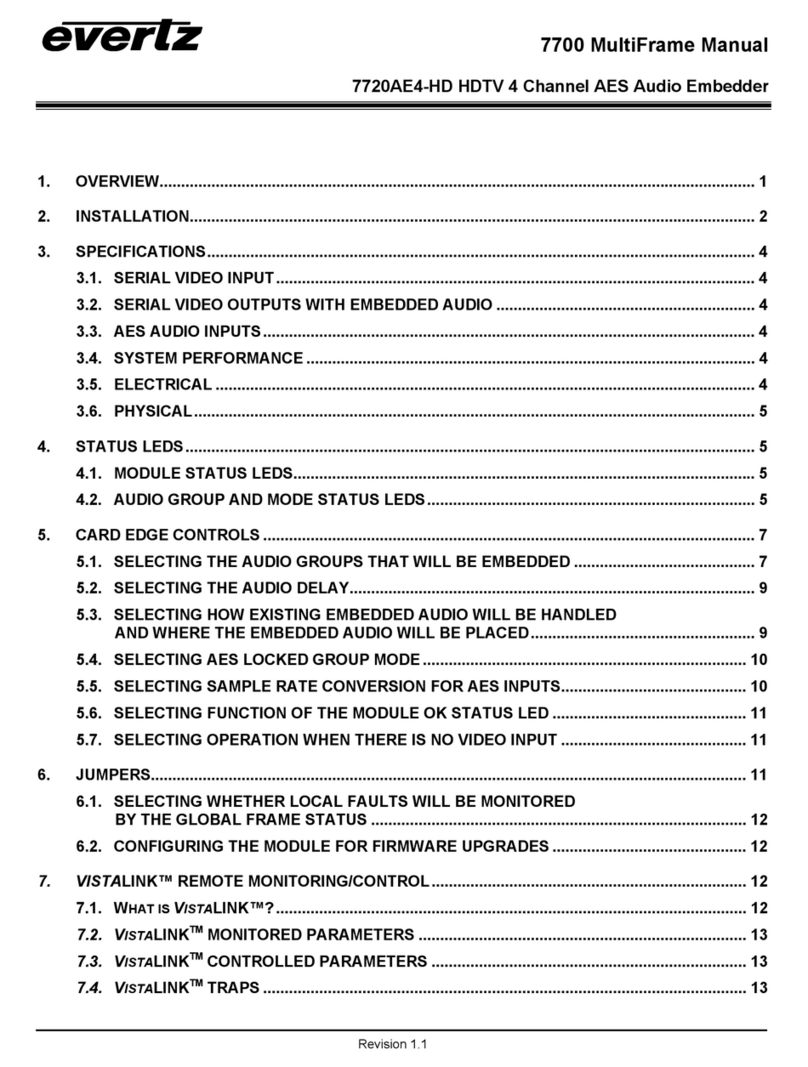

Table 3. Mini-Card/mSATA high speed signals

Card type Signal name Description

Mini-Card PETp0, PETn0 PCI Express Tx differential pair

PERp0, PERn0 PCI Express Rx differential pair

mSATA +A, A SATA Tx differential pair

+B, B SATA Rx differential pair