3

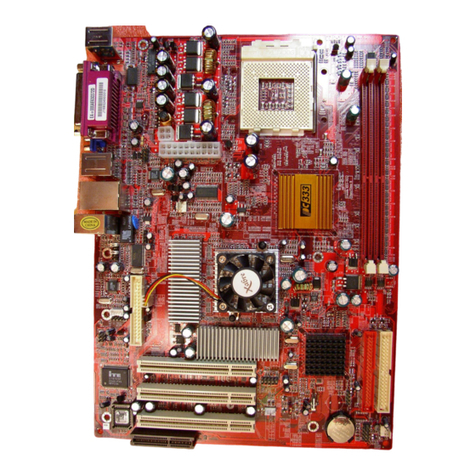

Power

Supply and

Power

Management

•ATX power supply connector

•Meets ACPI 1.0b and APM 1.2 requirements, keyboard

power on/off

•Supports RTC Alarm, Wake On Modem, AC97 Wake-Up

and USB Wake-Up

AC’97 Audio

Codec •Compliant with AC’97 2.2 specification

•Full-duplex Codec with independent and variable sam-

pling rate

•Earphone Buffer Built-In, SNR up to 90db

•4Ch DAC, support 4-channel speak-out

•Advanced power management support

Onboard VGA •Supports AGP V2.0 Compliant

•Supports AGP 4X/2X*interface and Fast Write Transac-

tion

•Supports high performance & high quality 3D Accelera-

tor—A built-in 256-bit 3D engine, up to 143 MHz 3D

engine clock speed

•Supports high performance 128-bit 2D Accelerator—

Ultra-AGPIITM

2GB/s data read for all 2D engine functions

•Maximum Share Memory size is 64MB

Built-in Ethernet

LAN (optional) •Built-in 10BaseT/100BaseTX Ethernet LAN

•SiS961 Embedded Fast Ethernet MAC and onboard

Realtek RTL8201 LAN PHY compliant with IEEE802.3u

100BASE-TX, 10BASE-T and ANSI X3.263 TP-PMD

standards

•Compliant with ACPI 1.0 and the Network Device Class

Power Management 1.0

•High Performance provided by 100Mbps clock generator

and data recovery circuit for 100Mbps receiver

USB 2.0 (see note)

The USB 2.0 Controller is compliant with Universal Serial Bus

Specification Revision 2.0.

The USB 2.0 supports data transfer rates up to 480MB/sec for

high-speed devices and specifies a microframe that will be

1/8th of a 1msec frame. This allows the USB 2.0 devices to

have small buffers even at high data rates.

The USB 1.1 connectors and other full speed cables can sup-

port the higher speed of USB 2.0 without any changes.

The chipset has the following advanced USB features:

•Compliant with Enhanced Host Controller Interface

(EHCI) Specification Revision 0.95 and Universal Host

Controller Interface (UHCI) Specification Revision 1.1

•PCI multi-function device consists of two UHCI Host Control-

lers for full/low-speed signaling and one EHCI Host

Controller core for high-speed signaling

•Supports PCI-Bus Power Management Interface Specifi-

cation release 1.1

•Legacy support for all downstream facing ports

Note: This feature is only present when SiS962

Southbridge chipset is onboard.

*Except when the mainboard incorporates the SiS650GL Northbridge chipset.