Page 8 RF Technology T50

2.6 Direct Audio (TONE) Select 2 TRANSMITTER INTERNAL JUMPER OPTIONS

applied to the pair through 660 ohms of source impedance. (It would be expected,

normally, that if this option is selected, then the option to remove the 600 terminator

from Line1, would also be selected). If dc current flows from having applied this

potential, then the transmitter will key up.

2.6 Direct Audio (TONE) Select

Normally any signal applied to the TONE+/TONE- pair is ignored. If this option is

selected then a Direct Audio input will be mixed with any audio received on either of

the other two lines.

2.7 Direct Audio (TONE) High Pass Filter Select

Normally the Direct Audio, and the CTCSS outputs are passed through a 250Hz, low

pass filter. This filter can be bypassed by selecting this option.

2.8 Transmit Time

This parameter defines a maximum time limit for continuous transmission. It is

expressed in seconds and can be arbitrarily large (months in fact). If it is set to zero

seconds, then the transmitter can stay keyed up permanently.

2.9 Channel Selectable Parameters

Each channel defines two complete set of parameters. One set of parameters is used

when a transmitter keys up from the PTT-in input, and the other set is used when the

transmitter keys up from the LOOP-in, the PTT switch, or the microphone PTT input.

Each set defines what frequency to use, what CTCSS sub-tone (if any) to use, what

maximum line deviation to use, what tone deviation to use, what transmit delay (a delay

applied from PTT-in or LOOP-in to transmission), what transmit tail (delay from PTT-

in, or LOOP-in, to transmission being stopped, and No-TONE period (a period of extra

transmission in which No Tone is applied after PTT-in or LOOP-in has been released.

As well as these parameters, which Line (or Lines) can be selected, and whether the

Lines should have Flat frequency response or have Pre-emphasis applied. Also, it can

Enable or disable the extra 20dB gain pad.

Note that both Line1 and Line 2 can be selected (each with or without pre-emphasis),

and if so, then the two signals will be mixed, and the Line potentiometer will adjust the

level of them both.

3 Transmitter I/O Connections

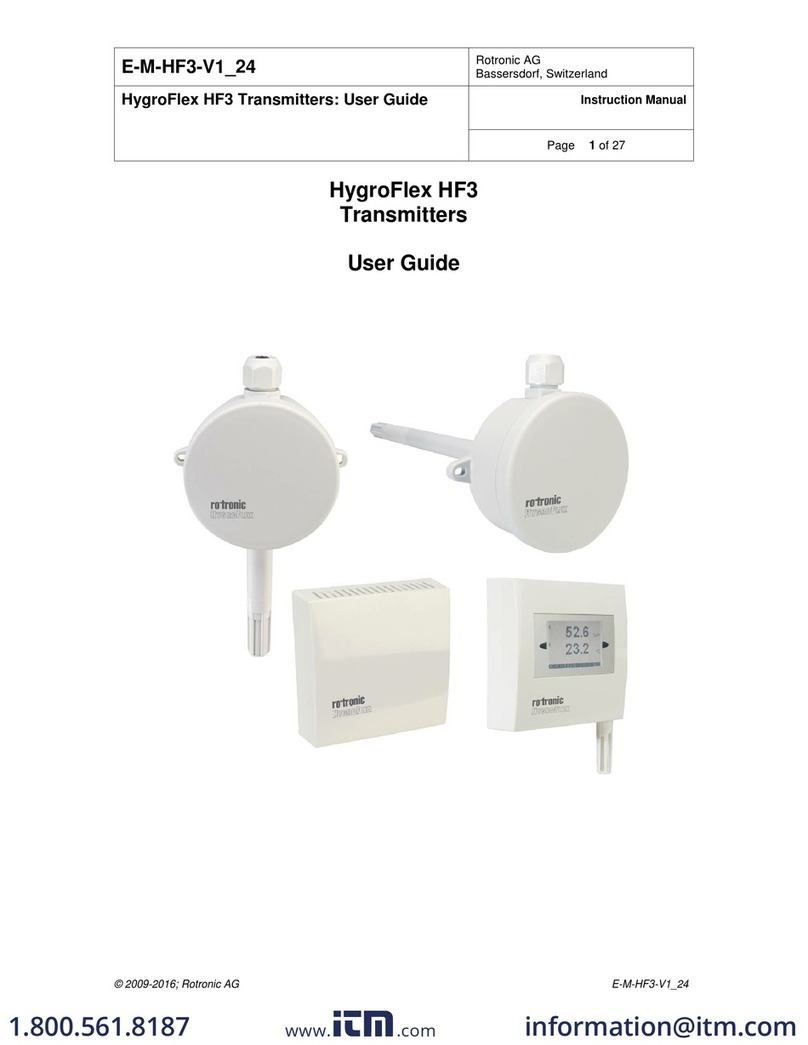

3.1 25 Pin Connector

The female D-shell, 25 pin, connector is the main interface to the transmitter. The pin

connections are described in table 3.