SAMSUNG Proprietary-Contents may change without notice

CircuitDescription

2-5

ThisDocumentcan notbe used withoutSamsung'sauthorization

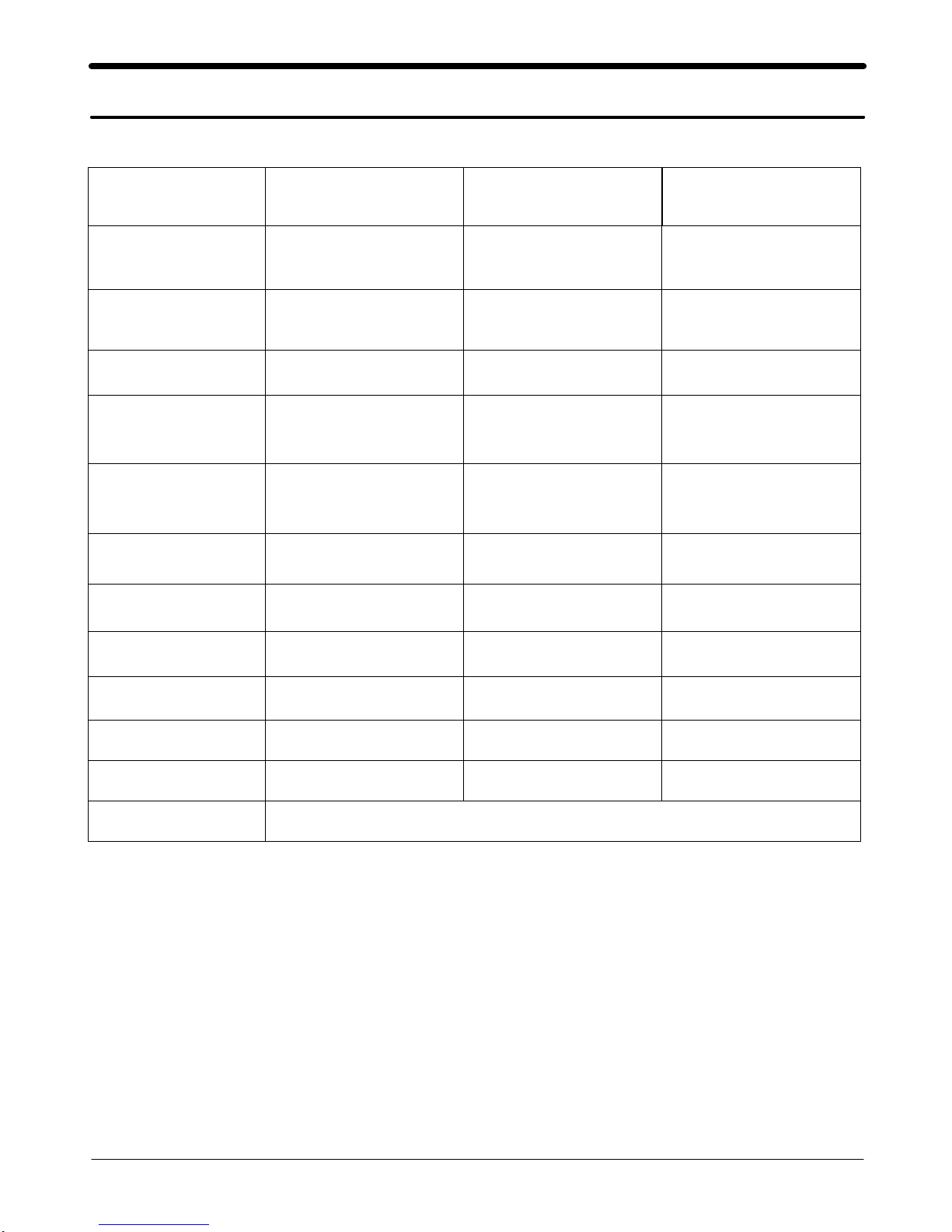

2-2-5.Memory

This systemusesSHARP'smemory,LRS18B0.

It isconsisted of256Mbitsflashmemoryand 64MbitsSCRAM.Ithas16 bit dataline,D[0~15]whichisconnectedto

trident,LCDorCSP2200.Ithas23 bit address lines,A[1~23].Theyare alsoconnected.CP_CSROMENsignal,chip

selectsignal inthetrident,enableflashmemories.They usesupply voltages,VCCDand VCC_1.8A.

During wrting process,CP_WENislowand it enableswriting process toflashmemoryand SCRAM.During reading

process,CP_OENislowand it output information whichislocatedat the address fromthetrident intheflashmemory or

SCRAMto datalines.Eachchipselectsignalsinthetridentselectflashmemory orSCRAM.Reading orwriting

procedureisprocessedafterCP_WENorCP_OENisenabled.MemoriesuseFLASH_RESET,whichisbufferedsignalof

RESET fromCSP2200,forESDprotection.A[0]signalenableslowerbyteofSCRAMand UPPER_BYTE signalenables

higherbyteofSCRAM.

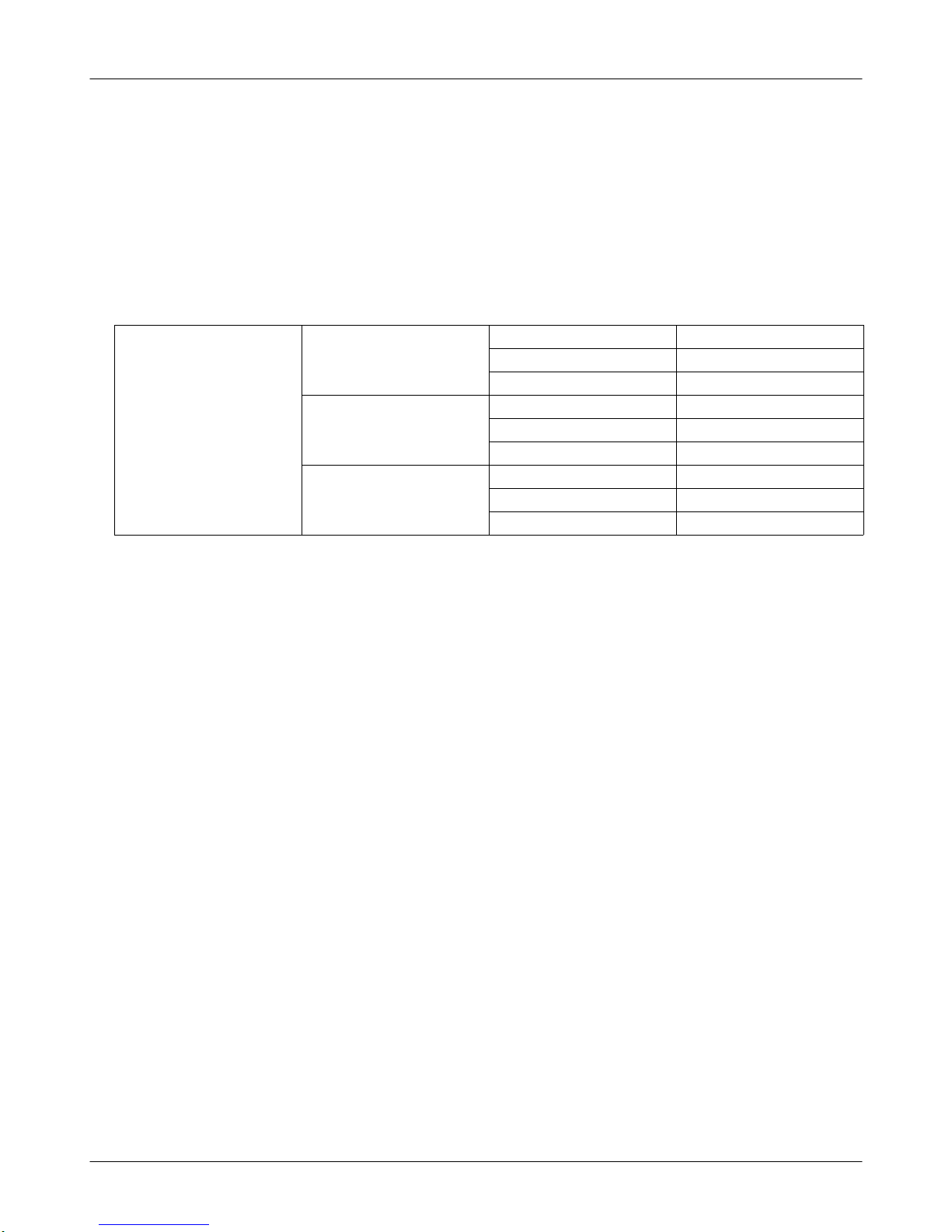

2-2-6.Trident

Trident isconsisted ofARMcore and DSP core.Ithas20K*16bitsRAM144K*16bitsROMintheDSP.Ithas

4K*32bitsROMand 2K*32bitsRAMintheARMcore.DSP isconsisted oftimer,onebit input/outputunit(BIO),JTAG,

EMIand HDS(HardwareDevelopmentSystem).ARMcoreisconsisted ofEMI,PIC(ProgrammableInterruptController),

reset/power/clock unit,DMAcontroller,TIC(TestInterface Controller),peripheralbridge,PPI,SSI(SynchronousSerial

Interface),ACCs(Asynchronouscommunicationscontrollers),timer,ADC,RTC(Real-TimeClock)and keyboardinterface.

DSP_AB[0~8],address linesofDSP core and DSP_DB[0~15],datalinesofDSP core are connectedtoCSP2200.A[0~20],

address linesofARMcore and D[0~15],datalinesofARMcore are connectedtomemory,LCDand YMU762.

ICP(InterprocessorCommunication Port)controlsthe communication betweenARMcore and DSP core.

CSROMEN,CSRAMENand CS1NtoCS4NintheARMcore are connectedtoeachmemory.WENand OENcontrol the

process ofmemory.ExternalIRQ(InterruptReQuest)signalsfromeach units,suchas,YMU,Ear-jack,Ear-mic and

CSP1093,needthe compatibleprocess.

SomePPIpinshasmany specialfunctions.CP_KB[0~9] receivethestatusfromkeyFPCB and areusedforthe

communicationsusing datalink cable(DEBUG_DTR/RTS/TXD/RXD/CTS/DSR).

And UP_CS/SCLK/SDI,controlsignalsforCSP2200 areoutputtedthrough PPIpins.Ithas signalportfor

charging(CHG_DET),SIM_RESET and FLIP_SNSwithwhichweknowsopen.closedstatusof folder.Ithas JTAG control

pins(TDI/TDO/TCK) forARMcore and DSP core.Itrecieves13MHz clockinCKIpinfromexternalTCXO and receives

32.768KHz clockfromX1RTC.ADC(Analog toDigitalConvertor) partreceivesthestatusoftemperature,batterytype and

battery voltage.And controlsignals(DSP_INT,DSP_IOand DSP_RWN) forDSP core areused.ItenablesmainLCD with

DSP IPpins.