Table of Contents

PRODUCT DESCRIPTION_________________________________________________1

KEY FEATURES _________________________________________________________1

ADDRESS MAP _________________________________________________________2

I/O CONNECTIONS_______________________________________________________2

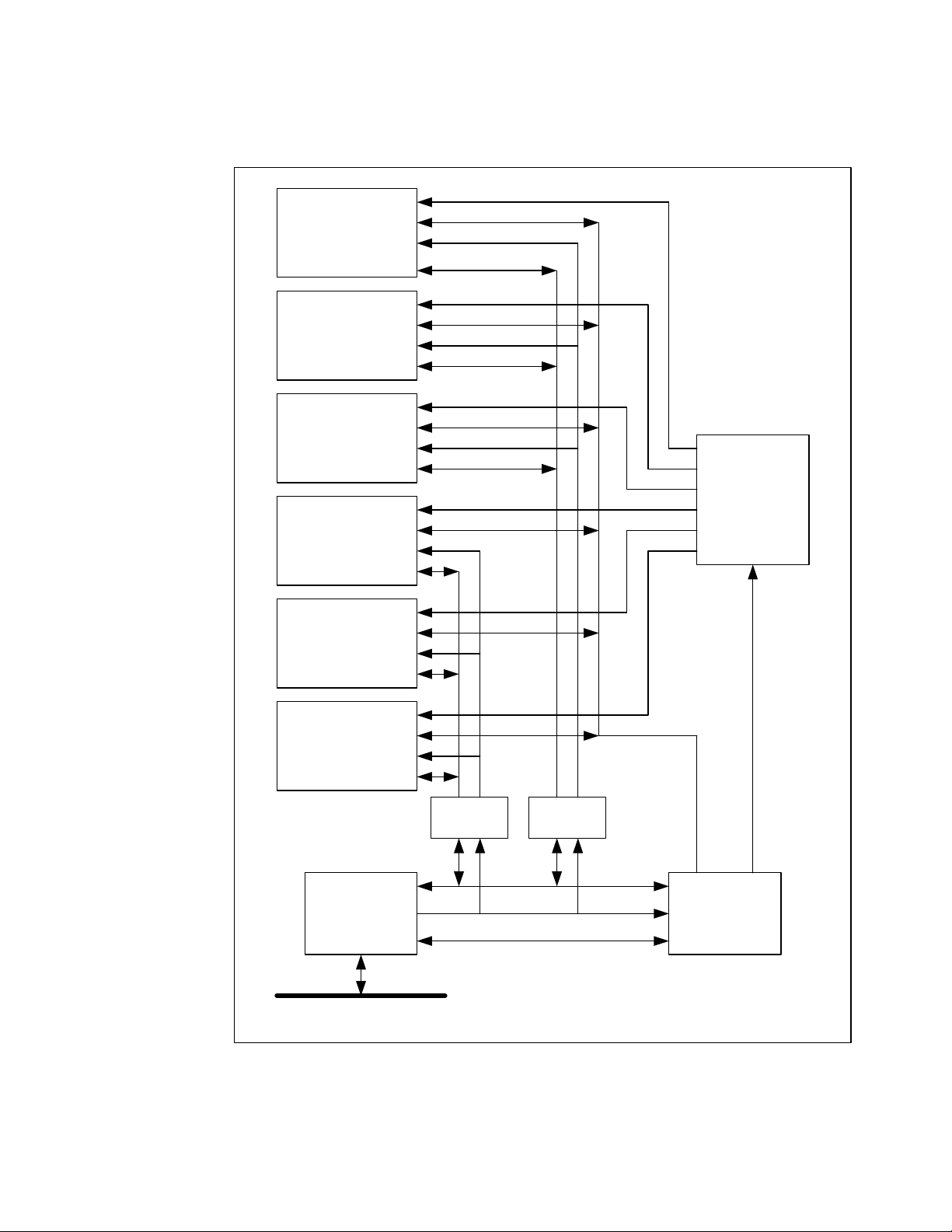

BLOCK DIAGRAM ________________________________________________________3

PCI-60A HARDWARE OVERVIEW __________________________________________4

ADDRESSING OVERVIEW __________________________________________________4

SELECTING THE PCI-60A BASE ADDRESS______________________________________4

I/O SPACE ____________________________________________________________6

ID SPACE _____________________________________________________________7

MEMORY SPACE ACCESSES________________________________________________7

INTERRUPT SPACE_______________________________________________________8

INDUSTRYPACK BUS TIME-OUT _____________________________________________8

STATUS AND CONTROL REGISTER BIT MAPS____________________________________9

INDUSTRYPACK BUS PIN ASSIGNMENTS ______________________________________12

INDUSTRYPACK I/O PIN ASSIGNMENTS _______________________________________13

POWER______________________________________________________________13

PROGRAMMING _______________________________________________________14

PROGRAMMING THE PCI 9080 REGISTERS ____________________________________15

PCI 2.1 Mode______________________________________________________ 15

Read Ahead Mode__________________________________________________ 16

INTERRUPTS __________________________________________________________16

WRITE POSTING _______________________________________________________17

OTHER FEATURES_____________________________________________________18

LED INDICATORS_______________________________________________________18

FUSES ______________________________________________________________19

INSTALLATION OF INDUSTRYPACKS _____________________________________20

USER I/O WIRING ______________________________________________________21

USER OPTIONS________________________________________________________22

SWITCH SW1 _________________________________________________________22

E1 -INDUSTRYPACK STROBE______________________________________________23

CONSTRUCTION AND RELIABILITY_______________________________________24

SPECIFICATIONS ______________________________________________________25

APPENDIX A - DOS EXTENDERS _________________________________________26

REPAIR ______________________________________________________________27

SERVICE POLICY _______________________________________________________27

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com