Spartan Edge Accelerate Board Development Manual--- FPGA Part

Table of Contents

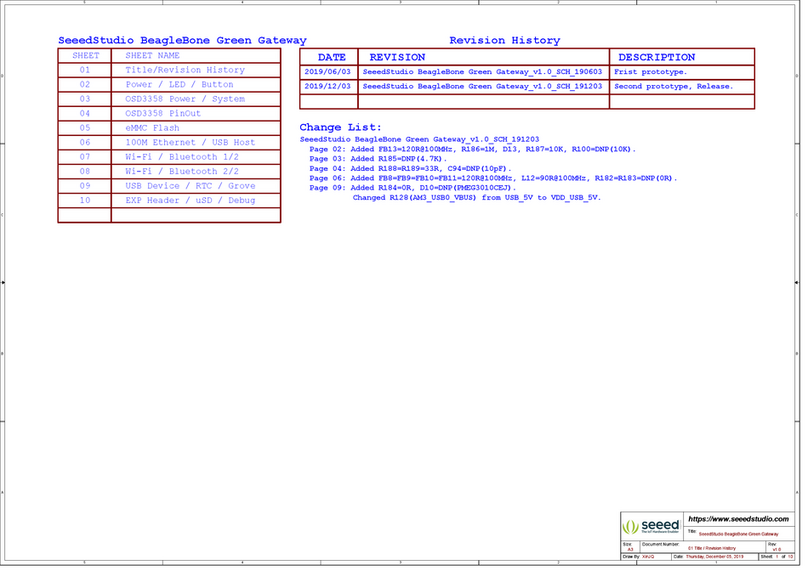

1.Development Description of FPGA ................................................................................................................................10

1.1 Introduction of on-board FPGA configuration..............................................................................................................10

1.2 Detailed description of the on-board FPGA pins.........................................................................................................11

1.3 Description of on-board FPGA interface ............................................................................................................. .17

1.3.1 LED of on-board FPGA peripheral interface.....................................................................................17

1.3.2 Mini HDMI of on-board FPGA peripheral interface ................................................................................. .18

1.3.3 MIPI camera of on-board FPGA peripheral interface.......................................................................18

1.3.4 Gyro of on-board FPGA peripheral interface .................................................................................. 19

1.3.5 ADC of on-board FPGA peripheral interface .......................................................................................... 19

1.3.6 DAC of on-board FPGA peripheral interface .......................................................................................... 20

1.3.7 Buttons of on-board FPGA peripheral interface ..................................................................................... 20

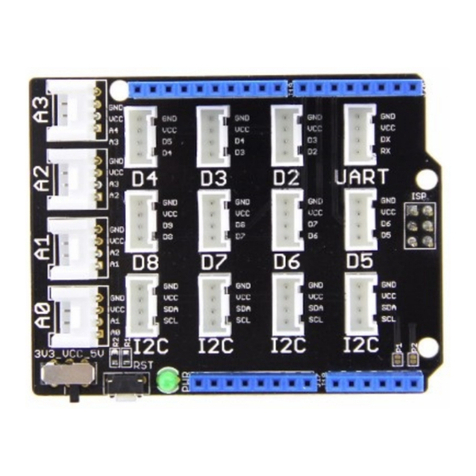

1.3.8 Arduino compatible IO interface of on-board FPGA interface ............................................................. 20

1.3.9 FPGA expansion IO interface of on-board FPGA interface ................................................................. 21

1.4 Peripheral I/O pin of on-board FPGA .................................................................................................................. 21

1.5 Arduino compatible pin of on-board FPGA ........................................................................................................ 22

1.6 IO expansion pin of on-board FPGA ................................................................................................................... 23

2.Front Installation Description of FPGA .................................................................................. .........................................24

2.1 JTAG downloader .................................................................................................................................................. 24

2.2 Additional peripherals ...............................................................................................................................................

26

2.2.1MIPI interface camera of additional peripherals ...................................................................................... 26

2.2.2Display screen of additional peripherals .....................................................................................................

26

3. Description of FPGA Development Platform ...................................................................... .........................................27

3.1 Configuration of Vivado development environment...................................................................................27

3.1 Introduction of use for Vivado IDE ....................................................................................................................... 30

3.2.1 Introduction of start interface .......................................................................................................................

30

3.2.2 Introduction of main interface ......................................................................................................................

31

3.2.3 Introduction of simulation interface .............................................................................................................

38

4.Introduction of FPGA Development Program ...................................................................... .........................................42

4.1 Verilog development ...................................................................................................................................................... 42

4.1.1 Verilog grammar module ................................................................................................................ 42

4.1.2 Execution block of Verilog grammar .............................................................................................. 42

4.1.3 Delay expression of Verilog grammar ............................................................................................ 43

4.1.4 Event expression of Verilog grammar ............................................................................................ 43

4.1.5 If conditional statement of Verilog grammar ................................................................................... 44

4.1.6 Case conditional statement of Verilog grammar ............................................................................. 44