SEMIKRON SKYPER User manual

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 1/37

1. Introduction...............................................................................................................................2

2. Block Diagram and Application Example ........................................................................................3

2.1 Block diagram.......................................................................................................................3

2.2 Application example ..............................................................................................................4

2.2.1 Primary side ...................................................................................................................4

2.2.2 Secondary side ...............................................................................................................5

3. Dimensions and mechanical precautions........................................................................................8

3.1 Dimensions ..........................................................................................................................8

3.2 Plug-in connection .................................................................................................................8

3.3 Support post.........................................................................................................................9

3.4 Solder connection..................................................................................................................9

3.5 Handling instructions ........................................................................................................... 10

4. Interface Description................................................................................................................. 11

4.1 Footprint ............................................................................................................................ 11

4.2 Pin assignment ...................................................................................................................11

4.2.1 Pin assignment of pin header X10 | Primary side............................................................... 11

4.2.2 Pin assignment of pin header X100 | Secondary side | TOP ................................................ 12

4.2.3 Pin assignment of pin header X200 | Secondary side | BOT ................................................12

4.3 Power supply | Primary side ................................................................................................. 13

4.4 Gate drive signals | Primary side ........................................................................................... 14

4.5 Filter selection, jitter and propagation delay time | Primary side ............................................... 15

4.6 Error output | Primary side ................................................................................................... 15

4.7 Error input | Primary side ..................................................................................................... 16

4.8 Error mode selection | Primary side ....................................................................................... 17

4.9 External error input | Secondary side.....................................................................................17

4.10 Gate resistors | Secondary side.............................................................................................19

4.11 External boost capacitors | Secondary side ............................................................................. 20

5. Protection features ................................................................................................................... 21

5.1 Failure management............................................................................................................21

5.2 Dead time and Interlock.......................................................................................................24

5.3 Short pulse suppression (SPS) .............................................................................................. 25

5.4 Undervoltage lockout (UVLO)................................................................................................ 25

5.5 Dynamic short circuit protection by VCEsat-monitoring (DSCP)....................................................26

5.5.1 DSCP | Functional description ......................................................................................... 27

5.5.2 DSCP | Calculation hints ................................................................................................ 28

5.6Active clamping................................................................................................................... 29

5.7 Soft Off..............................................................................................................................30

5.8 Safe short circuit turn-off in multilevel topology ......................................................................31

6. Electrical characteristic.............................................................................................................. 31

7. Product Qualification ................................................................................................................. 32

8. Environmental conditions .......................................................................................................... 33

9. Marking...................................................................................................................................35

Technical Explanation

SKYPER®

12 PV

Revision:

03

Issue date:

2020-05-25

Prepared by:

Niklas Hofstötter

Reviewed by:

Daniel Obernöder

Approved by:

Marco Honsberg

Keyword: IGBT driver core, L5070901

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 2/37

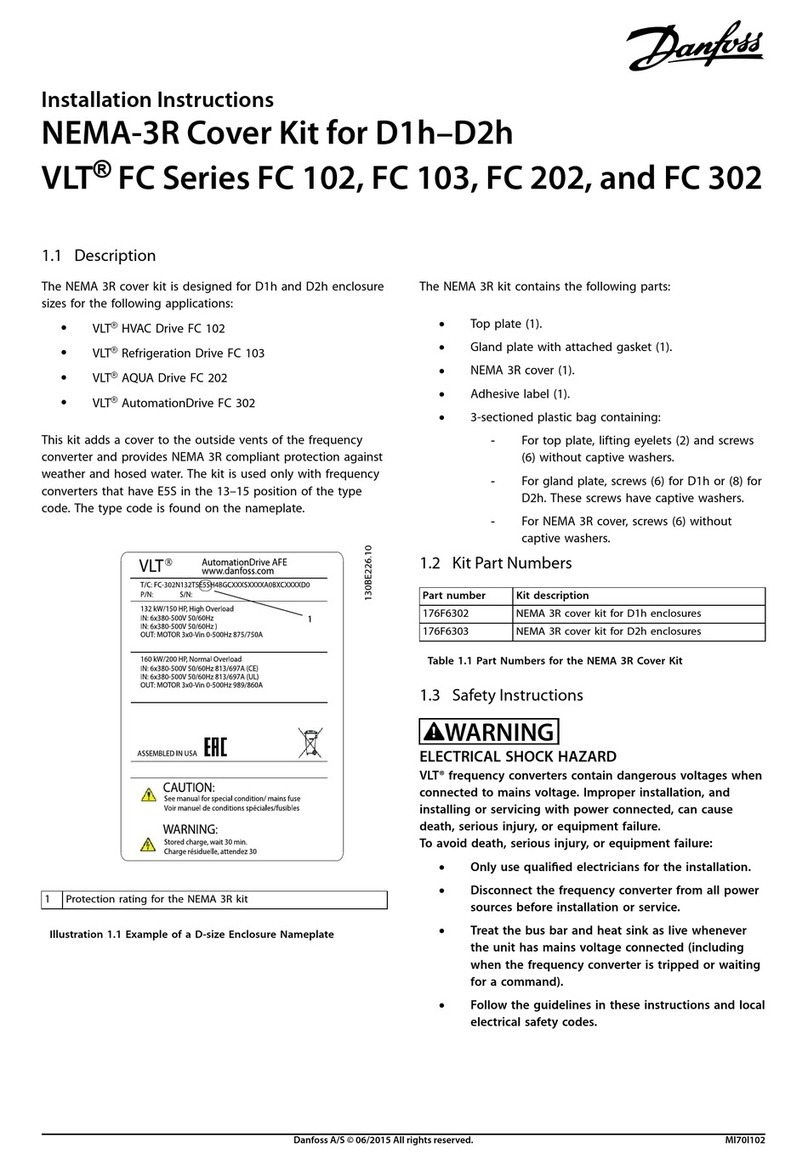

1. Introduction

The SKYPER®12 PV is the most compact driver core within the SKYPER®family and demonstrates its real

advantages in low and medium power photovoltaic and ESS applications. In spite of its unrivalled

compactness of only 36mm x 45mm the SKYPER®12 PV provides reinforced insulation for operating

voltages of up to 1500 VDC in accordance with EN62109-1 & EN61800-5-1. The powerful output stages of

20A peak current per channel drives semiconductor module with gate charges of up to 20µC reliably.

SEMIKRON's highly integrated ASIC technology allows using 30% fewer components than standard

solutions which achieve a MTBF rate of 12 million hours at full load for the dual-channel driver core in

accordance with the industry standard SN29500.

Figure 1: SKYPER®12 PV

KEY FEATURES

Two output channels

1.25W output power and 20A peak output current per channel

Up to 1500V DC-Link voltage

±3 ns jitter per channel

Fully isolated secondary side power supply

Selectable filter settings

Soft turn-off in case of any secondary side error event

Short pulse suppression (SPS)

Under voltage lockout (UVLO)

Dynamic short circuit protection (DSCP)

Selectable error management modes for standard and multilevel applications

MTBF rate > 12 Million hours at full load

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 3/37

2. Block Diagram and Application Example

2.1 Block diagram

Figure 2: SKYPER®12 PV | Block diagram

Power Supply

Management

Power Supply

Management

Short Pulse

Suppression

Interlock

Signal

Processing

Dead Time

Generation

Filter

Management

UVLO

Error

Management

Gate Drive

Management

Power Supply

Management

Error

Management

Error

Management

Gate Drive

Management

UVLO

DSCP

DSCP

UVLO

nERR_IN_TOP

nERR_IN_BOT

PWR_VS_P_BOT

PWR_GND_BOT

PWR_VS_N_BOT

PWR_VS_P_TOP

PWR_GND_TOP

PWR_VS_N_TOP

BOT_ON

BOT_OFF

BOT_SOFTOFF

CLMP_IN_BOT

VCE_IN_BOT

CFG_VCE_BOT

TOP_ON

TOP_OFF

TOP_SOFTOFF

CLMP_IN_TOP

VCE_IN_TOP

CFG_VCE_TOP

PWR_VS

PWR_GND

TOP_IN

BOT_IN

CFG_FLT

CFG_IDT

nERR_IN

nERR_OUT

CFG_ERR

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 4/37

2.2 Application example

Figure 3 and Figure 4 show a typical SKYPER®12 PV core setup to control a multilevel semiconductor

module. The SKYPER®12 PV employs SEMIKRON’s highly-integrated ASIC chipset allowing easy

configuration with only a few simple external circuits and in turn reducing the project and development

time as well as the cost.

2.2.1 Primary side

Figure 3: SKYPER®12 PV | Application example | Primary side

Table 1: SKYPER®12 PV | Application example | Primary side | Recommended values

Component

Value

Remark

CTOP_IN / CBOT_IN

1nF

Optional filter capacitors suppressing high-frequency signals.

For further information please refer to [3].

CBST

-

Optional boost capacitor, dimensioning according to chapter

4.11.

RTOP_IN / RBOT_IN

10kΩ

Optional pull-down resistors, for steady off state of the

corresponding output, if no input signal is applied.

RnERR_OUT

4.75kΩ

Optional pull-up resistor, mandatory if error output is used.

Dimensioning according to chapter 4.6

PWR_GNDX10:01

CBST

SKYPER®12 PV

PWR_VSX10:09

CFG_ERRX10:05

PWR_VSX10:10

nERR_OUTX10:03

nERR_INX10:04

PWR_VS

TOP_INX10:07

PWR_GNDX10:01

nERR_OUT

TOP_IN

RnERR_OUT

CTOP_IN

RTOP_IN

BOT_INX10:08

PWR_GNDX10:01

BOT_IN

CBOT_IN

RBOT_IN

CFG_IDTX10:02

CFG_FLTX10:06

PWR_GNDX10:01PWR_GND

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 5/37

2.2.2 Secondary side

Figure 4: SKYPER®12 PV | Application example | Secondary side

DC+

RG(on)_TOP

RG(softoff)_TOP

RVCE_TOP DVCE_TOP

DGE_TOP

T1

SKYPER®12 PV

VCE_IN_TOP X100:02

TOP_ON X100:05

TOP_OFF X100:06

TOP_SOFTOFF X100:09

PWR_GND_TOP X100:08

RG(off)_TOP

RGE_TOP

CGE_TOP

VCE_IN_BOT X200:02

BOT_ON X200:05

BOT_OFF X200:06

BOT_SOFTOFF X200:09

PWR_GND_BOT X200:08

RG(on)_BOT

RG(softoff)_BOT

RVCE_BOT DVCE_BOT

DGE_BOT

T2

RG(off)_BOT

RGE_BOT

CGE_BOT

N

PWR_VS_P_TOP X100:03

nERR_IN_TOP X100:04

CFG_VCE_TOP X100:01

CLMP_IN_TOP X100:07

PWR_GND_TOP X100:08

PWR_VS_N_TOP X100:10

CBST(N)_TOP

R2_CFG_TOP

R1_CFG_TOP

CCFG_TOP

CBST(P)_TOP

PWR_VS_P_BOT X200:03

nERR_IN_BOT X200:04

CFG_VCE_BOT X200:01

CLMP_IN_BOT X200:07

PWR_GND_BOT X200:08

PWR_VS_N_BOT X200:10

CBST(N)_BOT

R2_CFG_BOT

CCFG_BOT

CBST(P)_BOT

R1_CFG_BOT

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 6/37

Table 2: SKYPER®12 PV | Application example | Secondary side | Recommended values

Component

Value

Remark

CBST(P)_TOP / CBST(N)_TOP

CBST(P)_BOT / CBST(N)_BOT

-

Optional boost capacitors, dimensioning according to chapter

4.11.

CCFG_TOP / CCFG_BOT

-

Optional capacitor to adjust the blanking time tbl(VCE) of the

dynamic short circuit protection function. Necessary, if DSCP

is used. Dimensioning according to chapter 5.5.

CGE_TOP / CGE_BOT

-

Optional capacitor to prevent gate oscillation in case of short

circuit events or in case of parallel operation of semiconductor

power modules. For further information please refer to [3].

DGE_TOP / DGE_BOT

Optional suppressor diode to prevent gate voltage

overshoots. For further information please refer to [3].

DVCE_TOP / DVCE_BOT

-

Optional high voltage diode for VCE-monitoring, mandatory if

DSCP is used. Dimensioning according to chapter 5.5.

R1_CFG_TOP / R1_CFG_BOT

≥ 10kΩ

Optional resistors to adjust the trip level VCE(ref) of the

dynamic short circuit protection, necessary if DCSP is used.

Dimensioning according to chapter 5.5.

R2_CFG_TOP / R2_CFG_BOT

-

Optional resistors to adjust the trip level VCE(ref) of the

dynamic short circuit protection, necessary if DCSP is used.

Dimensioning according to chapter 5.5.

RGE_TOP / RGE_BOT

10kΩ

Optional resistor to avoid an open gate of the semiconductor,

if the driver is not supplied. For further information refer to

[3].

RG(off)_TOP / RG(off)_BOT

RG(on)_TOP / RG(on)_BOT

≥ 1.25Ω

Necessary resistors to adjust the semiconductors’ turn-on

and turn-off behavior. Dimensioning according to chapter

4.10.

RG(softoff)_TOP

RG(softoff)_BOT

≥ 1Ω

Mandatory resistor to adjust the semiconductors’ turn-off

behavior in case of soft turn-off. Dimensioning according to

chapter 4.10.

RVCE_TOP / RVCE_BOT

511Ω

Optional series resistor for VCE-monitoring, mandatory if

DSCP is used.

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 7/37

Referring to the application example shown in Figure 3 and Figure 4, Table 3 describes the settings made.

Table 3: SKYPER®12 PV | Application example | Settings

Function

Configuration

Remark

Chapter

Active clamping

Disabled

Disabled by connecting the pins

CLMP_IN_TOP and CLMP_IN_BOT to

the corresponding PWR_GND pins.

5.6

Bidirectional error

(=HALT)

Disabled

Disabled by connecting the pin

nERR_IN to pin PWR_VS.

4.7

Dynamic short circuit

protection (DSCP)

Enabled at both output

channels

Enabled by connecting the pins

VCE_IN_TOP and VCE_IN_BOT to the

corresponding collectors of the

semiconductors through RVCE_TOP,

DVCE_TOP and RVCE_BOT, DVCE_BOT.

DSCP configuration via pins

CFG_VCE_TOP and CFG_VCE_BOT.

5.5

Dead time generation

Disabled

Disabled by connecting pin CFG_IDT to

pin PWR_VS.

5.2

Error mode

In case of any secondary

side error condition the

event will be reported at

the pin nERR_OUT. The

driver turns-off the

affected output

immediately and the

second output with the

next turn-off signal at

the corresponding input.

Both outputs remain

blocked until the error

state is reset .

Selected by connecting pin CFG_ERR to

pin PWR_VS.

5.1

Error propagation

delay time

700ns (typical value)

Fixed value.

5.1

External error

Disabled at both

secondary sides.

Disabled by connecting the pins

nERR_IN_TOP and nERR_IN_BOT to

the corresponding PWR_VS pins.

5.1

Filter

Analogue

Selected by connecting pin CFG_FLT to

pin PWR_GND.

5.3

Interlock

Disabled

Disabled by connecting pin CFG_IDT to

pin PWR_VS.

5.2

Jitter

±3ns (typical value)

Selected by connecting the pin

CFG_FLT to pin PWR_GND.

4.5

Short pulse

suppression (SPS)

200 ns (typical value)

Selected by connecting pin CFG_FLT to

pin PWR_GND.

5.3

Undervoltage lockout

(UVLO)

Always active on primary

and secondary side

-

5.4

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 8/37

3. Dimensions and mechanical precautions

3.1 Dimensions

Figure 5: SKYPER®12 PV | Dimension drawing

All dimensions in mm. Please consider higher tolerances of connector position according to IPC A 610.

STEP file on request.

3.2 Plug-in connection

The SKYPER®12 PV provides simple electrical and mechanical connection to adapter or control boards by

its standard pin headers. The primary side and the two secondary side plug-in connectors are 10 pin dual

row 2.54mm pin headers. For a secure mechanical connection of the SKYPER 12 PV IGBT driver it is

essential that the pin headers can be fully supported by the female mating connectors.

Example for a suitable female mating connector:

Description

Shape

Manufacturer

Art. no.

(female) RM2.54 10p

SMD 2ROW

Suyin

254100FA

Using SMD type mating connectors allows optimized board layout especially for SEMIKRON’s spring contact

modules like SEMiX.

8,13

8.13

18,79

max. 20.00

5,092.54

5,212.54

3,42

44,70

3,42 36,08

35,80

3.42

33.75

45.00

3.42

36.00

36.4

Ø3,2

AA 2:1

41,17

4,13 4,15

4,40

13,68

4.13

13.77

3.42

4.52

41.27

4.23

3.2

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 9/37

3.3 Support post

To increase the robustness of the mechanical connection between the SKYPER®12 PV driver and the

corresponding board a support post could be assembled. If a support post is used, make sure it has the

correct length. A too short support post would bend both, the driver and the corresponding board that it is

mounted on, thus increasing mechanical stress. If the support post is too long, the mating connectors may

not fully support the pin header and insufficient or instable electrical and mechanical contact might occur.

The mounting hole is located in the insulation area between the secondary sides of the driver. To avoid

reduction of creepage and clearance distances when utilizing a support post, the support post’s material

must have a CTI 600 classification at least.

Example of a support post:

Description

Shape

Manufacturer

Art. no.

Nylon support post

Dual lock

Essentra

DLMSPM-8-01 (>12mm)

Figure 6: SKYPER®12 PV | Support post

mounting hole for support post principle of a supported driver on an adapter

board

3.4 Solder connection

The SKYPER®12 PV driver core can be soldered directly onto an adapter or control board. It should be

noted that if the driver is placed too close to the adapter or control board, the clearance distances from the

driver’s primary to secondary side as well as the clearance distances between the secondary sides may be

reduced.

Soldering hints

•The solder’s temperature must not exceed 260°C and the solder time must not exceed 10 seconds.

•The ambient temperature must not exceed the specified maximum storage temperature of the driver.

•The solder joints should be in accordance to IPC A 610 Revision D (or later) - Class 3 (Acceptability of

Electronic Assemblies) to ensure an optimum connection between driver core and printed circuit

board.

•The driver is not suited for hot air, reflow or infrared reflow processes.

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 10/37

3.5 Handling instructions

Please ensure electric static discharge protection during handling. The driver should only be removed from

its original packaging just before mounting. When mounting the driver it has to be ensured that the work is

done in an ESD-protected workplace environment. Persons working with the driver have to wear ESD

wristbands, overalls and shoes. If tools are used for mounting, those must comply with ESD standards.

When handling the driver, do not pick up the driver at the transformers. The driver MUST be handled at the

PCB sides.

Figure 7: SKYPER®12 PV | Handling instruction

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 11/37

4. Interface Description

4.1 Footprint

The footprint of the SKYPER®12 PV with its primary side pin header X10 and the secondary side pin

headers X100 and X200 are shown in Figure 8.

Figure 8: SKYPER®12 PV | Footprint | Bottom view

4.2 Pin assignment

4.2.1 Pin assignment of pin header X10 | Primary side

Table 4: SKYPER®12 PV | Pin assignment –Primary side | X10

Pin

Signal

Function

Specification

X10:01

PWR_GND

Ground potential of power

supply and digital signals

To be connected to ground

X10:02

CFG_IDT

Interlock dead time

configuration

15V logic; 150kΩ (pull-up)

LOW = 2µs interlock dead time

HIGH = No interlock dead time

X10:03

nERR_OUT

Error output

Open collector output; max. 18V/15mA

(external pull-up resistor needed)

LOW = Error

HIGH = No error

X10:04

nERR_IN

Error input

15V logic inverted; 150kΩ/10nF (pull-up)

LOW = External error

HIGH = No external error

X10:05

CFG_ERR

Error behaviour

configuration in case of any

error condition

15V logic; 150kΩ (pull-down)

LOW = Both outputs switch off

HIGH = Affected output switches off

X10:06

CFG_FLT

Filter configuration for

switching signals

15V logic; 150kΩ (pull-down)

LOW = Analogue filter (tSPS(ana))

HIGH = Digital filter (tSPS(dig))

X10:07

TOP_IN

Switching signal input (TOP)

15V logic; 33kΩ/0.01nF (pull-down)

LOW = TOP switch off

HIGH = TOP switch on

X10:08

BOT_IN

Switching signal input (BOT)

15V logic; 33kΩ/0.01nF (pull-down)

LOW = BOT switch off

HIGH = BOT switch on

X200

X100

X10

1

10

1

10 1

10

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 12/37

X10:09

PWR_VS

Driver power supply

Stabilised +15V ±3%

X10:10

PWR_VS

Driver power supply

Stabilised +15V ±3%

4.2.2 Pin assignment of pin header X100 | Secondary side | TOP

Table 5: SKYPER®12 PV | Pin assignment –Secondary side | TOP | X100

Pin

Signal

Function

Specification

X100:01

CFG_VCE_TOP

VCE-monitoring reference

voltage

External voltage divider needed

X100:02

VCE_IN_TOP

VCE-monitoring input

External blocking diode needed

X100:03

PWR_VS_P_TOP

Power supply output,

positive voltage

Equal to VG(on)

(external buffer capacitors can be

optionally connected)

X100:04

nERR_IN_TOP

External error input

15V logic inverted; 150kΩ/0.01nF (pull-up)

LOW = External error

HIGH = No external error

X100:05

TOP_ON

On signal terminal for TOP

semiconductor

External gate resistor needed

(under consideration of Iout(avg), Iout(peak),

VG(on))

X100:06

TOP_OFF

Off signal terminal for TOP

semiconductor

External gate resistor needed

(under consideration of -Iout(avg), -Iout(peak),

VG(off))

X100:07

CLMP_IN_TOP

VCE-clamping input

150kΩ/0.01nF (pull-down)

In case of activated TOP_OFF:

LOW = TOP_OFF equal to VG(off)

HIGH = TOP_OFF floating

X100:08

PWR_GND_TOP

Ground potential of power

supply and digital signals

Reference potential of gate voltages

(emitter/source of power semiconductor)

X100:09

TOP_SOFTOFF

SoftOff signal terminal for

TOP semiconductor

External gate resistor needed

X100:10

PWR_VS_N_TOP

Power supply output,

negative voltage

Equal to VG(off)

(external buffer capacitors can be

optionally connected)

4.2.3 Pin assignment of pin header X200 | Secondary side | BOT

Table 6: SKYPER®12 PV | Pin assignment –Secondary side |BOT | X200

Pin

Signal

Function

Specification

X200:01

CFG_VCE_BOT

VCE-monitoring reference

voltage

External voltage divider needed

X200:02

VCE_IN_BOT

VCE-monitoring input

External blocking diode needed

X200:03

PWR_VS_P_BOT

Power supply output,

positive voltage

Equal to VG(on)

(external buffer capacitors can be

optionally connected)

X200:04

nERR_IN_BOT

External error input

15V logic inverted; 150kΩ/0.01nF (pull-up)

LOW = External error

HIGH = No external error

X200:05

BOT_ON

On signal terminal for BOT

semiconductor

External gate resistor needed

(limits under consideration of Iout(avg),

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 13/37

Iout(peak), VG(on))

X200:06

BOT_OFF

Off signal terminal for BOT

semiconductor

External gate resistor needed

(limits under consideration of -Iout(avg), -

Iout(peak), VG(off))

X200:07

CLMP_IN_BOT

VCE-clamping input

150kΩ/0.01nF (pull-down)

In case of activated BOT_OFF:

LOW = BOT_OFF equal to VG(off)

HIGH = BOT_OFF floating

X200:08

PWR_GND_BOT

Ground potential of power

supply and digital signals

Reference potential of gate voltages

(emitter/source of power semiconductor)

X200:09

BOT_SOFTOFF

SoftOff signal terminal for

BOT semiconductor

External gate resistor needed

X200:10

PWR_VS_N_BOT

Power supply output,

negative voltage

Equal to VG(off)

(external buffer capacitors can be

optionally connected)

4.3 Power supply | Primary side

For a proper operation of the SKYPER®12 PV driver core, a power supply of at least 15W/1A shall be

connected to the driver’s power supply pins. During power-up of the driver turn-on signals should not be

applied to the driver’s inputs TOP_IN/BOT_IN, otherwise the driver will not leave the error state.

Please note, when controlling power semiconductor modules with a gate charge ≥ 2.5 µC external boost

capacitors (CBST) are recommended to support the supply voltage on the primary side. Dimensioning of

such boost capacitors shall be done according to chapter 4.11.

Figure 9: SKYPER®12 PV | Primary side | Power supply

SKYPER®12 PV

CBST

PWR_VS

PWR_GND PWR_GNDX10:01

PWR_VSX10:10

PWR_VSX10:09

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 14/37

4.4 Gate drive signals | Primary side

The signal inputs TOP_IN/BOT_IN of the SKYPER®12 PV driver core have a +15V schmitt trigger logic. A

HIGH signal at the input of the driver turns on the corresponding output of the driver. A LOW signal at the

input leads to a switch-off command at the corresponding output. Pulses below 1µs are not allowed.

Short pulses as well as voltage peaks, e.g. caused by interference, are suppressed by the driver and will

not be transmitted to the outputs. Further information to the short pulse suppression are referred in

chapter 5.3.

Figure 10: SKYPER®12 PV | Primary side | Gate drive signals

When using the driver in environments with high levels of electromagnetic noise, it is recommended to

connect a filter capacitor (CTOP_IN/CBOT_IN) of several hundred pico Farads as close as possible to the signal

inputs. Please note that these capacitors affect the propagation delay time of the driver. The RTOP_IN/RBOT_IN

resistors pull the inputs to low-level when no control signals are applied. The recommended value of the

pull-down resistors is approximately 10kΩ.

Parameter

Min

Typ

Max

Threshold high

-

-

10V

Threshold low

5V

-

-

SKYPER®12 PV

CTOP_IN

TOP_IN

PWR_GND

RTOP_IN

PWR_GNDX10:01

TOP_INX10:07

CBOT_IN

BOT_IN

PWR_GND

RBOT_IN

PWR_GNDX10:01

BOT_INX10:08

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 15/37

4.5 Filter selection, jitter and propagation delay time | Primary side

SEMIKRON’s highly-integrated mixed signal ASICs the SKYPER®12 PV permit the selection of filter type,

jitter and propagation delay time to meet specific requirements of applications.

The filter time can be set via the configuration pin CFG_FLT. Connecting the CFG_FLT pin to the PWR_VS

pin enables the digital filter employing very low tolerances over the full temperature range.

Depending on the settings made the SKYPER®12 PV driver provides a very low jitter of typically ±3ns. For

this mode, the analogue filter has to be enabled and the driver’s internal dead time generator has to be set

inactive. The dead time generator is inactive, if either the interlock feature is disabled via the CFG_IDT pin

or the dead time of the applied pulse pattern is longer than the dead time of internal generator of the

driver of typically 2µs. A detailed description of the interlock function and the dead time generation is

referred in chapter 5.2.

CFG_FLT

CFG_IDT

Setting

Filter time

Delay time

Jitter

HIGH

HIGH/LOW

Digital filter

390ns

830ns

±12.5ns

LOW

LOW

Analogue filter

200ns

500ns

±3ns /±12.5ns

LOW

HIGH

Analogue filter

200ns

500ns

±3ns

4.6 Error output | Primary side

The SKYPER®12 PV reports any detected error event at the nERR_OUT pin by pulling it to low-level. The

error output is an open collector output and requires an external pull-up resistor (RnERR_OUT). The

recommended value of the pull-up resistor is in the range of

.

As long as the driver has not been reset the error output will be at low-level.

A detailed description, how to reset the driver to exit the error state and resume to operation is described

in chapter 5.1.

Figure 11: SKYPER®12 PV | Primary side | Error output

Please note, if the nERR_OUT terminal of SKYPER®12 PV is directly connected to a nERR_OUT terminal of

another SKYPER®12 PV driver, only one pull-up resistor must to be applied.

SKYPER®12 PV

PWR_VS

nERR_OUT nERR_OUTX10:03

PWR_VSX10:09

PWR_GND PWR_GNDX10:01

RnERR_OUT

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 16/37

4.7 Error input | Primary side

The nERR_IN input is optionally used to report a system related external error event to the

SKYPER®12 PV. If the nERR_IN input is pulled down to low-level the driver enters into error state.

Depending on the error mode configuration, described in chapter 4.8, the driver sets its outputs either

immediately or with the next turn-off command at its corresponding input to low-level and locks them.

After reset, as described in chapter 5.1, the driver will be ready to transfer the signals to the output stage

again. If no reporting to the external error input is required, the nERR_IN input can be connected to the

PWR_VS pin or to the nERR_OUT pin.

In multiphase or parallel operation the nERR_IN input offers the possibility to force the outputs of each

driver in the system to off-state and locks them, simultaneously, without the need of an external control

unit. Therefore all nERR_OUT outputs and all nERR_IN inputs have to be connected together forming a

common bi-directional HALT line. Additionally, all CFG_ERR configuration pins have to be connected to

ground potential, as shown in Figure 12. In this configuration, any driver connected to the HALT line can

force the outputs of all connected drivers to off-state and locks them, when the driver pulls its nERR_OUT

output to low-level.

If a specific turn-off sequence is required –as it is common practice in NPC multilevel applications –the

configuration pins CFG_ERR have to be connected to the PWR_VS pins. A low-level of the HALT line locks

the outputs of the connected drivers, but does not immediately force them to low-level. Outputs which are

in on-state can be forced to off-state by the controller sending a turn-off command to the corresponding

signal inputs TOP_IN/BOT_IN.

If the driver is used in environments with high levels of EMI noise, it is recommended to connect an

additional filter capacitor as close as possible to the nERR_IN pin and the PWR_GND pin.

Figure 12: SKYPER®12 PV | Primary side | Error input

Parameter

Min

Typ

Max

Threshold high

-

-

11 V

Threshold low

7.5 V

-

-

SKYPER®12 PV | 1

PWR_VS

nERR_OUT nERR_OUTX10:03

PWR_VSX10:09

PWR_GNDX10:01

RnERR_OUT

SKYPER®12 PV | 2

nERR_OUTX10:03

nERR_INX10:04

PWR_GND PWR_GNDX10:01

nERR_INX10:04

X10:05 CFG_ERR

X10:05 CFG_ERR

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 17/37

4.8 Error mode selection | Primary side

The configuration pin CFG_ERR selects the behavior of the SKYPER®12 PV driver core on error events.

Connecting the CFG_ERR pin to the PWR_GND pin forces the driver to set its outputs to off-state

immediately when an error is detected. As long as the driver has not been reset the error event is reported

at the corresponding output and the driver’s outputs are locked. Whereby, depending on whether an error

is detected on the primary or on the secondary side the driver switches off the connected semiconductors

via the standard turn-off or the soft-off path. If an error occurs on the primary side the driver will activate

the standard turn-off paths of both channels. If an error occurs on the secondary side, the driver will

activate the soft-off path of the affected secondary side. The semiconductor connected to the other

secondary side will be switched off via the standard turn-off path.

If the CFG_ERR pin is connected to the PWR_VS pin, the driver locks its outputs in case of any error event’s

occurrence and, hence, reports the error event at the terminal nERR_OUT. The affected output at which the

error occurred will be set to off-state, immediately. The second output will be set to off state when the

driver has received a turn-off command at the corresponding signal input TOP_OFF/BOT_OFF. Depending

on whether an error is detected on the primary or secondary side the driver activates the standard turn-off

or the soft-off path, as described above.

Further information related to the primary and secondary side error events, as well as on the error reset

conditions is referred in chapter 5.1.

4.9 External error input | Secondary side

Each secondary side of the driver provides an error input (nERR_IN_TOP/nERR_IN_BOT) to handle external

error events. These inputs are low active. Pulling one input to low-level forces the driver into error state.

The behaviour of the driver in case of an external error event depends on the configuration at the

configuration pin CFG_ERR, as described in chapter 4.8.

The external error input is typically used to monitor temperature, current or voltage of modules, phase legs

or systems. The error input of the secondary TOP/BOT side can be disabled by connecting it to the

PWR_VS_P_TOP/PWR_VS_P_BOT pin.

Figure 13 shows a recommended comparator circuitry to process the NTC’s signal and derive the required

logic signal for the input of the SKYPER®12 PV. When the voltage at the comparator’s positive input falls

below the voltage level of the negative input the nERR_IN input will be pulled to low-level and generates an

external error event. Assuming that resistors R3and R4have the same value the comparator’s trip level is

reached when the value of the NTC falls below the value of RCGF(temp). Please note that the negative supply

pin of the comparator is connected to PWR_VS_N which has to be taken into account, in case the NTC

thermistor is monitored by an external application circuit in addition.

Figure 13: SKYPER®12 PV | Secondary side | Example of an external error input circuitry

R1

SKYPER®12 PV

PWR_VS_P_TOP X100:03

nERR_IN_TOP X100:04

PWR_GND_TOP X100:08

PWR_VS_N_TOP X100:10

ϑ

R2

C1

C2

RCFG(temp)

C3

R3

R4

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 18/37

Recommended values

Component

Value

Remark

C1

1nF

C2

100nF

C3

1µF

R1

30.1kΩ

R2

15kΩ

R3

30.1kΩ

R4

30.1kΩ

RCFG(temp)

-

The value of the resistor RCFG(temp) has to be determined

considering the resistance characteristic of the connected

thermistor and the desired trip level.

Parameter

Min

Typ

Max

Threshold high

-

-

13 V

Threshold low

2 V

-

-

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 19/37

4.10 Gate resistors | Secondary side

Equipped with three output channels at each secondary side (TOP_ON/TOP_OFF/TOP_SOFTOFF and

BOT_ON/BOT_OFF/BOT_SOFTOFF) the SKYPER®12 PV driver offers the possibility to optimize turn-on and

turn-off behavior of the IGBT separately. By default, the driver uses the TOP_ON/TOP_OFF and

BOT_ON/BOT_OFF output to turn-on or turn-off the connected semiconductor. The SOFTOFF output will be

activated by the driver if a secondary side error event has been detected to turn-off of the connected

semiconductor slowly, which in turn shall prevent from excessive voltage overshoots to protect the

semiconductor against destruction by over voltage. It is mandatory to populate a suitable soft-off gate

resistor, otherwise the semiconductor will not be turned-off in case of a secondary side error. A detailed

explanation of when the driver is activating the soft-off path is referred in chapter 4.8.

The gate resistor influences the IGBT switching time, switching losses, reverse bias safe operating area

(RBSOA), short-circuit safe operating area (SCSOA), EMI, dV/dt, di/dt and reverse recovery current of the

freewheeling diode. The gate resistor essentially optimizes the safe operation of the power semiconductor

in accordance with the individual application parameters, e.g. IGBT technology, diode, switching frequency,

losses, application layout, inductivity / stray inductance, DC-link voltage and driver capability. The

complete design of an application must be viewed as a whole, with due considering of the above-mentioned

parameters at least. Interacting and interfering effects within the whole application must be considered,

evaluated and addressed. [4]

The minimum value of the gate resistors RG(on) and RG(off) could be calculated by the following equation:

The minimum allowed value of the RG(softoff) is 1Ω. Additional hints how to determine the values of the gate

resistors are referred in [4].

Figure 14: SKYPER®12 PV | Secondary side | Gate resistors

Please note that some of SEMIKRON’s driver cores using an ASIC internal N-channel MOSFET for Soft Off.

To protect this MOSFET against stress when turning-off the TOP_ON/BOT_ON channel it is recommended to

place the RG(softoff) resistor in series with the RG(off) resistor.

Since each turn-on and turn-off of a semiconductor means charging or discharging the input capacitance of

the connected power semiconductor, the gate resistor has to be suitable for such pulse load. For this

reason, SEMIKRON recommends the use of pulse current suitable resistors. The following table provides

examples.

DC+

RG(on)_TOP

RG(softoff)_TOP

T1

SKYPER®12 PV

TOP_ON X100:05

TOP_OFF X100:06

TOP_SOFTOFF X100:09

PWR_GND_TOP X100:08

RG(off)_TOP

AC

RG(int)_TOP

RE_TOP

IGBT

© by SEMIKRON / 2020-05-25 / Technical Explanation / SKYPER®12 PV

PROMGT.1026/ Rev.7/ Template Technical Explanation

Page 20/37

Description

Shape

Manufacturer

Art. no.

MELF resistors

MELF / MiniMELF SMD

Vishay Beyschlag,

Vishay Draloric,

Vitrohm

PRO MELF resistors,

SMM0207, SMM 0204,

ZCM series

4.11 External boost capacitors | Secondary side

The SKYPER®12 PV allows driving of semiconductor power modules with a gate charge (QG) of up to 20µC

per output. To stabilize the gate voltages VG(on) and VG(off) during the semiconductor switching, the use of

boost capacitors for each output channel is recommended, if the connected gate charge is larger than

2.5µC. For maximum effectiveness, these capacitors have to be placed as close as possible to the

corresponding terminal as shown in Figure 15.

Figure 15: SKYPER®12 PV | Secondary side | Boost capacitors

The required capacitance of the optional external boost capacitors can be estimated by the following

equation:

Please note, when assembling boost capacitors at the secondary sides, also boost capacitors have to be

assembled at the primary side, as shown in Figure 9.

SKYPER®12 PV

CBST(N)_TOP

CBST(P)_TOP

PWR_VS_P_TOP X100:03

PWR_GND_TOP X100:08

PWR_VS_N_TOP X100:10

Table of contents

Other SEMIKRON DC Drive manuals

Popular DC Drive manuals by other brands

Hertz

Hertz HDD Series instruction manual

SOMFY

SOMFY Sonesse 50 RTS Installation and operating guide

ITOH DENKI

ITOH DENKI POWER MOLLER 24 HBM-604BN manual

Sealey

Sealey PPD100 quick guide

BONFIGLIOLI

BONFIGLIOLI ACTIVE ACT2 Series quick start guide

GFA

GFA ELEKTROMAT SI 35.100 FU-40,00 installation instructions

easydriver

easydriver basic 1.8 Installation and instruction manual

Montech

Montech 508815 Assembly instructions

GFA

GFA ELEKTROMAT SI 25.15-30,00 installation instructions

Digga

Digga HH-6K Operator's manual

Danfoss

Danfoss NEMA-3R installation instructions

Moeller

Moeller DF4-340 Series installation instructions