Sequential 242 User manual

MODEL 242

OPERATION MANUAL

^EOUEfliiAL

SEQUENTIAL

Publications Department Publications Number: M242A

Issued: October, 1984

MODEL 2 2

MIDI INTERFACE CARTRIDGE

FOR THE COMMODORE 6 R

OPERATION MANUAL

By Stanley Jungleib

and Chet Wood

Sequential Sequential

POSTBUS 16 3051 North First Street

3640 AA Mijdrecht San Jose, A 95134-2093

Netherlands U.S.A.

02979-6211 408/946-5240

TELEX: 12721 SQNTL NL TELEX: 4997150 SEQ IR

MODEL 2 2

MIDI INTERFACE CARTRIDGE

FOR THE COMMODORE 6 R

OPERATION MANUAL

By Stanley Jungleib

and Chet Wood

ommodore 64 is a registered trademark of ommodore Business

Machines, Inc.

Manual No. M242A

Issued: October, 1984

©1984 by

SEQUENTIAL IR UITS, IN .

All rights reserved.

M242A 2

Table of Contents

TOPI PAGE

OVERVIEW

CONNECTION AND OPERATION 5

Figure 1: onnection Diagram 5

HARDWARE 7

OVERVIEW 7

Figure 2: Block Diagram 7

INTEGRATED IR UITS 8

Figure 3: Schematic Diagram 9

OTHER PARTS 11

PROGRAMMING 12

INTERRUPTS 12

DRUM LO K INPUT OPTIONS 13

Table 1: PIA ontrol Modes 13

Table 2: A IA ontrol Modes 13

Table 3: PIA Addressing 13

Table 4: A IA Addressing 13

INITIALIZATION 14

TRANSMITTING MIDI DATA 14

RE EIVING MID DATA 14

READING THE FOOTSWIT H 14

READING THE DRUM LO K INPUT! 4

BASI PROGRAM EXAMPLE 15

PROGRAMMING IN ASSEMBLY 18

M242A 3

OVERVIEW

ongratulations on your purchase of the Sequential ircuits Model

242 MIDI cartridge for the ommodore 64 ( 64). This cartridge,

together with the 900 series of diskette-based software from

Sequential, allows you to perform minor miracles with your MIDI-

equipped musical instruments.

To use the Model 242, you need the following:

ommodore 64 computer and power supply

Monitor (or TV)

ommodore floppy diskette drive

1 or 2 MIDI cables (depending on the application)

MIDI synthesizer

Audio cable and sound system, or headphones

Applications diskette (unless you plan to program the cartridge

yourself)

Data diskette (depending on the application)

Footswitch (if desired)

able for drum machine (if used)

This operation manual is in three sections:

CONNECTION AND OPERATION covers basic installation. It is

very short and intended for everyone.

HARDWARE describes the 242 and its theory of operation in

detail, for the technically curious.

PROGRAMMING explains theory and gives examples in both

BASI and assembly language for those who wish to write their

own MIDI programs.

M242A 4

ONNE TION AND OPERATION

AUTION! Always switch power off to all equipment in use before

connecting or disconnecting anything. Otherwise, serious damage may

result to the 64 or cartridge.

MODEL

242

>EOUcniidL CRCUiti snc

COMMODORE 64

—f\\

----

iTr™1nr|V= TlY::-V ,l l\

----

1

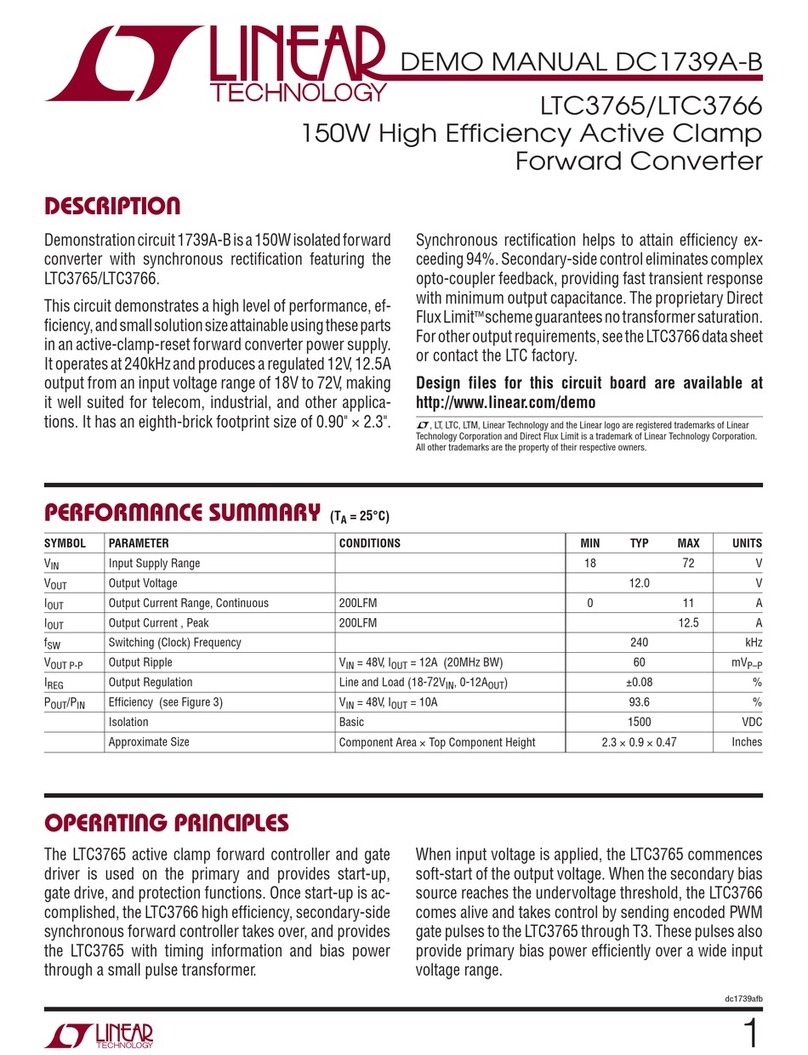

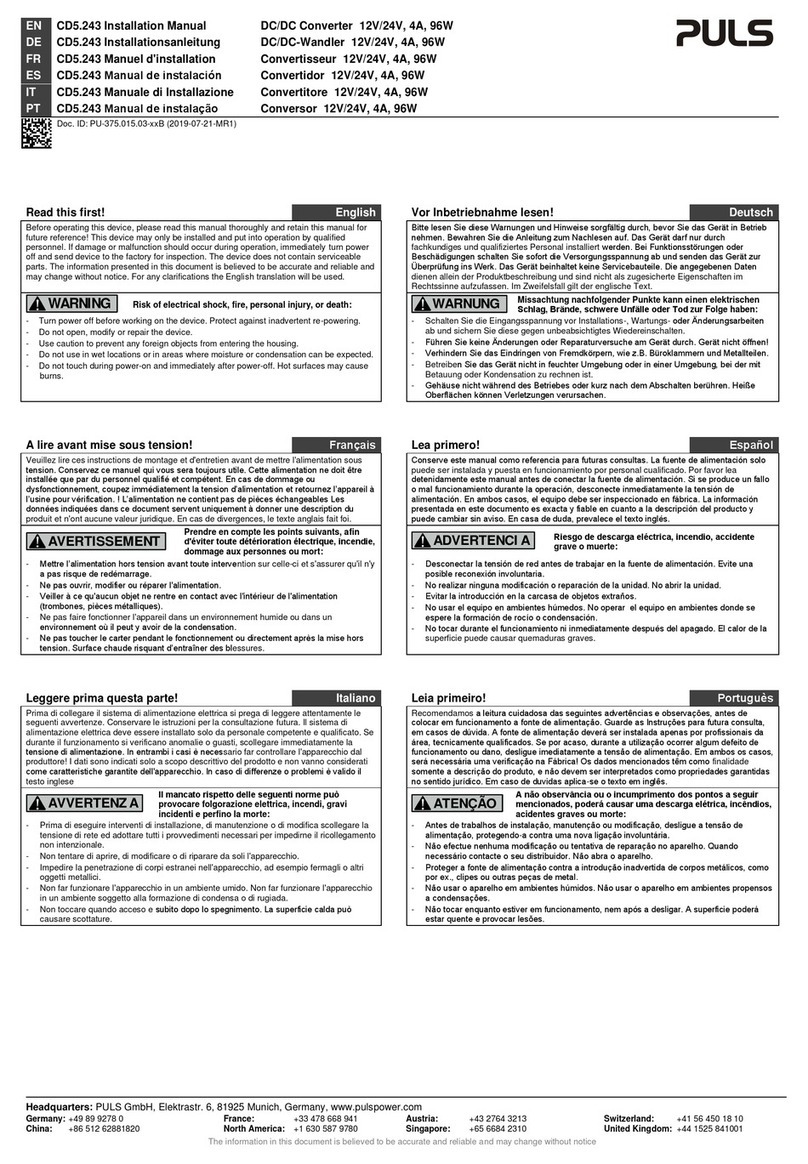

Figure 1

ONNE TION DIAGRAM

M242A 5

CONNECTION AND OPERATION

See figure on previous page.

1. onnect the 64 to its monitor and peripherals (diskette drive) as

instructed by ommodore.

2. Switch off power to the 64, if it is not off already.

3. arefully plug the 242, face up, into the cartridge slot of the 64.

heck that the connector is aligned squarely and fully seated.

The 64 and 242 must rest on a flat surface.

4. onnect the MIDI cables.

Use S I's Model 838 or other MIDI cable. Two of these are

required for most applications. onnect one from MIDI IN of

the 242 to MIDI OUT of your synthesizer or other musical

instrument. onnect the other cable from MIDI OUT of the 242

to MIDI IN of the synth.

5. onnect the footswitch, if desired.

The footswitch may be used to start and stop sequences, and

perform other functions called for by the software. (Use S I's

Model 839.)

6. onnect the external clock, if desired.

The clock input takes a 'A" mono phone plug. Use it for

synchronizing the 64 with another sequencer, drum machine,

or clock signal recorded on tape.

Suppose, for example, that a drum machine lays down a basic

rhythm on track one of a multi-track tape recorder. If the clock

output of the drumbox is recorded on track two at the same

time, the output of track two can then synchronize the 242

during many succesive overdubbing takes.

For more information, refer to your 900 series software

manual.

7. Switch on the system.

Follow the order recommended by ommodore, with the

synthesizer last.

8. Insert the diskette of S I 900 series software

Load and run the software according to the instructions in its

operation manual.

9. If you do not have the software diskette, the PROGRAMMING

section gives a simple BASI program you can use to test your

hardware (see page 12).

M242A 6

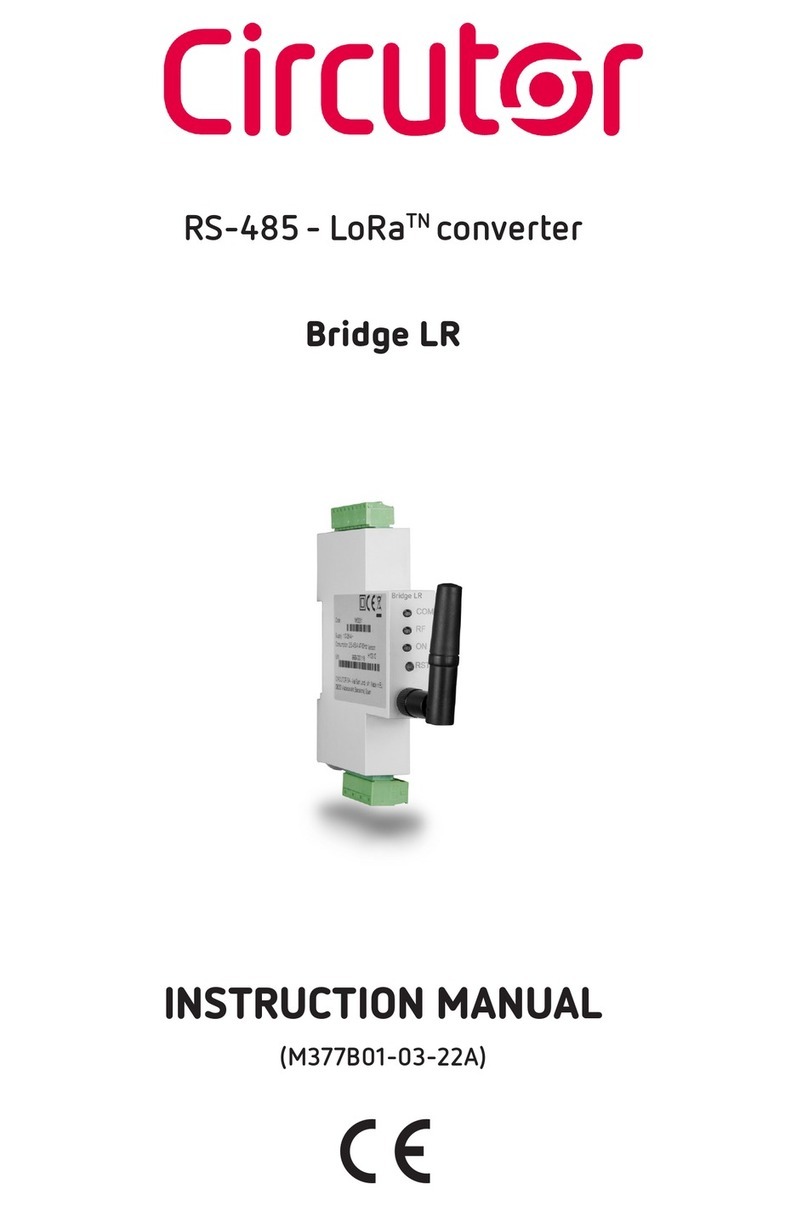

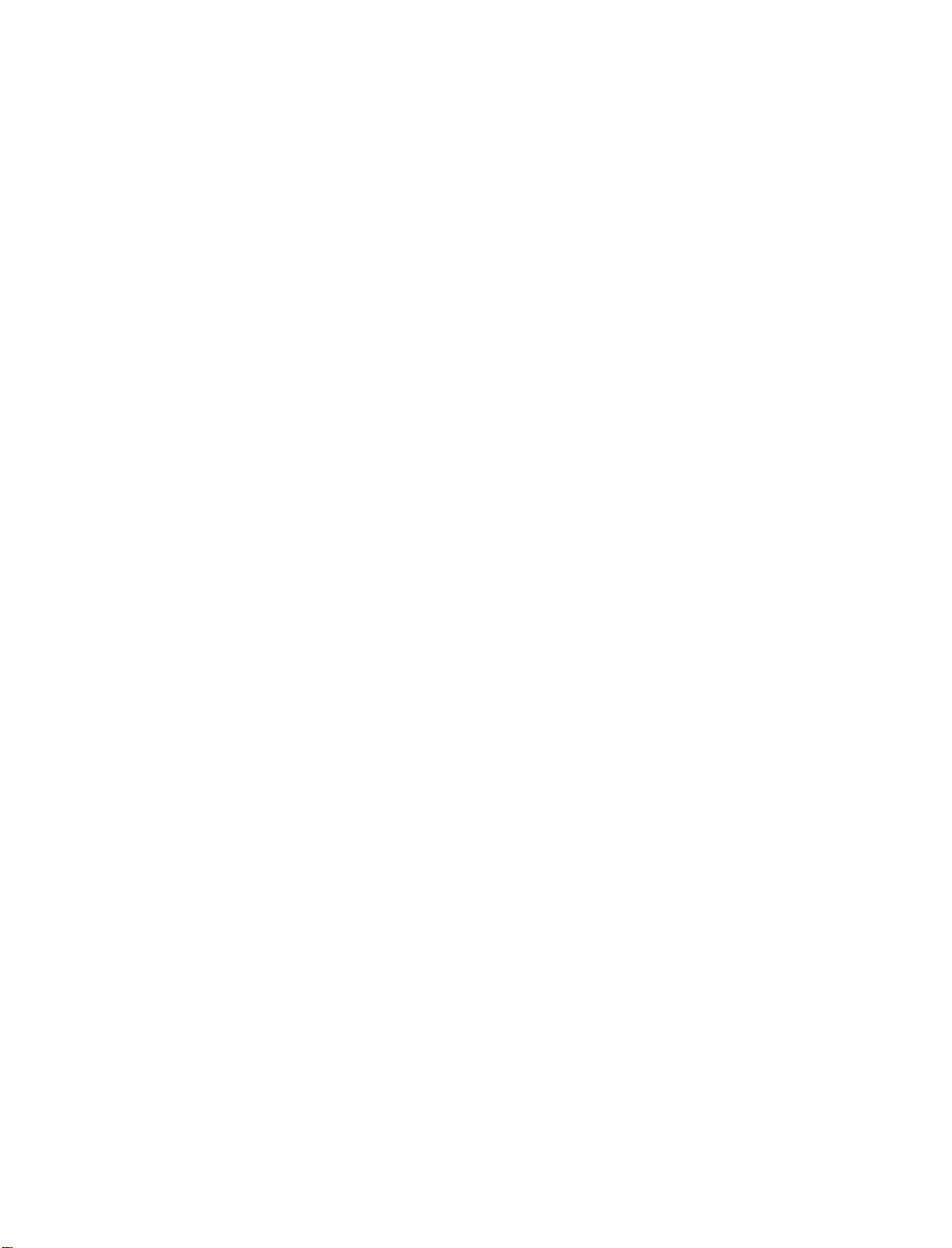

HARDWARE

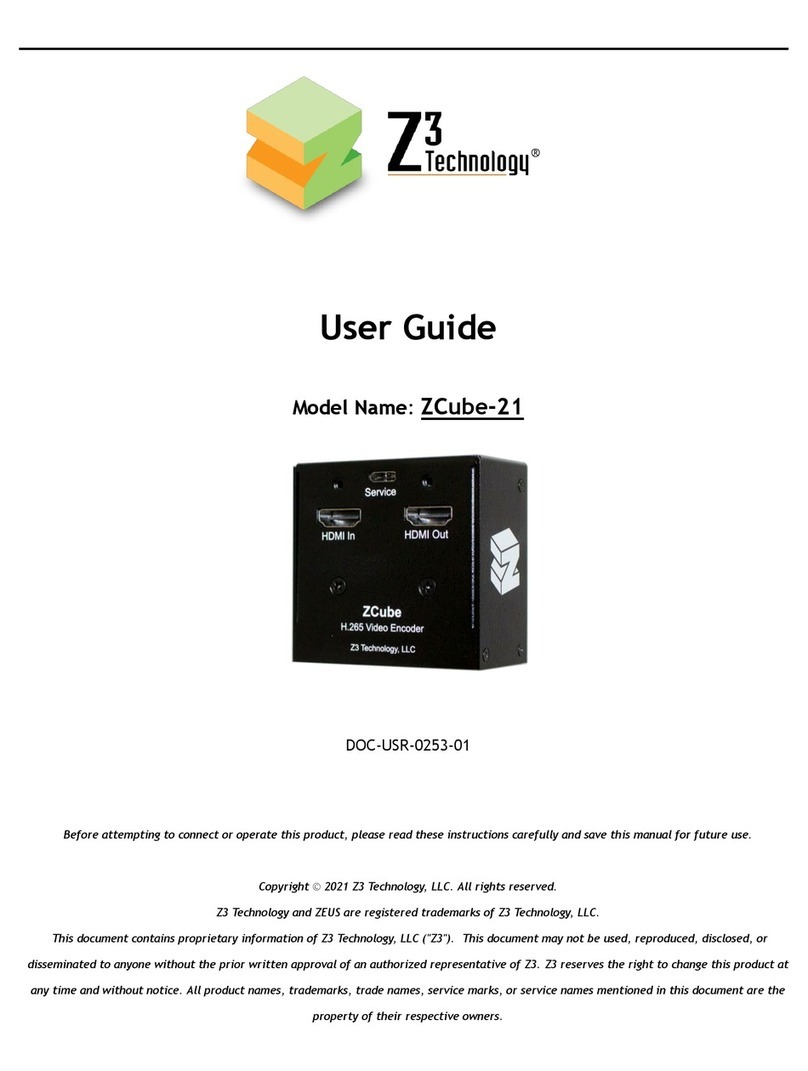

The block diagram of the 242 is shown below. Two main I s are used.

The asynchronous communications interface adaptor (A IA) and its

associated buffer and optoisolator transfer MIDI serial data to and

from the 64 data bus. The parallel interface adaptor (PIA) and

associated circuitry route the footswitch and external clock signals

to the 64. A more detailed discussion of the circuitry follows.

MIDI

IN OPTO

ISOLATOR

BUFFER

-D>-

START/STOP

IN

DRUM CLOCK

IN

SIGNAL

CONDITIONER

SIGNAL

CONDITIONER

PIA ACIA

C64 DATA BUS

CLK

Figure 2

BLOCK DIAGRAM

M242A 7

MIDI

OUT

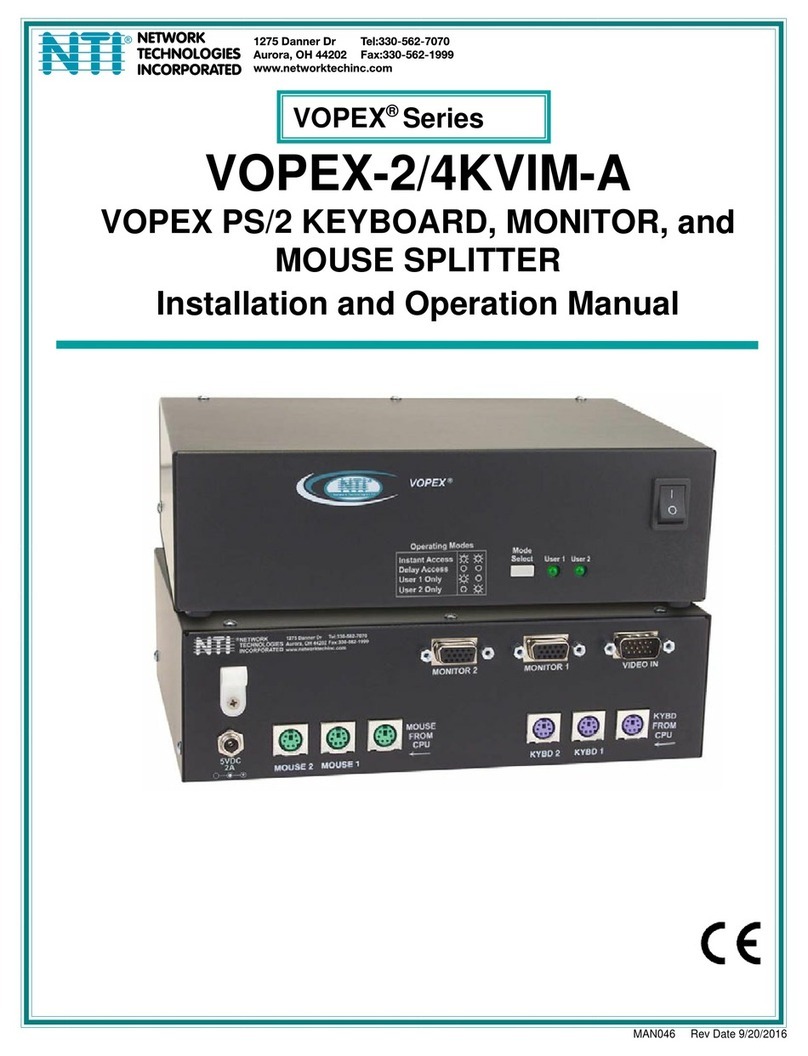

The following annotated parts list describes circuit operation by part

number (integrated circuits first). Refer to the schematic diagram,

SD242-1, on page 9.

DESIG.

U101

U102

U103-9

FUN TION S I PART // DES RIPTION

INTEGRATED CIRCUITS

Optoisolator 1-330 Sharp P -900

The optoisolator electrically isolates the external MIDI

device and the 64/242 system. This is useful for

preventing ground loops, which might cause audio hum and

noise.

When data at pin 5 of MIDI IN is low (0), current flows

over pin 4 and through limiter R101 and UlOl's internal

LED. The LED lights, turning on the phototransistor

between pins 4 and 5, enabling current flow, which pulls

receiver input U105-2 low. When MIDI IN is high (1), no

current flows through R101 and the LED. Thus the

phototransistor turns off, and R114 pulls U105-2 high.

D101 protects the circuit from non-standard or faulty

MIDI drivers.

omparator 1-301 LM311

The comparator squares-up the drum clock input signal to

provide a logic signal for the PIA. Since the LM311 must

operate on supplies of 0 and +5V, a bias network shifts the

input signal so that it is centered between the supplies,

and a comparator reference voltage is provided of the

same value. The 2.5-V bias is generated by voltage divider

R112/R105, filtered by 101, and added to both the signal

path through R106 and to the comparator reference (pin

2) through R107. The incoming signal, meanwhile,

encounters load resistor R109, passes through dc-blocking

capacitor l03, and is offset by the 2.5 Vdc bias, before

going through R108 to the high-impedance inverting input

of the comparator (U102-3).

When the input is positive, output U102-7 is 0V, and when

the input is negative, the output is +5V. R113 is a pull-up

for the open collector output of the LM311. R110 provides

positive feedback for hysteresis to prevent oscillations on

slow input edges. 104 is for comparator stability.

"T" Flip Flop 1-109 74LS74

Divides the approximately 1 MHz 64 clock by two,

supplying U105-3 and U105-4 with the 500 KHz fron

which the 31.25 kBaud data rate is derived (internally).

M 242 A 8

43 2 1

LAW USED DEtETED

C107

0102

R 14-

UOG>

J 101

J4- REL. PER

ECO O-I20

DesCR*f»rio»s» i<bs

DO NOT SCAlE ORAWin6

13l

^ £ O U E r iu A

^ C R O J ia if K 3051 N. FIRST ST.

SAN JOSE.CA. 95134

TITLE

S ME.NV<VT\ . DIA G R A M

-G>4

SIZE DRAWING NO.

D SD242-1 n____Ul

| SHEET 1 OF |

DESIG. FUN TION S I PART // DES RIPTION

U104-6

U104-8

U104-11

U105

Buffer 1-104 74LS08 Quad AND Gate

Serial data output from U105-6 drives U104-4/5 and

appears uninverted at U104-6. When data is low, current

will flow from +5V through R103, the external MIDI

circuit (which should be similar to that described above,

under U101,) and R102. When data is high, no current

flows.

One-shot 1-104 74LS08 Quad AND Gate

When a footswitch contact is made (grounding the bottom

of R104), the resulting high-to-low transition is instantly

coupled through l02 to buffer U104-9/10. The buffer

output triggers the interrupt input of the PIA, U106-18.

102 immediately begins to recharge through R ill, and

in a few milliseconds, U104-9/10 crosses its threshold,

causing U104-8 to again go positive. When the footswitch

is released, 102 is charged through R104. D102 protects

U104 if an active voltage source is connected to the

footswitch input.

Buffer 1-104 74LS08 Quad AND Gate

Buffers the outDut of comparator U102 and applies it to

U106-40.

A IA 1-066 68A50 A IA (Motorola only)

Transfers data bidirectionally between the parallel 64

data bus and the serial MIDI. The data bus is connected to

pins 15-22 of U105. Since chip selects S0 (pin 8) and S1

(pin 10) are tied high (active), the 64 communicates by

pulling down - S2 (pin 9) through decoded chip select

output -I/Ol (address $DEXX). The two lowest address

bits determine function. To read from the A IA, the 64

sets A1 high and to write, brings A1 low. A0 is applied to

RS, pin 11, of the A IA, and when low, selects the control

or status registers; when high, selects the data registers.

The baud rate clock is applied to pins 3 and 4, as discussed

under U103, and the "E" signal, used by the 6500/6800

processor family to synchronize their data transfers,

comes in on pin 14. If so programmed, the A IA

interrupts the 64 by pulling down -IRQ (pin 7) when a

process is complete. MIDI data comes in on 'Rx' (pin 2)

and is sent over 'Tx' (pin 6). Since RS-232 protocols are

not needed, -D D and - TS are tied low, and -RTS is not

connected.

M242A 10

DESIG. FUN TION S I PART it DES RIPTION

U106 PIA 1-064 6520 PIA

The PIA transfers data from the Start/Stop footswitch

and drum lock inputs to the 64 data bus. Pins 26-33

connect to the data bus, SO and S1 are tied high

(active), and the 64 communicates with the PIA by

addressing $DFXX, which puts a low on - S2 (-1/02). The

mode (read or write) is controlled by the 64 R/W line

(pin 21). The internal PIA registers are selected by 64

address lines AO and Al, connected to PIA functions RSO

(pin 36), and RSI (pin 35), respectively.

The 64 reset signal, -RES, applied to pin 34, resets the

PIA at power up, and the 'E' signal (described under Ul05)

comes in on pin 25. Parallel ports A and B are not used

(pins 2-17), nor are interrupt ports A2 (pin 39) and B2

(pin 19.)

The squared and inverted clock signal from the drumbox

comes in A1 (pin 40—from U104-11). If so programmed,

the PIA will interrupt the 64 on the specified transition

of the clock input by pulling down -IRQ A, pin 38,

connected to the non-maskable interrupt input (-NMI), of

the 64. The clock transition also sets a bit in an internal

PIA register, which can be polled by the 64 if interrupts

are not enabled. The Start/Stop pulse, coming in B1 (pin

18) sets a bit in another internal register, which can also

be polled. This input, however, can not be programmed to

interrupt the 64, since -IRQ B (pin 37) is not connected.

101-3

OTHER PARTS

-045 .1 uF 50V

104 -004 100 pF 50V 10%

105-7 -045 .1 uF 50V

D101 D-005 1N914

D102 D-008 1N34

R101-3 R-003 .220

R104 R-025 100K

R105 R-040 22K

R106 R-025 100K

R107-8 R-018 47K

R109 R-040 22K

RllO R-074 510K

R ill R-025 100K

R112 R-040 22K

R113 R-011 4.7K

R114 R-003 220

3101/2 E3-006 PHONE 3A K ABLE

3103/4 E3-005 MIDI 3A K ABLE

M242A 11

PROGRAMMING

This section gives an overview of programming the 242, followed by

examples in BASI and in assembly language. Using the Model 242 is

simply a matter of reading and writing to (in BASI , PEEKing and

POKEing) the several on-chip registers of the 6520 PIA and the 6850

A IA. It should be noted that BASI , because of its slowness cannot

be used for processing MIDI data received from the synth (a MIDI

byte takes only 320 microseconds). BASI can send data to the synth-

-such as musical notes at a very slow tempo, or program dumps, if

you don't mind them taking a long time.

Interrupts

Not only will most applications have to use assembly language for

speed considerations, but interrupts will have to be used as well. The

alternative is polling at least as often as you expect an event to

happen (every 320 microseconds for MIDI receiving). Drum clock

inputs can also happen pretty fast—every few milliseconds. Polling so

often costs a lot in execution time and code space.

Interrupts can benefit MIDI transmitting as well. The alternative,

polling, could here take several different forms. For example, waiting

until the last byte has been sent before sending the next one, or going

off to another task while checking the A IA every 320 microseconds

(or whenever, if you're not too concerned with transmit speed) to see

if it is ready to send another byte.

The A IA interrupt is tied to the maskable interrupt of the 64. It is

beyond the scope of this manual to describe 64 interrupt-handling in

detail, but suffice it to say that the A IA handler must check bits 0

and 1 to determine whether the receiver or transmitter is

interrupting (see next page). If both, the receiver should be handled

first.

A technique that is useful for speeding up the interrupt handlers is

first-in-first-out (FIFO) buffering. In receive, the handler takes the

byte from the A IA, quickly puts it into the FIFO and returns. A

background routine can then unload the FIFO when convenient. In

transmit, the background process that wants to send bytes first

checks that the A IA is ready to transmit a new byte (see page 13).

When it is, the first byte is placed in the A IA transmit data

register, the remaining bytes are put in the FIFO, and the transmit

interrupts are enabled. The transmit interrupt handler, then, takes

the next byte out of the FIFO and loads it into the A IA. When it

takes the last byte, it disables transmit interrupts. Interrupts are

enabled and disabled by loading the ontrol register of the A IA with

the byte found in Table 2.

The PIA interrupt request is connected to the non-maskable interrupt

input of the 64. PIA interrupt enable is selected in conjunction with

the drum clock input polarity (see next page).

M242A 12

Drum Clock Input Options

If you are going to use an external drum clock, you must choose

whether to trigger on the positive (low-to-high) or negative (high-to-

low) transition of the clock. It is recommended that the positive

transition be specified when using the S I Drumtraks. Determine

from Table 1 the mode byte to load into ontrol Register A of the

PIA.

NOTE: The clock polarity given in Table 1 refers to the input to the

242 cartridge (J101), not the input to the PIA itself (U106-40).

Table 1

PIA CONTROL MODES (DRUM CLOCK INPUT)

Transition Interrupts

Positive Disabled

Positive Enabled

Negative Disabled

Negative Enabled

Mode

4

5

6

7

Table 2

ACIA CONTROL MODES

Interrupts

Receive Transmit

Disabled

Enabled

Disabled

Enabled

Disabled

Disabled

Enabled

Enabled

Mode

Decimal Hexadecimal

21

149

53

181

$15

$95

$35

$B5

Table 3

PIA ADDRESSING

Register

lear A

ontrol A

ontrol A

lear B

ontrol B

ontrol B

Read or Write Decimal

Read

Read

Write

Read

Read

Write

57088

57089

57089

57090

57091

57091

Address

Hexadecimal

$DF00

$DF01

$DF01

$DF02

$DF03

$DF03

Table

ACIA ADDRESSING

Register

ontrol Read or Write Decimal

Write 56832

Transmit Data Write 56833

Status Read 56834

Receive Data Read 56835

Address

Hexadecimal

$DE00

$DE01

$DE02

$DE03

M 24 2 A 13

Initialization

Both the A IA and the PIA must be initialized at power-up. The 64

addresses for the registers referred to in the text can be found in

Tables 3 and 4.

Initialize the PIA by first loading the mode byte from Table 1 into

ontrol Register A. Next, since the footswitch hardware does not

invert the signal, and interrupts cannot be used, load a mode byte of

4 into ontrol Register B.

Initialize the A IA by loading its ontrol Register first with a 3

(master reset), then with the mode byte selected from Table 2.

Transmitting MIDI Data

First read the A IA's Status Register to see if it has finished

transmitting the last byte. If the A IA is ready to send another byte,

bit 1 will be high. If 0, you must wait. When ready, load the Transmit

Data Register with the byte to be sent.

Receiving MIDI Data

As in transmitting, first check the A IA's Status Register to see that

a byte has been fully read in. If ready, bit 0 will be high. When the

A IA is ready, check bits 6, 5, and 4 of the Status Register. A high

bit indicates the following error:

Bit 6 Parity error

Bit 5 Overrun error

Bit 4 Framing error

Then read the Receive Data Register. If an error was detected, the

data is not valid, but the read must be done to reset the Status

Register flag bits.

Reading the Footswitch

Read the PIA's ontrol Register B. If a footswitch event has

occurred, bit 7 is high. After detecting an event, reset bit 7 low by

reading from the lear B register. (The data read is meaningless.

The mere action of reading the register resets the bit.)

Reading the Drum Clock Input

If a clock transition of the specified polarity has occurred, bit 7 of

ontrol Register A is high. This should be checked every few

milliseconds when polling, or during the interrupt handler if

interrupts are used. Again, when a clock event is detected, reset bit 7

by reading from the lear A register.

M242A 14

BASIC

Now we will demonstrate these principles using an example in 64

BASI . For real-time use BASI is too slow, but it can be used for

sending simple commands and data to the synthesizer. The following

example can be used to completely check the 242 and the MIDI IN

circuitry of the synthesizer. Unfortunately, since BASI is so slow,

the MIDI OUT circuitry of the synth cannot be checked.

10 REM BASI PROGRAM TO VERIFY PERFORMAN E OF THE

S I MODEL 242.

20 L0=60

30 DELAY=300

50 REM A IA ONSTANTS

60 WOK=2 :REM BIT 1 IS TX EMPTY FLAG

70 ROK=l :REM BIT 0 IS RX BYTE READY FLAG

80 R=56832 :REM ONTROL REGISTER

90 DW= R+1 :REM TRANSMIT DATA REGISTER

100 SR= R+2 :REM STATUS REGISTER

110 DR= R+3 :REM RE EIVE DATA REGISTER

130 REM PIA ONSTANTS

140 RA=57088 :REM LEAR (RESET) A REGISTER

150 A=RA+1 :REM ONTROL REGISTER A

160 RB=RA+2 :REM LEAR (RESET) B REGISTER

170 B=RA+3 :REM ONTROL REGISTER B

180 MD=4

190 REM POSITIVE LO K TRANSITION AND NO INTERRUPTS

FOR BOTH A AND B.

200 REM INITIALIZE PIA

210 POKE A,MD:POKE B,MD

220 REM INITIALIZE A IA

230 POKE R,3 :REM MASTER RESET

240 POKE R,21 :REM SETUP A IA FOR 1 START, 8

DATA AND 1 STOP

250 :REM BITS, 31.25 KBAUD DATA RATE,

255 :REM AND NO INTERRUPTS

260 REM 242 MIDI TEST

265 PRINT "TURN OFF SYNTH POWER, IF NOT OFF ALREADY"

268 PRINTrPRINT

270 PRINT "TO TEST THE 242, PLUG IT IN TO ITSELF:"

280 PRINT " ONNE T MIDI OUT TO MIDI IN"

290 PRINT "THEN HIT A T "

300 PRINT:PRINT "TO SKIP THIS TEST, HIT ANY OTHER"

301 PRINT " HARA TER."

310 GET A$ : IF A$="" THEN 310

320 IF A$="T" THEN GOSUB 2000

330 REM EXE UTE AN UPWARD GLISSANDO WITH EVER-

DE REASING NOTE DURATIONS

M242A 15

332 PRINTsPRINT "NOW ONNE T THE 242'S MIDI OUT "

333 PRINT "TO MIDI IN OF THE SYNTH,"

334 PRINT "TURN SYNTH POWER ON,"

335 PRINT "AND WHEN THE SYNTH IS READY,"

337 PRINT "HIT ANY HARA TER."

338 PRINT " YOU SHOULD HEAR A GLISSANDO."

339 GET A$ : IF A$="" THEN 339

340 WAIT SR,WOK :REM TRANSMIT READY?

350 POKE DW,144 :REM IF SO, THEN SEND MIDI NOTE

ON

360 REM USE RUNNING STATUS AND VELO ITY BYTE ODING

OF NOTE ON OR OFF.

380 DD=DELAY

390 FOR NN=LO TO LO+36

400 WAIT SR,WOK REM

410 POKE DW,NN REM

420 WAIT SR,WOK REM

430 POKE DW,64 REM

NOTE ON

440 GOSUB 1000 REM

450 WAIT SR,WOK REM

460 POKE DW,NN REM

470 WAIT SR,WOK REM

480 POKE DW,0 REM

490 NEXT

TRANSMIT READY?

SEND OUT NOTE NUMBER

TRANSMIT READY?

NON-ZERO VELO ITY FOR

DELAY FOR NOTE SUSTAIN

TRANSMIT READY?

NOTE NUMBER AGAIN

TRANSMIT READY?

ZERO VELO ITY FOR NOTE OFF

500 REM NOW A SIMILAR DOWNWARD GLISS

510 DD=DELAY

520 FOR NN=LO+36 TO LO STEP -1

530 WAIT SR,WOK REM

540 POKE DW,NN REM

550 WAIT SR,WOK REM

560 POKE DW,64 REM

NOTE ON

570 GOSUB 1000 REM

580 WAIT SR,WOK REM

590 POKE DW,NN REM

600 WAIT SR,WOK REM

610 POKE DW,0 REM

620 NEXT

630 PRINT "THANK YOU"

TRANSMIT READY?

SEND OUT NOTE NUMBER

TRANSMIT READY?

NON-ZERO VELO ITY FOR

DELAY FOR NOTE SUSTAIN

TRANSMIT READY?

NOTE NUMBER AGAIN

TRANSMIT READY?

ZERO VELO ITY FOR NOTE OFF

640 REM TEST FOOTSWIT H

650 PRINT "TO TEST THE FOOTSWIT H, STEP ON IT AND "

660 PRINT "WAT H THE S REEN FOR THE MESSAGE "

670 PRINT "'FOOTSWIT H A TIVATED"':PRINT

680 PRINT "HIT ANY HARA TER TO END THE TEST"

690 A=PEEK (RB) :REM LEAR INTERRUPT FLAG

BEFORE STARTING

700 IF (PEEK( B)AND 128)=0 THEN 730

710 PRINT "FOOTSWIT H A TIVATED"

720 A=PEEK (RB) :REM LEAR FLAG AFTER RE EIVING

730 GET A$:IF A$="" THEN 700

740 PRINT:PRINT:PRINT "THANK YOU"

M242A 16

760 REM LO K INPUT TEST

770 PRINT " LO K INPUT TEST"

780 PRINT "A MESSAGE WILL BE PRINTED ON THE S REEN "

790 PRINT "WHEN A LO K SIGNAL IS RE EIVED."

800 PRINT : PRINT "HIT ANY KEY TO END TEST"

810 PRINT : PRINT "START DRUMBOX..."

820 A=PEEK (RA) :REM LEAR INTERRUPT FLAG

BEFORE STARTING

830 IF (PEEK( A)AND 128)=0 THEN 860

840 PRINT " LO K SIGNAL RE EIVED"

850 A-PEEK (RA) :REM LEAR FLAG AFTER RE EIVING

860 GET A$:IF A$="" THEN 830

870 PRINT:PRINT:PRINT "THANK YOU"

880 PRINT:PRINT:PRINT "THANK YOU"

890 PRINT:PRINT:PRINT "THANK YOU"

900 PRINT "END"

910 END

997 REM SUBROUTINE DELAY

998 REM PRODU ES A DELAY WHI H IS SMALLER EA H TIME

IT IS ALLED

999 REM UNLESS THE "DD" VARIABLE IS RESET EXTERNALLY

1000 FOR N=INT(DD) TO 0 STEP -1

1010 NEXT

1020 DD=DD/2 4(1/6)

1030 RETURN

1040 END

1990 REM SUBROUTINE TEST 242 MIDI HARDWARE

2000 PRINT "IF TEST NOT DONE IN 8 SE ONDS,"

2001 PRINT "HIT RUN/STOP RESTORE TO STOP PROGRAM,"

2002 PRINT "THEN HE K THE MIDI ABLE."

2003 PRINT:PRINT

2005 FOR A=0 TO 255

2010 WAIT SR,WOK :REM WAIT FOR TX EMPTY

2020 POKE DW,A :REM SEND THIS BYTE

2030 WAIT SR,ROK :REM WAIT FOR RE EIVED BYTE

2035 IF (PEEK(SR)AND 112)=0 THEN 2040 :REM HE K

ERROR FLAGS (BITS 4,5,<5c6.)

2038 PRINT "*****FLAG*****":GOTO 2050

2040 IF PEEK(DR)=A THEN 2060 :REM READ AND TEST RE EIVED

BYTE

2050 PRINT "******£RROR******"

2055 STOP

2060 NEXT

2070 PRINT "242 MIDI HARDWARE HE KS OK"

2080 RETURN

2090 END

M242A 17

PROGRAMMING IN ASSEMBLY LANGUAGE

The following code segments illustrate the programming principles

described above. (To run them on the 64, you need an assembler and

debugger.)

1. To initialize the A IA for MIDI:

;Master reset

LDA #$03

STA $DE00

LDA //$15

STA $DE00 ;Setup for 1 start bit+8 bits+1 stop bit

; and 31.25 kBaud

2. To send MIDI OUT:

LOOP LDA $DE02

AND #$02

BEQ LOOP

LDA MIDIBYTE

STA $DE01

;Read A IA status register

; heck transmit empty flag

;Loop until empty

;Load in byte to send

;Send MIDI OUT

3. To receive MIDI IN:

LOOP LDA $DE02

LSR

B LOOP

LDA $DE03

;Read A IA status register

; heck receive full flag

;Loop until ready

;Read MIDI IN

k. To initialize the PIA:

LDA MODE

STA $DF01

STA $DF03

;Use control registers to set up

;operating mode.

;Obtain mode from Table 1

5. To read drum clock input:

LDA $DF01

BPL EXIT

LDA $DF00

;Read control register

;8ranch if no drum clock yet

;Falls thru if interrupted by drum clock

; lear the interrupt flag bit

6. To read footswitch input:

LDA $DF03 ;Read control register

BPL EXIT

LDA $DF02 ;Branch if no footswitch press

; lear interrupt flag

M242A 18

Table of contents