2

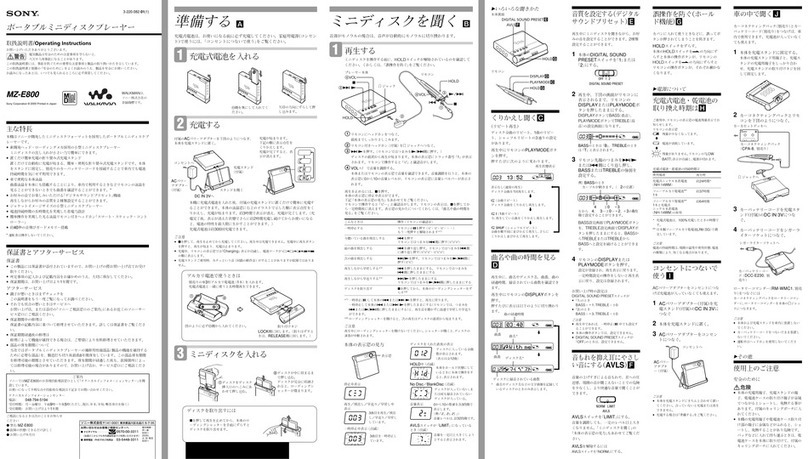

laser-tap

SAFETY-RELATED COMPONENT WARNING!!

COMPONENTS IDENTIFIED BY MARK 0OR DOTTED LINE

WITH MARK 0ON THE SCHEMATIC DIAGRAMS AND IN

THE PARTS LIST ARE CRITICAL TO SAFE OPERATION.

REPLACE THESE COMPONENTS WITH SONY PARTS WHOSE

PART NUMBERS APPEAR AS SHOWN IN THIS MANUAL OR

IN SUPPLEMENTS PUBLISHED BY SONY.

ATTENTION AU COMPOSANT AYANT RAPPORT

À LA SÉCURITÉ!!

LES COMPOSANTS IDENTIFIÉS PAR UNE MARQUE 0SUR LES

DIAGRAMMES SCHÉMATIQUES ET LA LISTE DES PIÈCES

SONT CRITIQUES POUR LA SÉCURITÉ DE FONCTIONNEMENT.

NE REMPLACER CES COMPOSANTS QUE PAR DES PIÈCES

SONY DONT LES NUMÉROS SONT DONNÉS DANS CE MANUEL

OU DANS LES SUPPLÉMENTS PUBLIÉS PAR SONY.

Notes on Chip Component Replacement

•Never reuse a disconnected chip component.

•Notice that the minus side of a tantalum capacitor may be dam-

aged by heat.

CAUTION

Use of controls or adjustments or performance of procedures

other than those specified herein may result in hazardous ra-

diation exposure.

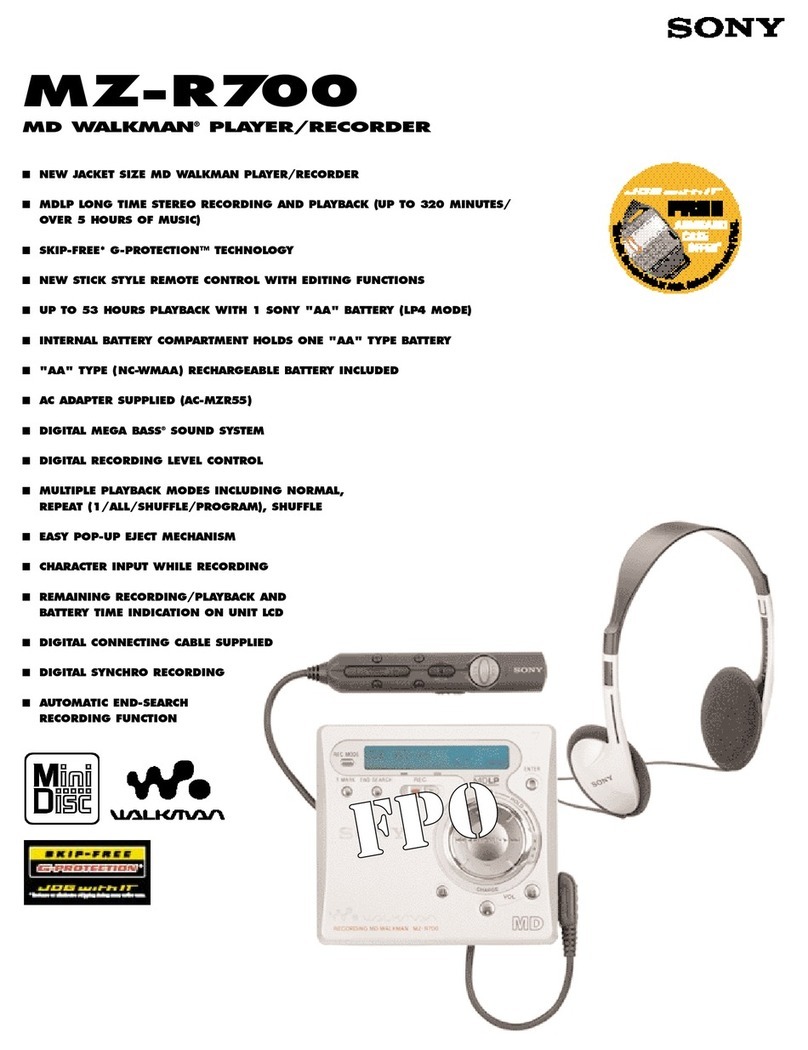

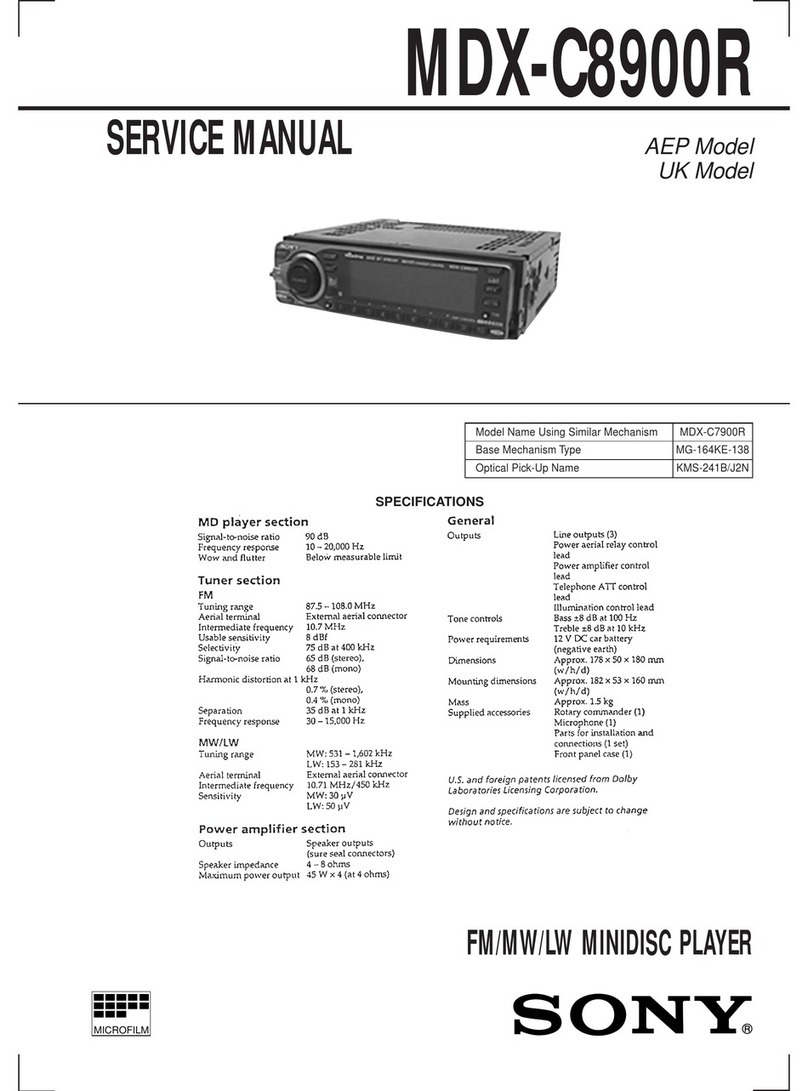

Power amplifier section

Outputs Speaker outputs

(sure seal connectors)

Speaker impedance 4 – 8 ohms

Maximum power output 50 W ×4 (at 4 ohms)

General

Outputs Audio outputs

Power antenna relay

control lead

Power amplifier control

lead

Telephone ATT control

lead

Tone controls Bass ±9 dB at 100 Hz

Treble ±9 dB at 10 kHz

Power requirements 12 V DC car battery

(negative ground)

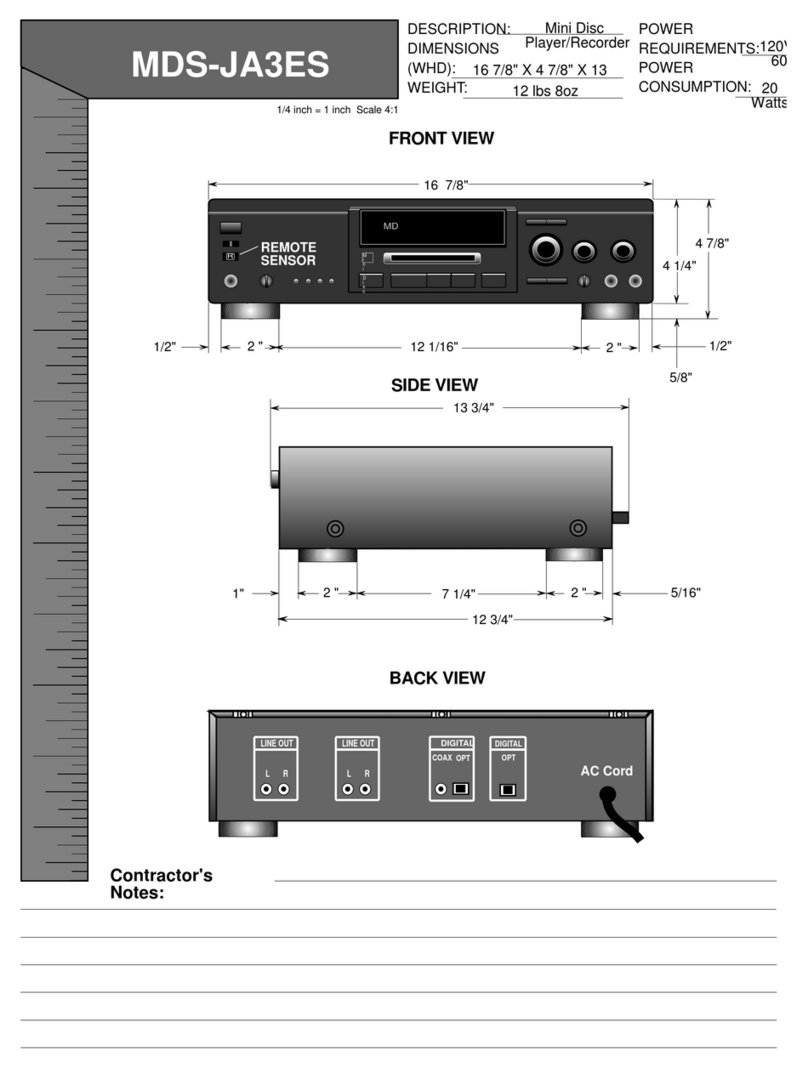

Dimensions Approx. 178 ×50 ×183 mm

(7 1/8 ×2 ×7 1/4 in.)

(w/h/d)

Mounting dimensions Approx. 182 ×53 ×162 mm

(7 1/4 ×2 1/8 ×6 1/2 in.)

(w/h/d)

Mass Approx. 1.2 kg (2 lb. 10 oz.)

Supplied accessories Parts for installation and

connections (1 set)

Front panel case (1)

Design and specifications are subject to change without

notice.

Flexible Circuit Board Repairing

• Keep the temperature of the soldering iron around 270 ˚C dur-

ing repairing.

• Do not touch the soldering iron on the same conductor of the

circuit board (within 3 times).

• Be careful not to apply force on the conductor when soldering

or unsoldering.

The laser diode in the optical pick-up block may suffer electrostatic

break-down because of the potential difference generated by the

charged electrostatic load, etc. on clothing and the human body.

During repair, pay attention to electrostatic break-down and also

use the procedure in the printed matter which is included in the

repair parts.

The flexible board is easily damaged and should be handled with

care.

NOTES ON LASER DIODE EMISSION CHECK

Never look into the laser diode emission from right avove when

checking it for adustment. It is feared that you will lose your sight.

NOTES ON HANDLING THE OPTICAL PICK-UP BLOCK

(KMS-241C/J1NP)

The laser diode in the optical pick-up block may suffer electrostatic

break-down easily. When handling it, perform soldering bridge to

the laser-tap on the flexible board. Also perform m easures against

electrostatic break-down sufficiently before the operation. The flex-

ible board is easily damaged and should be handled with care.

OPTICAL PICK-UP FLEXIBLE BOARD

NOTES ON HANDLING THE OPTICAL PICK-UP

BLOCK OR BASE UNIT