ST STM32F103 series Installation and operating instructions

Other ST Microcontroller manuals

ST

ST STM32F410 User manual

ST

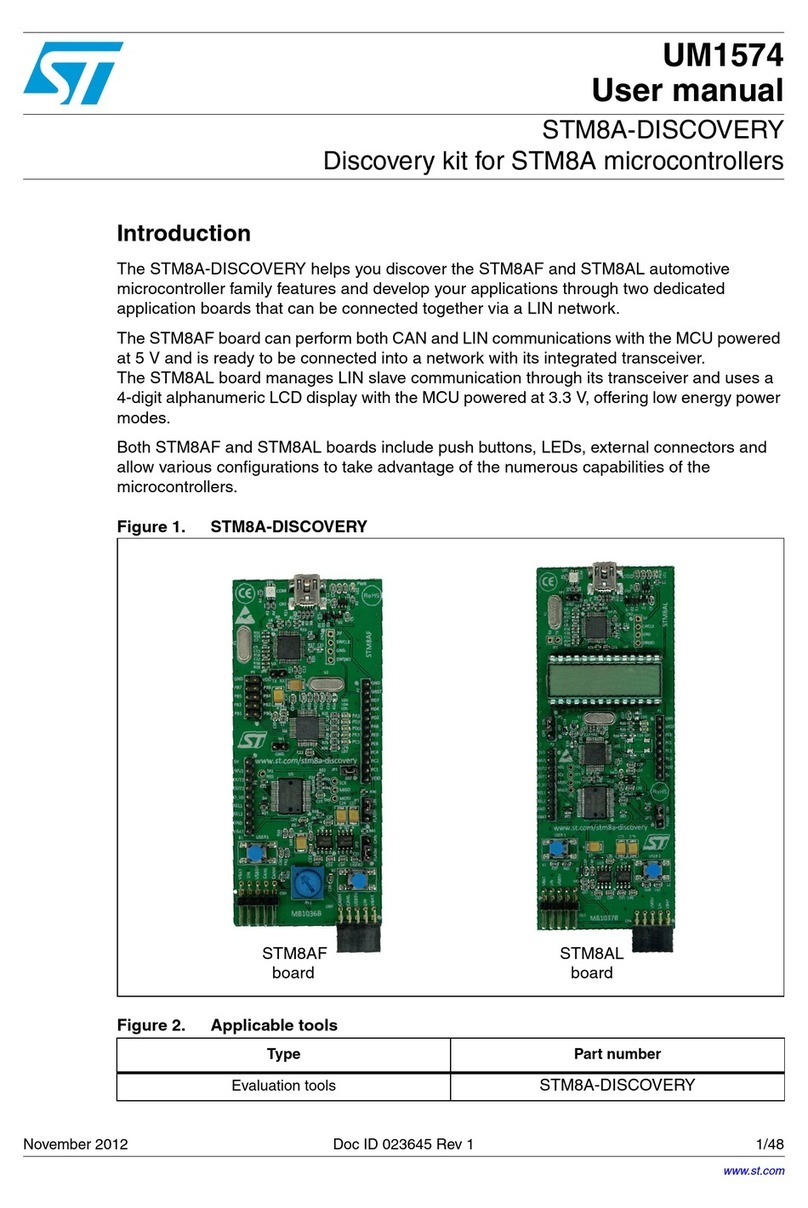

ST STM8A-DISCOVERY User manual

ST

ST STM32F446 Series User manual

ST

ST UC2842B User manual

ST

ST ST25DV-I2C User manual

ST

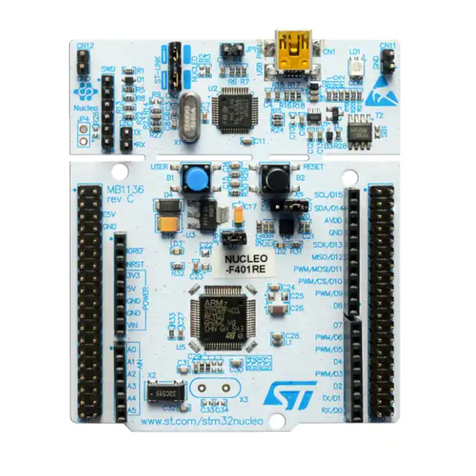

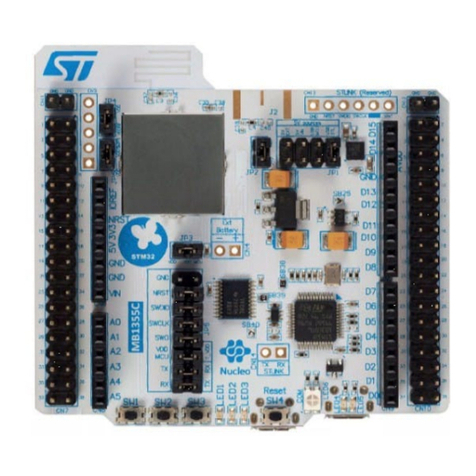

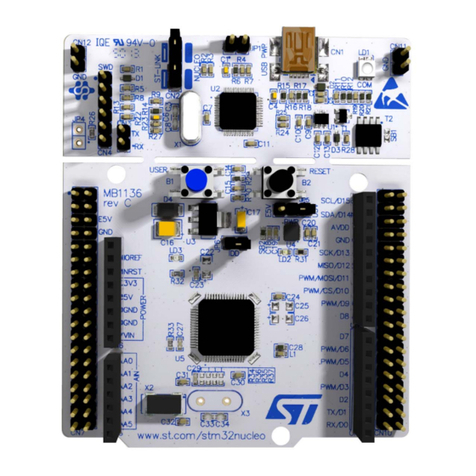

ST STM32 Nucleo Installation and operating instructions

ST

ST ST7LITE1 B Series User manual

ST

ST STM8S User manual

ST

ST STM32L053 User manual

ST

ST STM32L4 5 Series User manual

ST

ST STEVAL-FKI433V1 User manual

ST

ST STM32L1 Series Installation and operating instructions

ST

ST STM32 Series Installation and operating instructions

ST

ST Turbo uPSD DK3300-ELCD User manual

ST

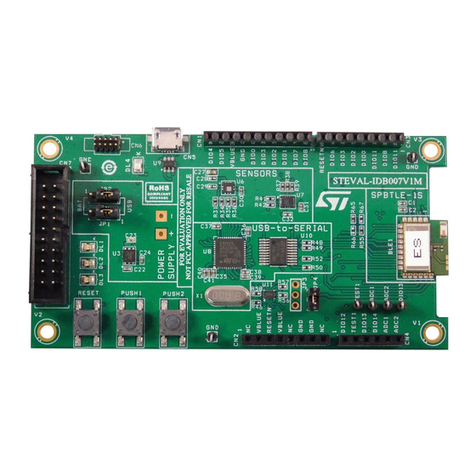

ST STEVAL-IDB007V1M SPBTLE-1S User manual

ST

ST STM32F20 Series Installation and operating instructions

ST

ST STM32 Nucleo User manual

ST

ST STEVAL-2STPD01 User manual

ST

ST STM32F7308-DK User manual

ST

ST STM32F101xx series User manual

Popular Microcontroller manuals by other brands

AMS

AMS AS7261 Demo Kit user guide

Novatek

Novatek NT6861 manual

Espressif Systems

Espressif Systems ESP8266 SDK AT Instruction Set

Nuvoton

Nuvoton ISD61S00 ChipCorder Design guide

STMicrolectronics

STMicrolectronics ST7 Assembler Linker user manual

Texas Instruments

Texas Instruments Chipcon CC2420DK user manual

Texas Instruments

Texas Instruments TMS320F2837 D Series Workshop Guide and Lab Manual

CYPRES

CYPRES CY14NVSRAMKIT-001 user guide

Texas Instruments

Texas Instruments INA-DUAL-2AMP-EVM user guide

Espressif Systems

Espressif Systems ESP8266EX Programming guide

Abov

Abov AC33M8128L user manual

Laird

Laird BL654PA user guide