492/492P Service Vol. I (SN B030000 & up)

LIST OF ILLUSTRATIONS (cont)

Fig. Page

No.

3-43 Response of the 100 kHz filter

.................. 3-65

3-44 Calibration adjust ents on the VR #1

odule....................................................... 3-65

3-45 Typical response of 10 kHz, 100 kHz, and

1 MHz bandwidth filters

...........................

3-67

3-46 Test equip ent setup for adjusting IF gain

and the location of the calibrator level

adjust ent

................................................. 3-68

3-47A Digital Storage adjust ent

locations SN B043115 and above

..........

3-70

3-47 Digital Storage adjust ents

SN B043114 and below .......................... 3-70

3-48 Location of binary switch (S1014) for

setting B —SAVE A reference level

............

3-71

3-49 Band leveling adjust ents and gain diodes

(when installed) on VR #2 odule

............

3-72

3-50 Test equip ent setup for calibrating band

leveling of the external ixer bands

..........

3-73

3-51 Test equip ent setup for calibrating

Preselector Driver

.....................................

3-74

3-52 Preselector Driver adjust ents and test

points......................................................... 3-74

3-53 Test equip ent setupo for calibrating

Phaselock asse bly

.................................

3-76

3-54 Adjust ents and test point locations in the

Phaselock odule

.....................................

3-77

4-1 Multipin (har onica) connector

configuration

............................................. 4-4

4-2 Color code for so e tantalu capacitors. . 4-4

4-3 Diode polarity arkings............................ 4-5

4-4 Electrode configuration for se iconductor

co ponents

............................................... 4-6

4-5 Preparing the VR odule for service

showing how it is supported when on an

extender................................................... 4-9

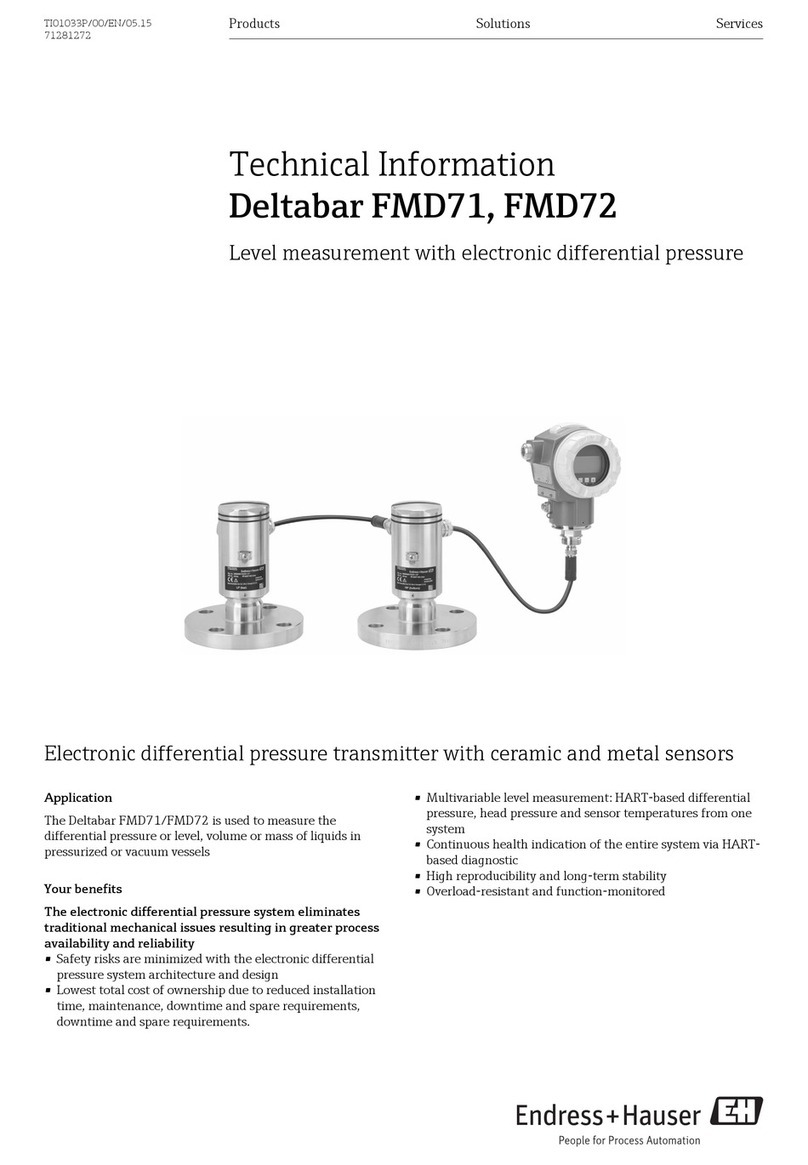

4-6 RF deck of B040000 and up version

showing ajor ase blies.......................... 4-11

4-6A View of the 492/492P RF deck for

B039999 and below showing ajor

asse blies

and circuit boards

.....................................

4-12

4-7 View of the 492/492P top deck showing

ajor asse blies

.......................................

4-13

4-8 Re oving YIG oscillator interface circuit

board......................................................... 4-16

4-9 Fan Asse bly

...........................................

4-18

4-10 Test equip ent setup for adjusting return

loss for the 110 MHz IF asse bly

............

4-20

4-11 Location of the 110 MHz IF return loss

adjust ents and IF Gain adjust ent

........

4-20

Fig. Page

N o .

4-12 LO section of 829 MHz converter showing

test points and connectors ........................ 4-22

4-13 Location of test jack and ju per on the

829 MHz a plifier board

...........................

4-23

4-14 Test equip ent setup for aligning the

829 MHz filter

........................................... 4-24

4-15 Filter tune tabs in the 829 MHz converter . 4-25

4-16 Typical response when the first and

second resonators of the 829 MHz filter

are adjusted correctly

...............................

4-26

4-17 Typical response when the third and fourth

resonators are tuned correctly

.................. 4-26

4-18 Test equip ent setup for calibrating

the oscillator section of the

2182 MHz Phaselocked 2nd L O

................

4-28

4-19 Adjust ents and test point locations

within the oscillator section........................ 4-29

4-20 Construction of a coaxial test probe

for the 2182 MHz Phaselocked 2nd LO ... 4-30

4-21 Test equip ent setup for calibrating

the phaselocked section of the

2182 MHz Phaselocked 2nd L O

................

4-31

4-22 Location of test points and co ponents

associated with calibrating the

14-22 MHz Phaselock circuit .................... 4-32

4-23 Ju per positions between T1077

and T1075 versus frequency

co pensation for the 14-22 MHz

Oscillator ................................................... 4-33

4-24 The Me ory board option switch band

S1033 ....................................................... 4-36

4-25 A15 through A12 in icroco puter test

ode ......................................................... 4-38

4-26 A15 and Y0 through Y2 of address decoder

U2044 ....................................................... 4-38

4-27 Enable and Y0 through Y2 of address de

coder U1037B

........................................... 4-39

4-28 A15 and Me ory board address decoder

outputs ..................................................... 4-40

4-29 A15 and Y0 through Y2 of address decoder

U1021 on the GPIB board ........................ 4-41

4-30 One enable and outputs LORAM, HIRAM,

and GPS of address decoder U1028 on the

GPIB board

............................................... 4-41

4-31 Instru ent bus check

...............................

4-41

5-1 Filter cross-section view ............................ 5-8

5-2 Filter equivalent circuit

...............................

5-9

5-3 2182.0 MHz Cavity LO equivalent circuits . 5-13

5-4 Diplexer si plified sche atic .................... 5-14

5-5 A plifier signal path

.................................

5-15

5-6 A plifier signal path

.................................

5-15

REV SEP 1983 vii