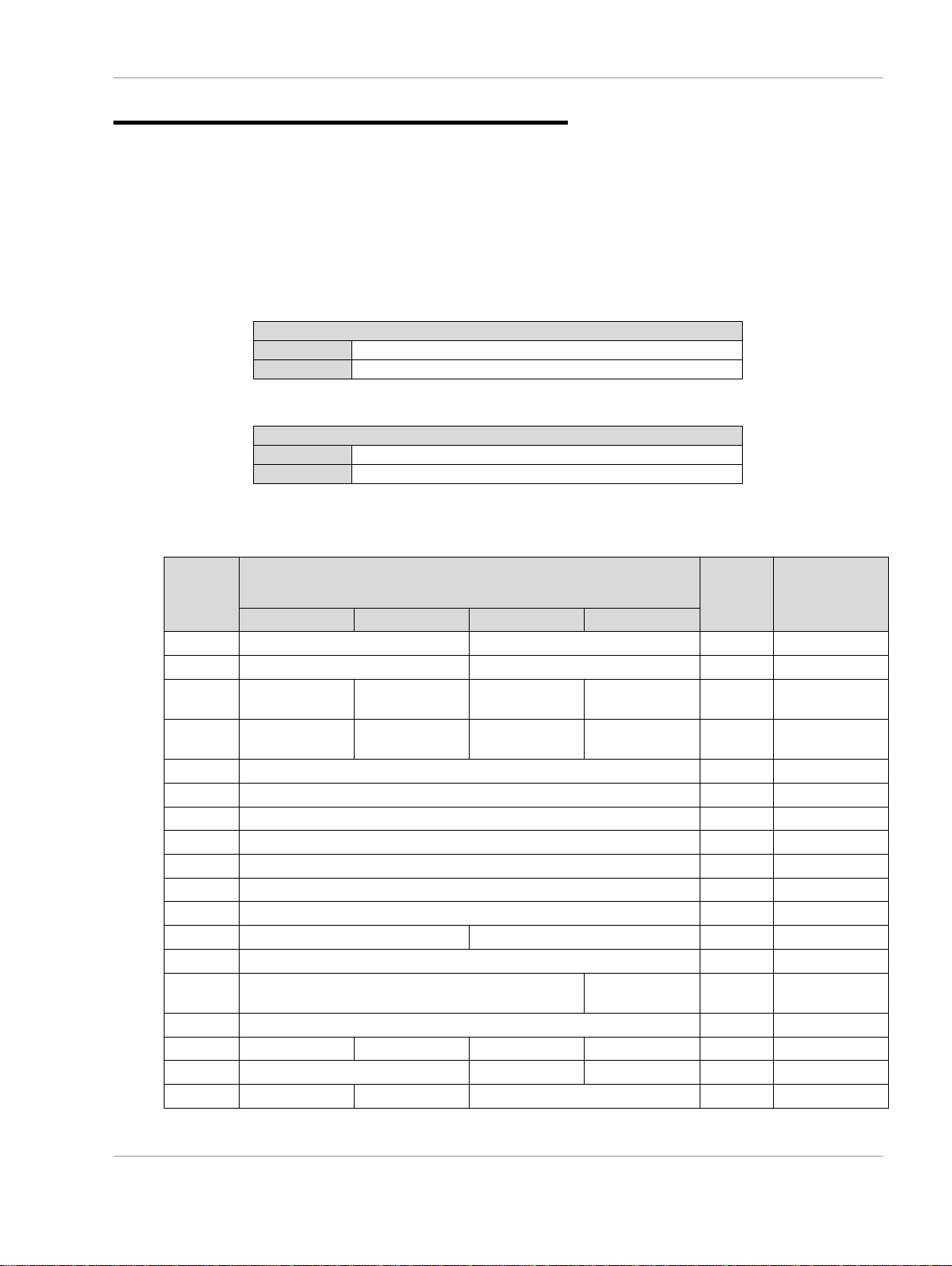

3 10 Gigabit Ethernet Controller

PCI Bus Topology3.1

The Intel X540 10 Gigabit Ethernet Controller is represented by a multifunctional device on the PCI bus. The

two different Ethernet Channels can be identified by the corresponding function of the device.

Multifunctional device (Intel Corporation)

Bus : Device : Function 0x00

0x8086 (Intel Corporation)

0x1528 (Ethernet Controller 10-Gigabit X540-AT2

Bus : Device : Function 0x01

0x8086 (Intel Corporation)

0x1528 (Ethernet Controller 10-Gigabit X540-AT2

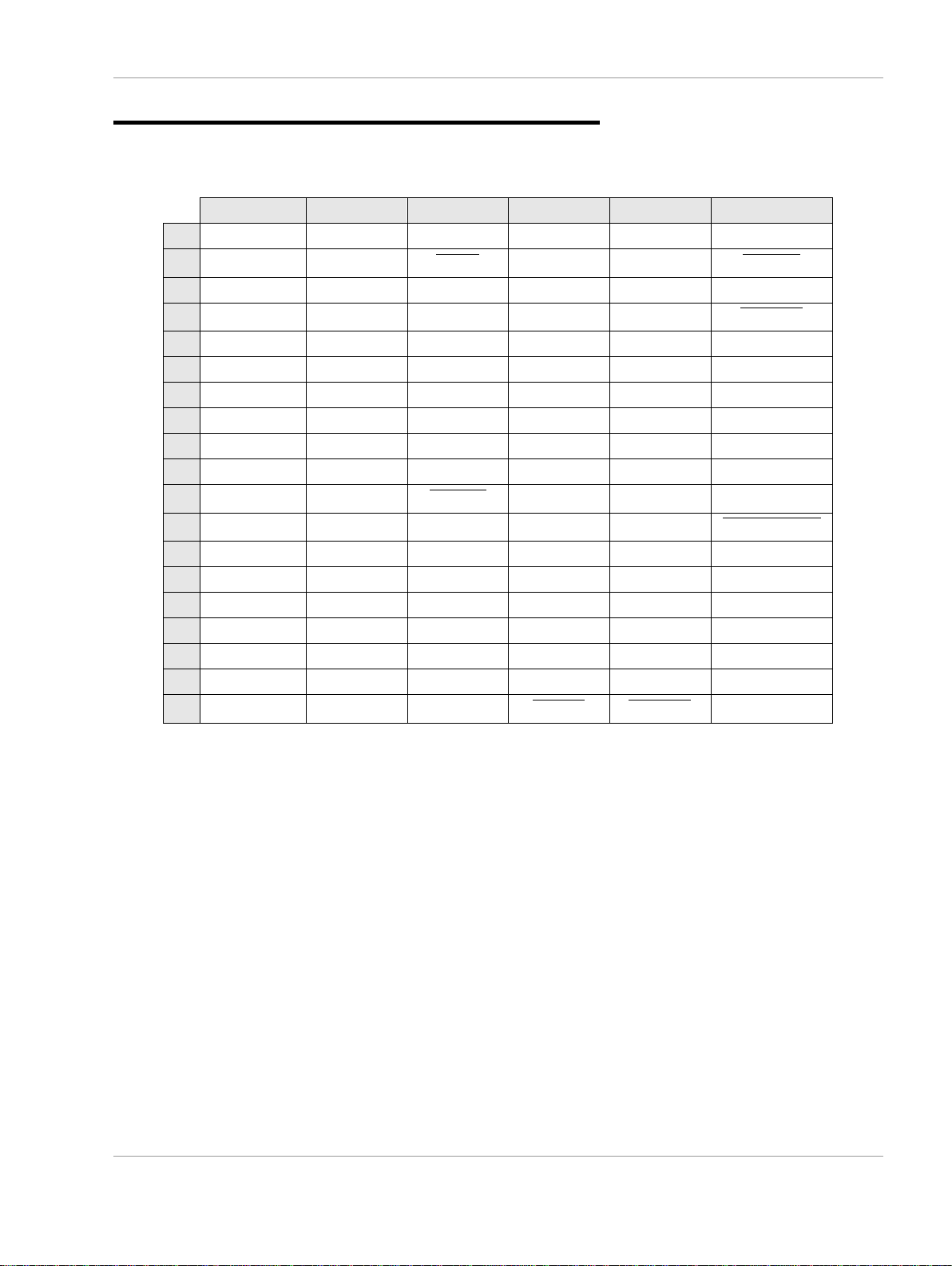

Intel X540 Function PCI Header3.2

PCI CFG

Register

Address

Write ‘0’ to all unused (Reserved) bits PCI

writeable

Initial Values

(Hex Values)

0x00 Device ID Vendor ID N 1528 8086

0x04 Status Register Command Register Y 0010 0406

0x08 Class Code Subclass Programming

Interface Revision ID Y[7:0] 02 00 00 10

0x0C BIST Header Type Latency Timer Cache Line

Size Y[7:0] 00 80 00 10

0x10 Base Address Register 0 Y F000000C

0x14 Base Address Register 1 Y 00000000

0x18 Base Address Register 2 Y 00000000

0x1C Base Address Register 3 Y 00000000

0x20 Base Address Register 4 Y F040000C

0x24 Base Address Register 5 Y 00000000

0x28 CardBus CIS N 00000000

0x2C Subsystem Device ID Subsystem Vendor ID N 0001 8086

0x30 Expansion ROM Y 00000000

0x34 Reserved Capabilities

Pointer N 000000 40

0x38 Reserved N 00000000

0x3C Max_Lat Min_Gnt Interrupt Pin Interrupt Line Y[7:0] 00 00 01/02 00

0x40 PMC Next_Item_Ptr Cap_ID N 4823 50 01

0x44 Data Register PMCSR_BSE PMCSR Y 00 00 1E00

Table 3-1 : Intel X540 PCI Header

TXMC387 User Manual Issue 1.0.0 Page 8 of 12