Texas Instruments TMS320C6000 DSP User manual

Other Texas Instruments Computer Hardware manuals

Texas Instruments

Texas Instruments TI TestGuard 4.0 Manual

Texas Instruments

Texas Instruments INA149 User manual

Texas Instruments

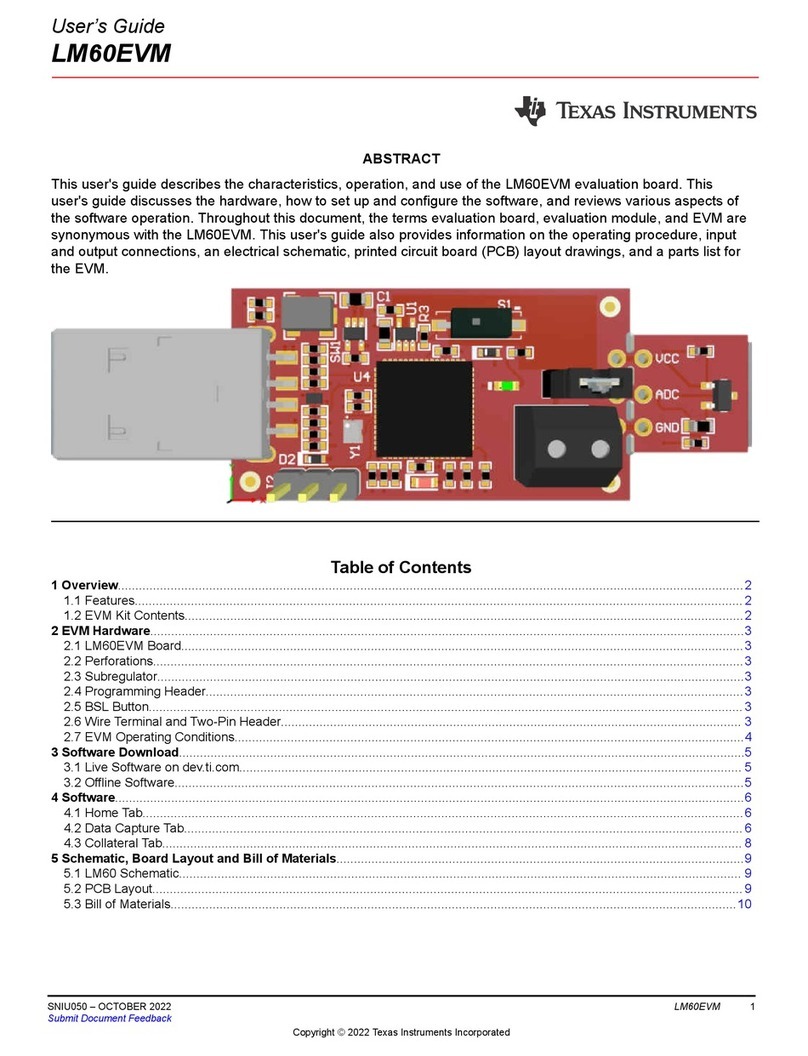

Texas Instruments LM60EVM User manual

Texas Instruments

Texas Instruments MCT8317 User manual

Texas Instruments

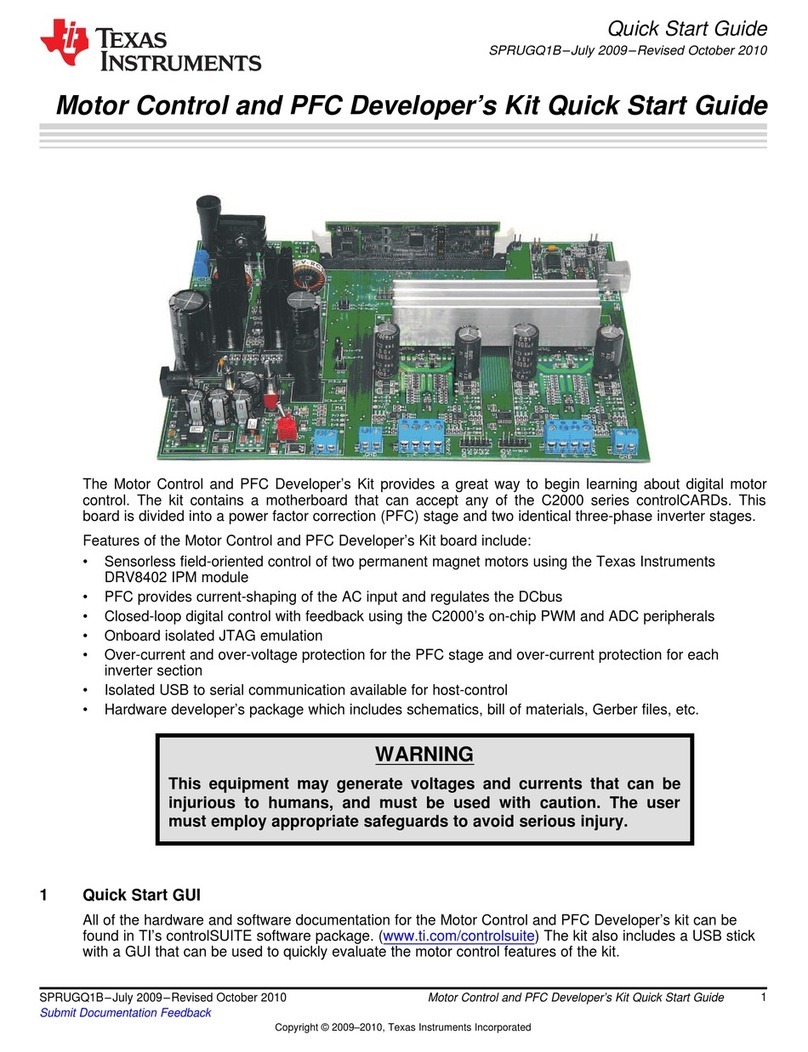

Texas Instruments Motor Control User manual

Texas Instruments

Texas Instruments TMS320VC5509 Installation and user guide

Texas Instruments

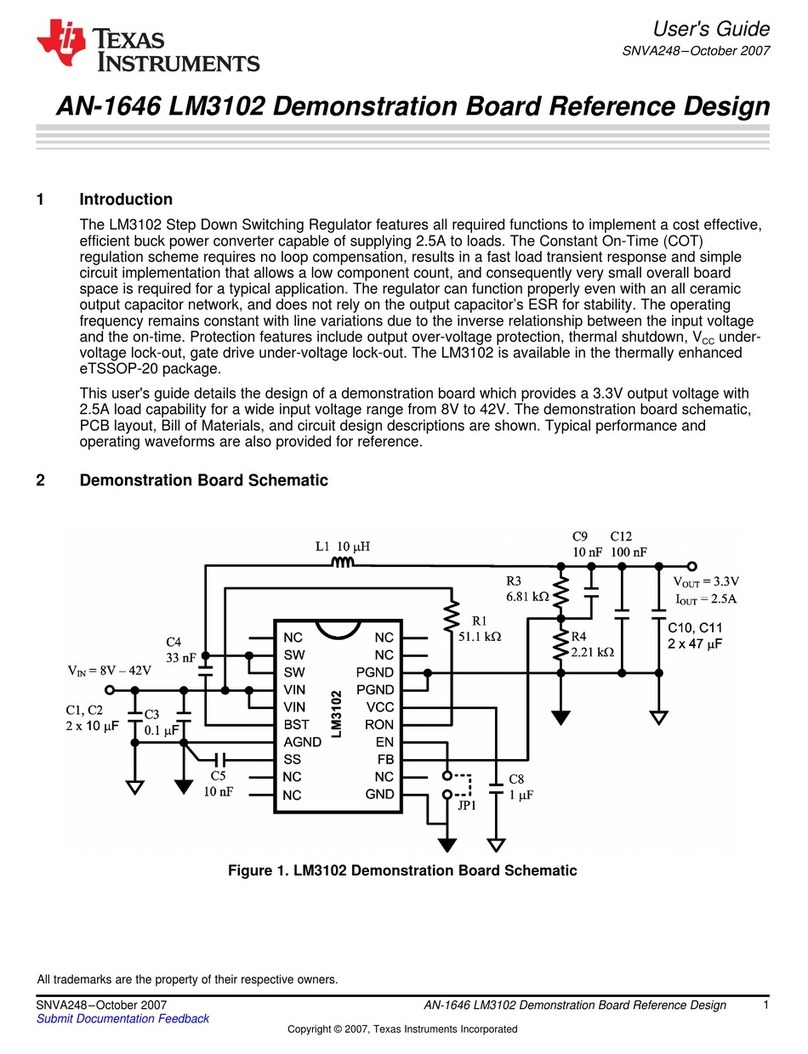

Texas Instruments AN-1646 User manual

Texas Instruments

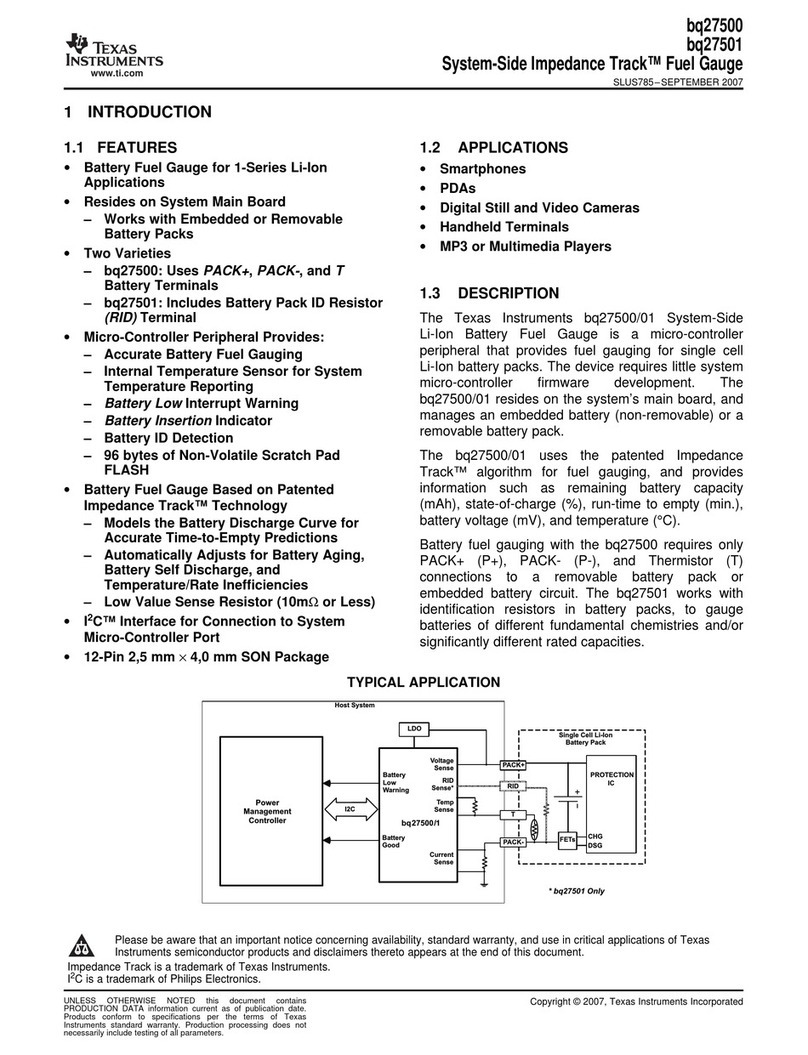

Texas Instruments System-Side Impedance Track bq27500 User manual

Texas Instruments

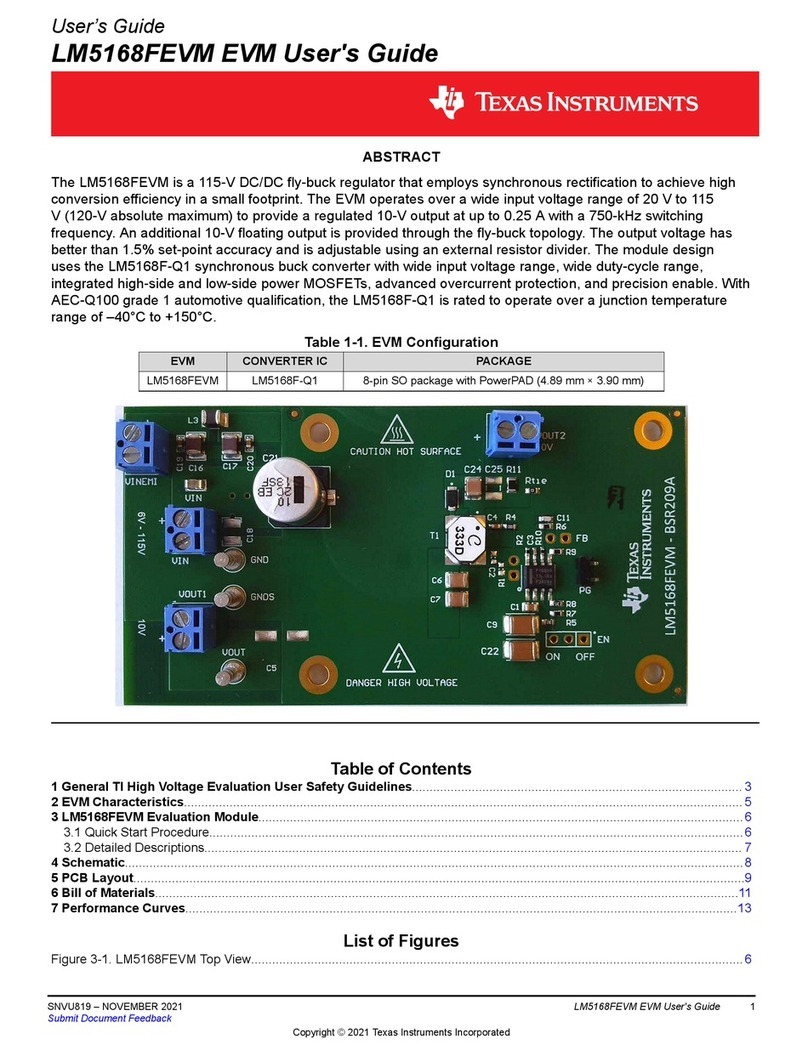

Texas Instruments LM5168FEVM User manual

Texas Instruments

Texas Instruments CC2545 User manual

Texas Instruments

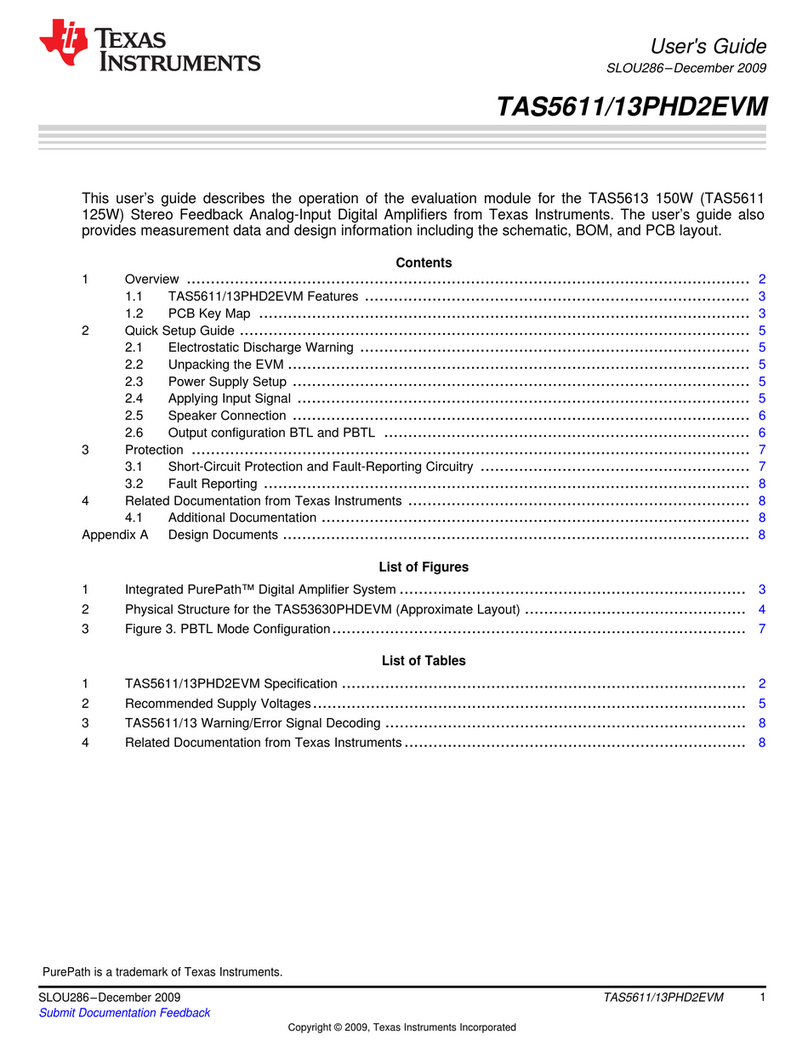

Texas Instruments TAS 5611/13PHD2EVM User manual

Texas Instruments

Texas Instruments TRIS TMS37122 User manual

Texas Instruments

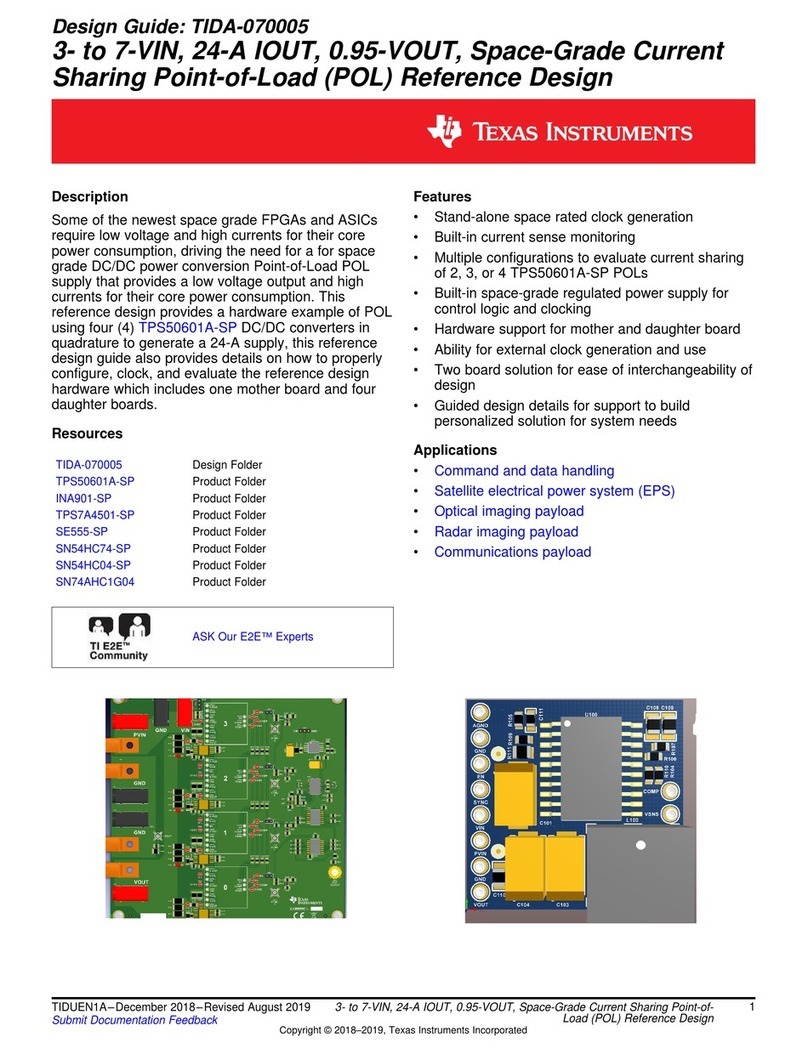

Texas Instruments tideP-0095 Guide

Texas Instruments

Texas Instruments XDS510 User manual

Texas Instruments

Texas Instruments MSP430x4xx Family User manual

Texas Instruments

Texas Instruments SimpleLink CC2640 User manual

Texas Instruments

Texas Instruments BoosterPack BOOSTXL-RS232 User manual

Texas Instruments

Texas Instruments TMDSCNCD28P65X Technical manual

Texas Instruments

Texas Instruments LM95172EVM User manual

Texas Instruments

Texas Instruments TVP5158 User manual

Popular Computer Hardware manuals by other brands

EMC2

EMC2 VNX Series Hardware Information Guide

Panasonic

Panasonic DV0PM20105 Operation manual

Mitsubishi Electric

Mitsubishi Electric Q81BD-J61BT11 user manual

Gigabyte

Gigabyte B660M DS3H AX DDR4 user manual

Raidon

Raidon iT2300 Quick installation guide

National Instruments

National Instruments PXI-8186 user manual