6 Power-Down, Mode and Format Control

7 Clock Source

7.1 Usage in PDK

7.2 Usage as a Stand-Alone EVM

Power-Down, Mode and Format Control

www.ti.com

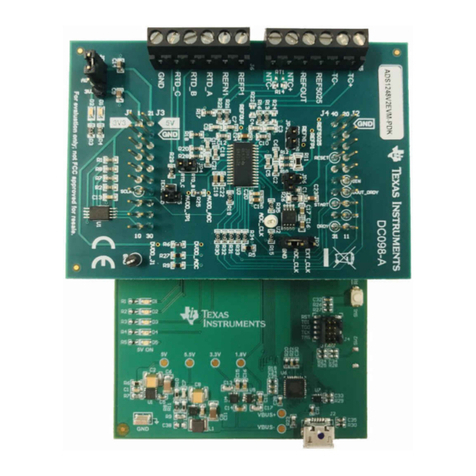

The ADS1274 has several pins to control power-down of individual channels, and mode and format for thedigital interface. These pins are controlled on the EVM either through software or hardware (usingswitches S10 and S11).

For users of the ADS1274EVM as a stand-alone module, these pins may be pulled high or low throughDIP switches S10 and S11. Refer to the ADS1274 product data sheet for complete details on these pinsand which state sets which options.

For use in the ADS1274EVM-PDK, the state of these pins is controlled by software, using the I

2

C portexpander on the EVM. When used in the ADS1274EVM-PDK, DIP switches S10 and S11 must all beswitched so that they are down, toward the center of the board. The ADS1274EVM-PDK software willcheck at startup to verify that these switches are set correctly, and will generate an error message if theyare not. However, it cannot detect if the switches are changed after startup.

CAUTION

When using the EVM as part of the ADS1274EVM-PDK, DIP switches S10 andS11 must all be switched so that they are down, toward the center of the board.Failure to do so may damage the EVM.

The ADS1274 clock can come from one of several sources: the onboard 27MHz crystal oscillator, a clocksupplied by a processor on the TOUT pin (J5.17), or an external clock source connected to J18.1 (ground)and J18.2 (signal).

If the onboard 27MHz oscillator is selected, the device can be run in the high-speed mode, thehigh-resolution mode, the low-power mode, or low-speed mode with CLKDIV set to 1. If the performanceof the device must be explored with CLKDIV set to 0 in the low-power and low-speed modes, an externalclock must be provided to the board, either using the TOUT connection or having an external clock sourceconnected to J18. The same is true if frequencies other than the 27MHz provided by the onboard oscillatormust be investigated.

If using the ADS1274EVM as part of the ADS1274EVM-PDK, J19 should not have any pins shorted.Remove any shorting blocks on jumper J19. The ADS1274EVM-PDK software will allow selection of theclock source under software control (this option is accomplished by using port 05 of the I

2

C expanderU17). The software allows selection of the onboard 27MHz oscillator, or a clock provided by a PLL on theMMB0 which directly drives the appropriate CLK pins of the interface, or an external, customer suppliedclock. If an external clock is selected with the software, this clock must be provided on J18. Note that if theexternal clock is selected and no clock is provided, the software may hang waiting for data from theconverter.

If using the EVM in your own system and not with the PDK hardware and software, observe the followingrecommendations:

•J17 should be removed if the external clock source is used and the TOUT pin is still driven by aprocessor in order to avoid conflicts.•Jumper J19 can be used to always select the 27MHz crystal (IOVDD position) or allow theonboard/external clock selection to be controlled by GPIO5 (J5.19) as shown in Figure 6 .

8ADS1174EVM, ADS1274EVM, ADS1174EVM-PDK, and ADS1274EVM-PDK SBAU134A – August 2008 – Revised May 2009Submit Documentation Feedback