Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 3

Copyright © 2013, Texas Instruments Incorporated

Table of Contents

TABLE OF CONTENTS ..............................................................................................................................................................3

GENERAL DESCRIPTION ..........................................................................................................................................................5

Evaluation Board Kit Contents..................................................................................................................5

Available LMK04906 Evaluation Boards .................................................................................................5

Available LMK04906 Family Devices......................................................................................................5

QUICK START ..........................................................................................................................................................................6

Default CodeLoader Modes for Evaluation Boards...................................................................................7

EXAMPLE: USING CODELOADER TO PROGRAM THE LMK04906B ............................................................................................8

1. Start CodeLoader 4 Application ............................................................................................................8

2. Select Device .........................................................................................................................................8

3. Program/Load Device............................................................................................................................9

4. Restoring a Default Mode......................................................................................................................9

5. Visual Confirmation of Frequency Lock.............................................................................................10

6. Enable Clock Outputs..........................................................................................................................10

PLL LOOP FILTERS AND LOOP PARAMETERS .........................................................................................................................12

PLL 1 Loop Filter ....................................................................................................................................12

25 MHz VCXO PLL............................................................................................................................12

PLL2 Loop Filter .....................................................................................................................................13

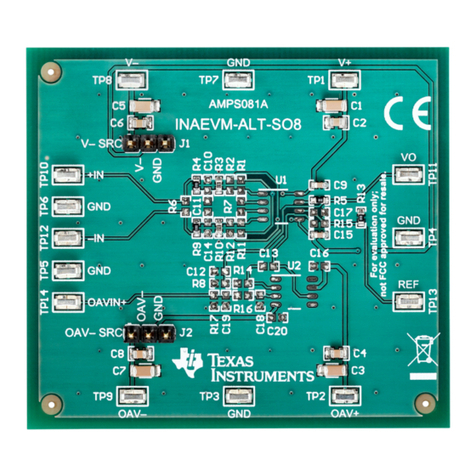

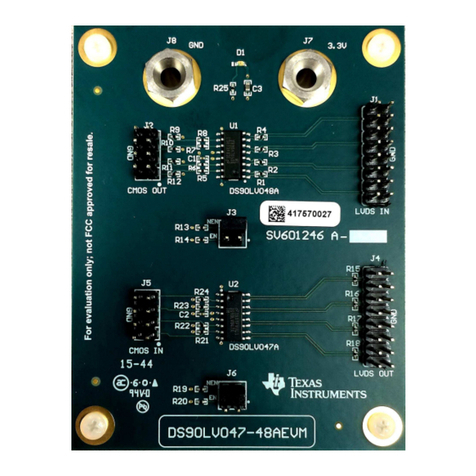

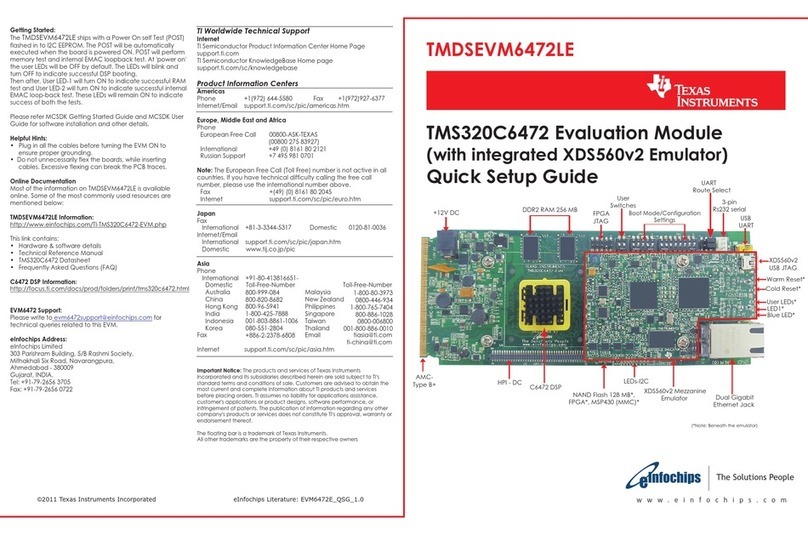

EVALUATION BOARD INPUTS AND OUTPUTS........................................................................................................................14

RECOMMENDED TEST EQUIPMENT ......................................................................................................................................21

APPENDIX A: CODELOADER USAGE.......................................................................................................................................22

Port Setup Tab..........................................................................................................................................22

Clock Outputs Tab...................................................................................................................................23

PLL1 Tab .................................................................................................................................................26

Setting the PLL1 VCO Frequency and PLL2 Reference Frequency...................................................27

PLL2 Tab .................................................................................................................................................28

Bits/Pins Tab............................................................................................................................................29

Registers Tab ...........................................................................................................................................34

APPENDIX B: TYPICAL PHASE NOISE PERFORMANCE PLOTS..................................................................................................35

PLL1 ........................................................................................................................................................35

25 MHz VCXO Phase Noise ...............................................................................................................35

Clock Output Measurement Technique...............................................................................................36

Clock Outputs (CLKout)..........................................................................................................................37