1General Information

1.1Features

n486DX4 at 100MHz or 5X86 at 133 MHz

n100% PC-AT Compatible

nUp to 32 Mbytes of user installable FPM or EDO DRAM

nOptional 256K L2 Cache

nSolid State Disk Support of up to 12MB

nPCI High-Resolution VGA controller for CRT or Flat Panel usage

nPCI IDE Controller

nNE2000 Compatible 10BaseT, AUI, Ethernet Controller

nFour 16550 Compatible Serial ports with optional RS422, RS485, J1708 interfaces

nBi-directional Parallel printer port supports EPP and ECP modes

n48 Digital I/O lines with 24 line event sense capability

nDual Floppy Disk interface

n16-Bit PC/104 Expansion Bus

nWatchdog Timer with Power-fail reset

1.2General Description

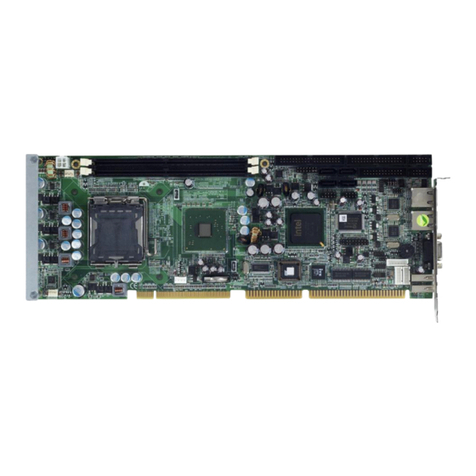

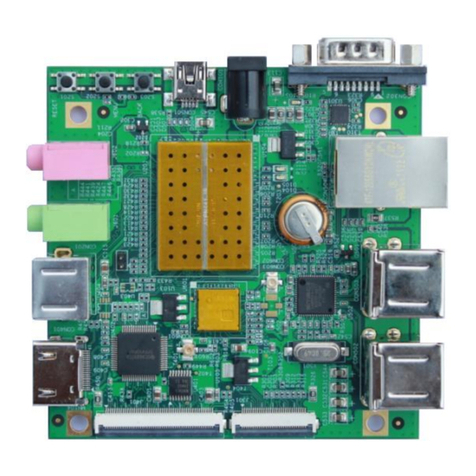

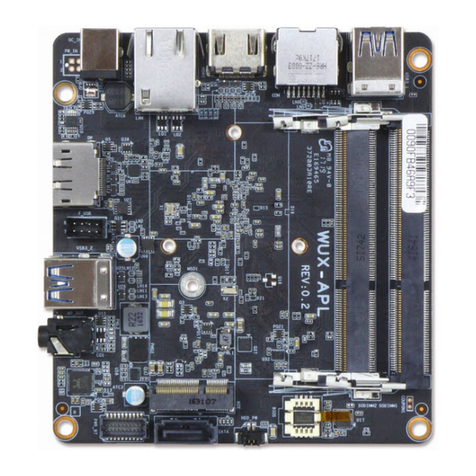

The LBC-486/586Plus is a small, high-performance, embeddable computer system on a single

board. It integrates a number of popular I/O options including VGA, Ethernet, Solid-State Disk, and

High-Density Parallel I/O. Four PC compatible serial ports are standard, as are the floppy,hard disk,

andparallelprinterinterfaces.TheLBC-Plusispopulated with either a 100 MHz AMD DX4proc essor

or the AMD 5x85 133 MHz processor. Up to 32Mbytes of user installable SIMM memory is sup-

ported. An optional 256KB level two cache is also available. A full 16-bit PC/104 expansion bus is

provided for further expansion to an entire industry of add-on peripherals including sound and speech

modules,SCSIcontrollers,Analog I/O modules, and literally hundreds of other optionsava ilable from

WinSystems and a variety of vendors supporting the PC/104 standard. An onboard silicon disk array

supportsdisksupto2megabytesinsizeandcanutilize SRAM, PEROM or EPROM as the disk media .

Boot capability is provided onboard and a set of utilities and drivers are provided to makethe silicon

disk based system very user friendly. Alternately, the M-Systems DiskOnChip FLASH modules ma y

be populated, supporting disk sizes ranging from 1 Megabyte to 12 Megabytes.

991206 OPERATIONS MANUAL LBC-PlusPage 1- 1